cy7c024v/025v/026v

cy7c0241v/0251v/036v

10

初步的

注释:

27. r/w

必须 是 高 在 所有 地址 transitions.

28. 一个 写 occurs 在 这 overlap (t

SCE

或者 t

PWE

) 的 一个 低 ce或者 sem和 一个 低 ub或者 lb.

29. t

HA

是 量过的 从 这 早期 的 ce或者 r/w或者 (sem或者 r/w) going 高 在 这 终止 的 写 循环.

30. 如果 oe

是 低 在 一个 r/w控制 写 循环, 这 写 脉冲波 宽度 必须 是 这 大 的 t

PWE

或者 (t

HZWE

+ t

SD

) 至 准许 这 i/o 驱动器 至 转变 止 和 数据 至 是 放置 在

这 总线 为 这 必需的 t

SD

. 如果 oe是 高 在 一个 r/w控制 写 循环, 这个 必要条件 做 不 应用 和 这 写 脉冲波 能 是 作 短的 作 这 指定 t

PWE

.

31. 至 进入 内存, ce

= v

IL

, sem= v

IH

.

32. 至 进入 upper 字节, ce

= v

IL

, ub= v

IL

, sem= v

IH

.

至 进入 更小的 字节, ce

= v

IL

, lb= v

IL

, sem= v

IH

.

33. 转变 是 量过的

±

500 mv 从 稳步的 状态 和 一个 5-pf 加载 (包含 scope 和 jig). 这个 参数 是 抽样 和 不 100% 测试.

34. 在 这个 时期, 这 i/o 管脚 是 在 这 输出 状态, 和 输入 信号 必须 不 是 应用.

35. 如果 这 ce

或者 sem低 转变 occurs 同时发生地 和 或者 之后 这 r/w低 转变, 这 输出 仍然是 在 这 高-阻抗 状态.

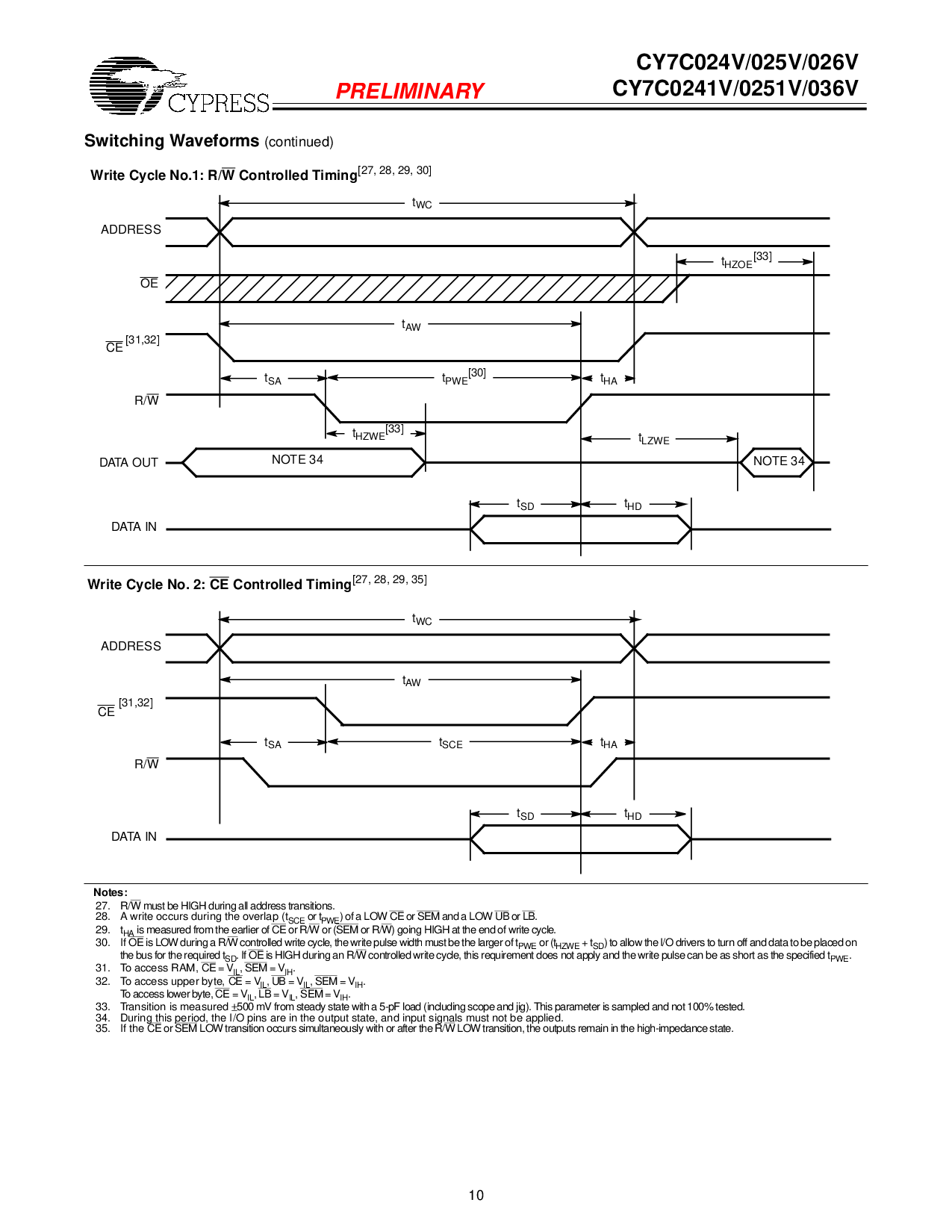

切换 波形

(持续)

t

AW

t

WC

t

PWE

t

HD

t

SD

t

HA

CE

r/w

OE

数据 输出

数据在

地址

t

HZOE

t

SA

t

HZWE

t

LZWE

写 循环 非.1: r/w控制 定时

[27, 28, 29, 30]

[33]

[33]

[30]

[31,32]

便条 34

便条 34

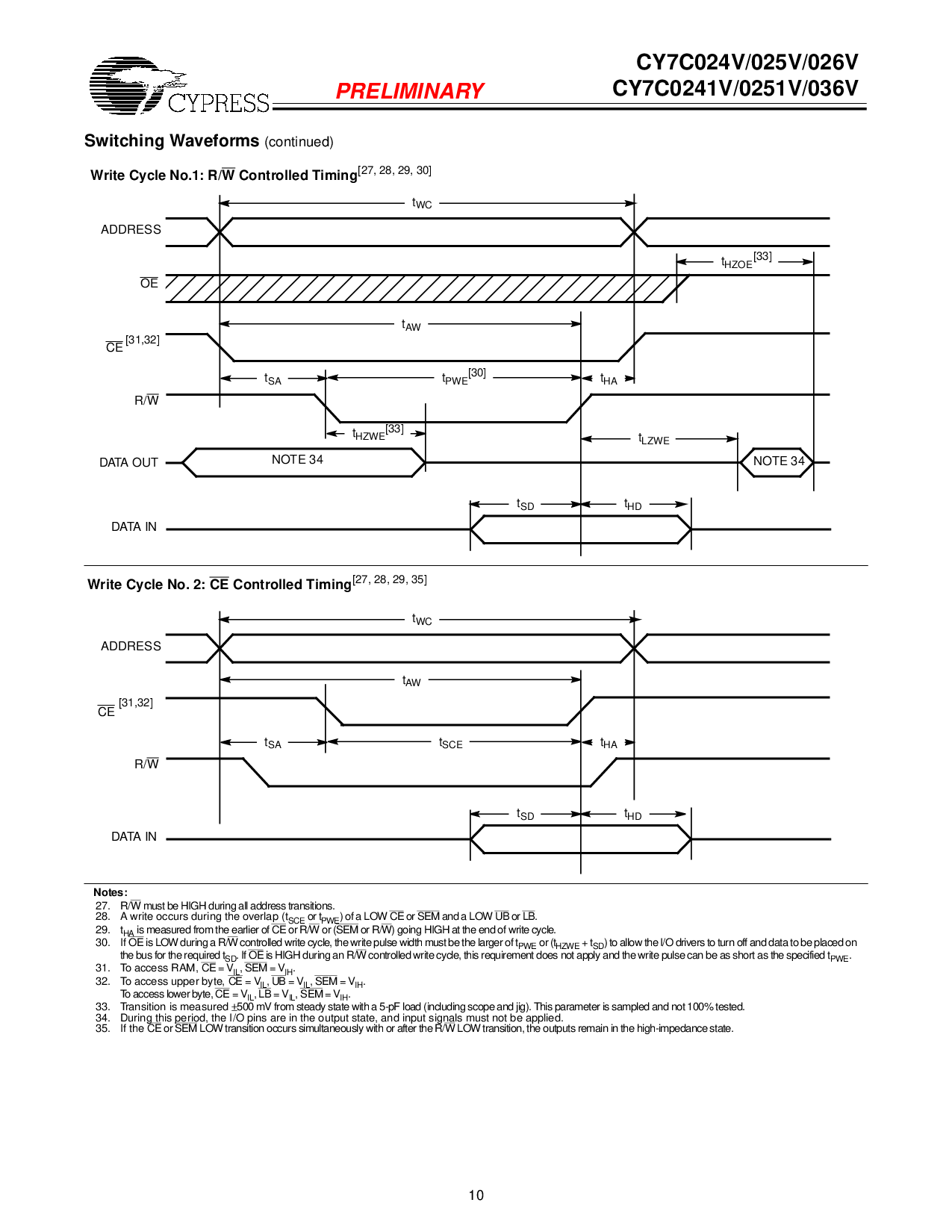

t

AW

t

WC

t

SCE

t

HD

t

SD

t

HA

CE

r/w

数据在

地址

t

SA

写 循环 非. 2: ce控制 定时

[27, 28, 29, 35]

[31,32]