max9153/max9154

低-jitter, 800mbps, 10-端口 lvds

repeaters 和 100

Ω

驱动

8 _______________________________________________________________________________________

产品 信息

供应 bypassing

绕过 各自 v

CC

和 高-频率 表面-挂载

陶瓷的 0.1µf 和 1nf 电容 在 并行的 作 关闭

至 这 设备 作 可能, 和 这 小 值 capac-

itor closest 至 这 v

CC

管脚.

查出, cables, 和 连接器

这 特性 的 输入 和 输出 连接

影响 这 效能 的 这 max9153/max9154. 使用

控制-阻抗 查出, cables, 和 连接器

和 matched 典型的 阻抗.

确保 那 噪音 couples 作 一般 模式 用 run-

ning 这 查出 的 一个 差别的 一双 关闭 一起.

减少 在里面-一双 skew 用 相一致 这 电的

长度 的 这 查出 的 一个 差别的 一双. 过度的

skew 能 结果 在 一个 降级 的 有磁性的 地方 能-

cellation. 维持 这 距离 在 查出 的 一个 dif-

ferential 一双 至 避免 discontinuities 在 差别的

阻抗. 降低 这 号码 的 vias 至 更远 前-

vent 阻抗 discontinuities.

避免 这 使用 的 不平衡 cables, 此类 作 ribbon

缆索. 保持平衡 cables, 此类 作 twisted 一双, 提供

更好的 信号 质量 和 tend 至 发生 较少 emi

预定的 至 canceling 影响. 保持平衡 cables tend 至 挑选

向上 噪音 作 一般 模式, 这个 是 rejected 用 这

lvds 接受者.

末端

这 max9153/max9154 是 指定 为 100

Ω

differ-

ential 典型的 阻抗 但是 能 运作 和

90

Ω

至 132

Ω

至 accommodate 各种各样的 类型 的 inter-

连接. 这 末端 电阻 应当 相一致 这 dif-

ferential 典型的 阻抗 的 这 interconnect

和 是 located 关闭 至 这 lvds 接受者 输入. 使用 一个

±1% 表面-挂载 末端 电阻.

这 输出 电压 摆动 是 决定 用 这 值 的 这

末端 电阻 multiplied 用 这 输出 电流. 和 一个

典型 3.8ma 输出 电流, 这 max9153/max9154 pro-

duce 一个 380mv 输出 电压 当 驱动 一个 传递

线条 terminated 和 一个 100

Ω

电阻 (3.8ma x 100

Ω

=

380mv).

碎片 信息

晶体管 计数:1394

处理: cmos

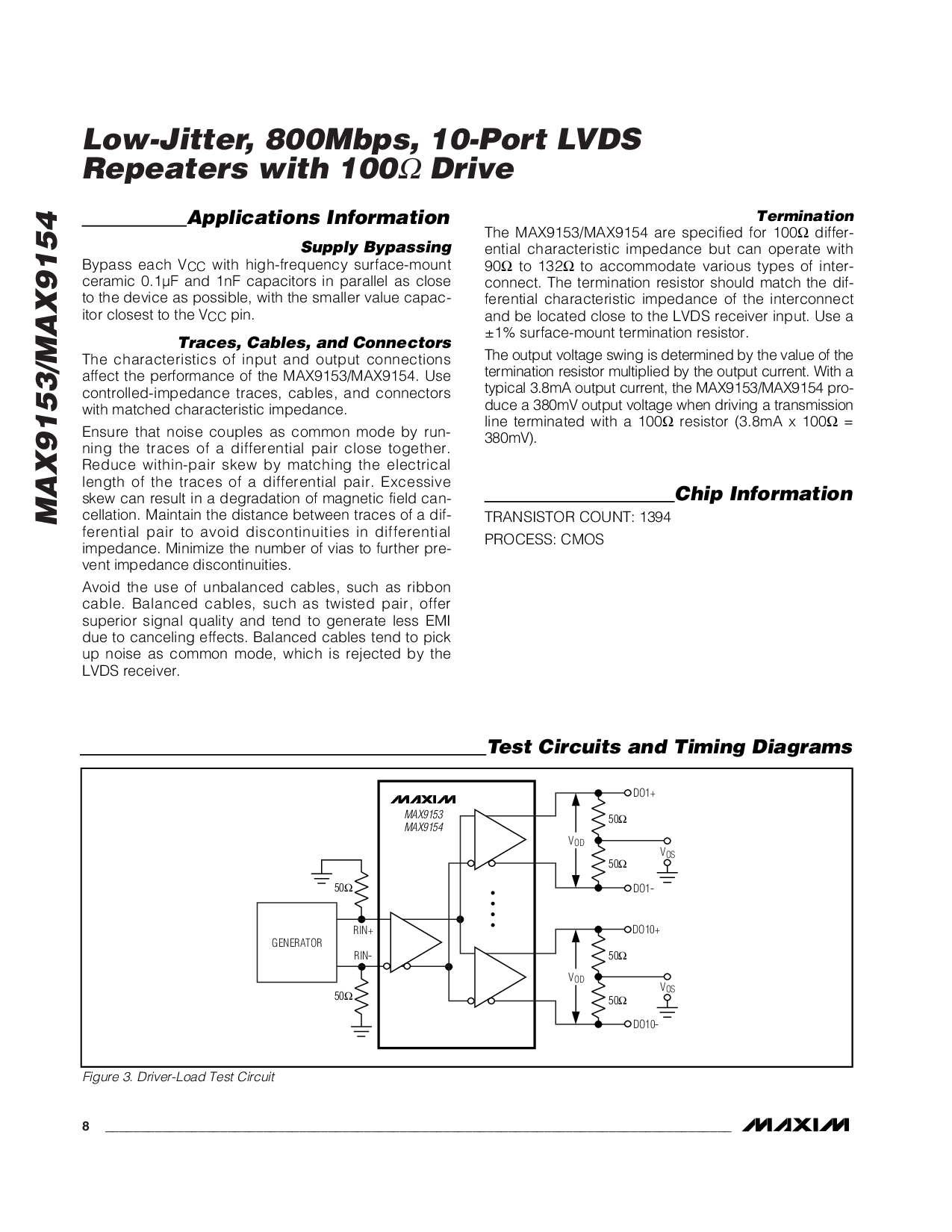

图示 3. 驱动器-加载 测试 电路

RIN+

rin-

发生器

50

Ω

50

Ω

MAX9153

MAX9154

DO1+

DO10+

do10-

do1-

V

OD

V

OS

50

Ω

50

Ω

50

Ω

50

Ω

V

OS

V

OD

测试 电路 和 定时 图解