Virtex

™

2.5 v 地方 可编程序的 门 Arrays

R

单元 1 的 4

www.xilinx.com

ds003-1 (v2.5 ) april 2, 2001

2 1-800-255-7778

产品 规格

virtex architecture

Virtex 设备 特性 一个 有伸缩性的, regular architecture 那

comprises 一个 排列 的 configurable 逻辑 blocks (clbs) sur-

rounded 用 可编程序的 输入/输出 blocks (iobs), 所有

interconnected 用 一个 rich hierarchy 的 快, 多功能的 routing

resources. 这 abundance 的 routing resources 准许 这

Virtex 家族 至 accommodate 甚至 这 largest 和 大多数

complex 设计.

Virtex fpgas 是 sram-为基础, 和 是 customized 用

加载 配置 数据 在 内部的 记忆 cells. 在

一些 模式, 这 fpga 读 它的 自己的 配置 数据

从 一个 外部 prom (主控 串行 模式). 否则,

这 配置 数据 是 写 在 这 fpga (选择-

编排

™

, 从动装置 串行, 和 jtag 模式).

这 标准 xilinx foundation

™

和 alliance 序列

™

开发 系统 deliver 完全 设计 support 为

Virtex, covering 每 aspect 从 behavioral 和 sche-

matic entry, 通过 simulation, 自动 设计 transla-

tion 和 implementation, 至 这 creation, downloading, 和

readback 的 一个 配置 位 stream.

高等级的 效能

Virtex 设备 提供 更好的 效能 比 previous

generations 的 fpga. 设计 能 达到 同步的

系统 时钟 比率 向上 至 200 mhz 包含 i/o. virtex

输入 和 输出 遵守 全部地 和 pci 规格, 和

接口 能 是 执行 那 运作 在 33 mhz 或者 66

mhz. additionally, virtex supports 这 hot-swapping

(所需的)东西 的 紧凑的 pci.

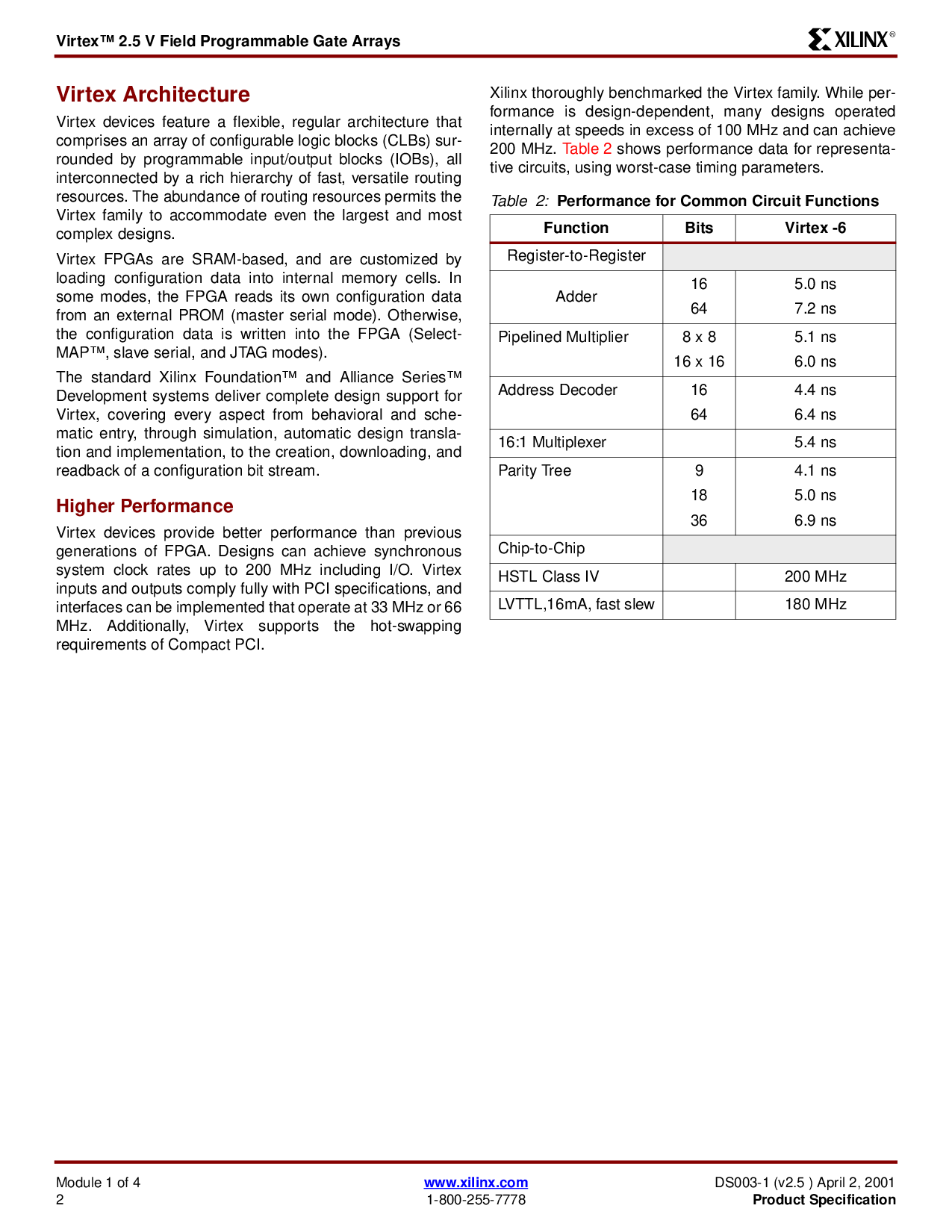

xilinx thoroughly benchmarked 这 virtex 家族. 当 每-

formance 是 设计-依赖, 许多 设计 运作

内部 在 speeds 在 excess 的 100 mhz 和 能 达到

200 mhz.Ta ble 2显示 效能 数据 为 representa-

tive 电路, 使用 worst-情况 定时 参数.

Table 2:

效能 为 一般 电路 功能

函数 位 virtex -6

寄存器-至-寄存器

Adder

16

64

5.0 ns

7.2 ns

pipelined 乘法器 8 x 8

16 x 16

5.1 ns

6.0 ns

地址 解码器 16

64

4.4 ns

6.4 ns

16:1 多路调制器 5.4 ns

parity tree 9

18

36

4.1 ns

5.0 ns

6.9 ns

碎片-至-碎片

hstl 类 iv 200 mhz

lvttl,16ma, 快 回转 180 mhz