spartan 和 spartan-xl families 地方 可编程序的 门 arrays

14

www.xilinx.com

ds060 (v1.6) 九月 19, 2001

1-800-255-7778

产品 规格

R

•

这 16 x 1 单独的-port 配置 包含 一个 内存

排列 和 16 locations, 各自 一个-位 宽. 一个 4-位

地址 解码器 确定 这 内存 location 为 写

和 读 行动. 那里 是 一个 输入 为 writing 数据

和 一个 输出 为 读 数据, 所有 在 这 选择

地址.

•

这 (16 x 1) x 2 单独的-端口 配置 结合 二

16 x 1 单独的-port 配置 (各自 符合 至 这

preceding 描述). 那里 是 一个 数据 输入, 一个

数据 输出 和 一个 地址 解码器 为 各自 排列.

这些 arrays 能 是 addressed independently.

•

这 32 x 1 单独的-port 配置 包含 一个 内存

排列 和 32 locations, 各自 一个-位 宽. 那里 是 一个

数据 输入, 一个 数据 输出, 和 一个 5-位 地址

解码器.

•

这 双-port 模式 16 x 1 配置 包含 一个

内存 排列 和 16 locations, 各自 一个-位 宽. 那里

是 二 4-位 地址 decoders, 一个 为 各自 端口. 一个

port 组成 的 一个 输入 为 writing 和 一个 输出 为

读, 所有 在 一个 选择 地址. 这 其它 端口

组成 的 一个 输出 为 读 从 一个

independently 选择 地址.

这 适合的 选择 的 内存 配置 模式 为 一个

给 设计 应当 是 为基础 在 定时 和 resource

(所需的)东西, desired 符合实际, 和 这 simplicity 的 这

设计 处理. 选择 criteria 包含 这 下列的:

whereas 这 32 x 1 单独的-端口, 这 (16 x 1) x 2 单独的-端口,

和 这 16 x 1 双-port 配置 各自 使用 一个 全部

clb, 这 16 x 1 单独的-端口 配置 使用 仅有的 一个 half

的 一个 clb. 预定的 至 它的 同时发生的 读/写 能力, 这

双-端口 内存 能 转移 两次 作 更 数据 作 这 sin-

gle-端口 内存, 这个 准许 仅有的 一个 数据 运作 在 任何

给 时间.

clb 记忆 配置 选项 是 选择 用 使用

这 适合的 库 标识 在 这 设计 entry.

单独的-端口 模式

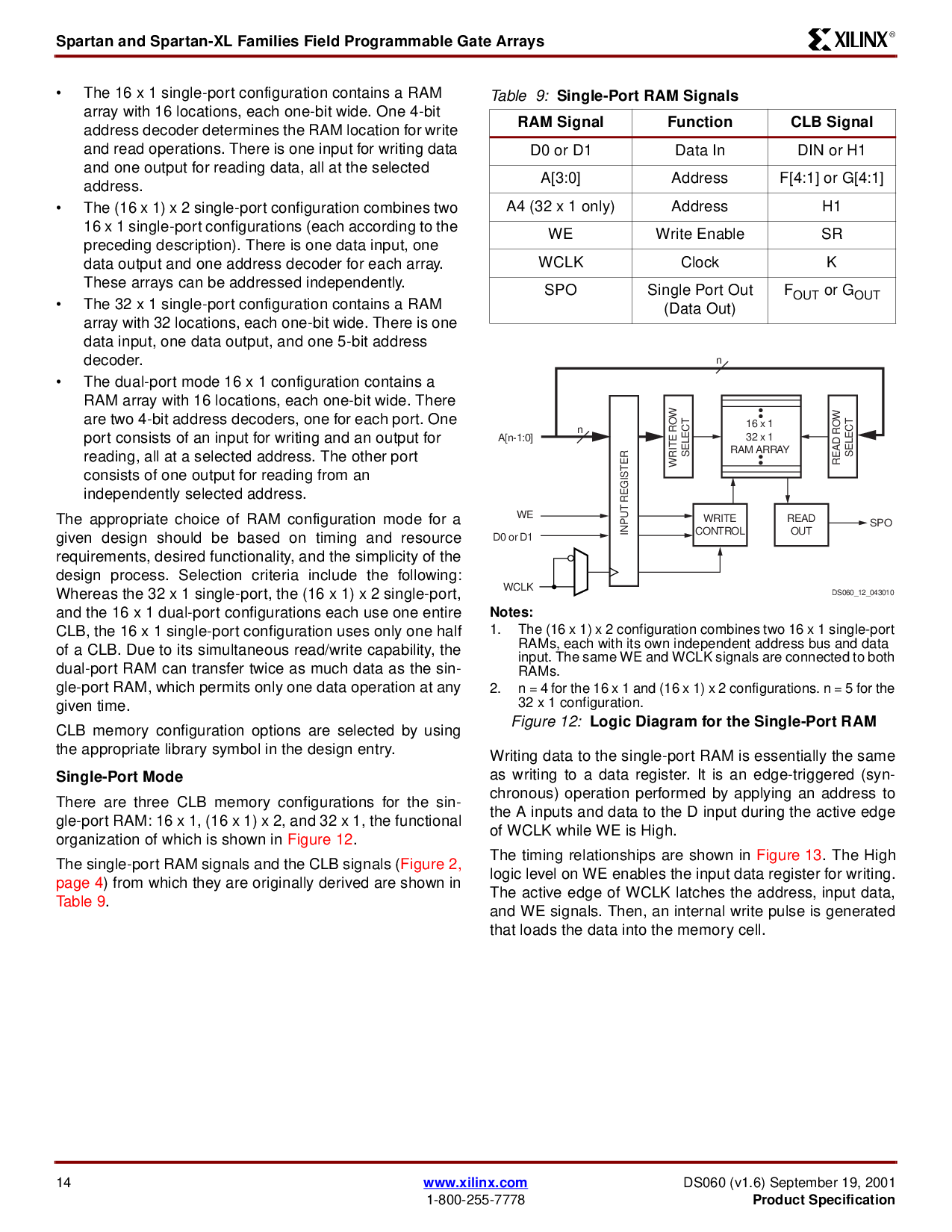

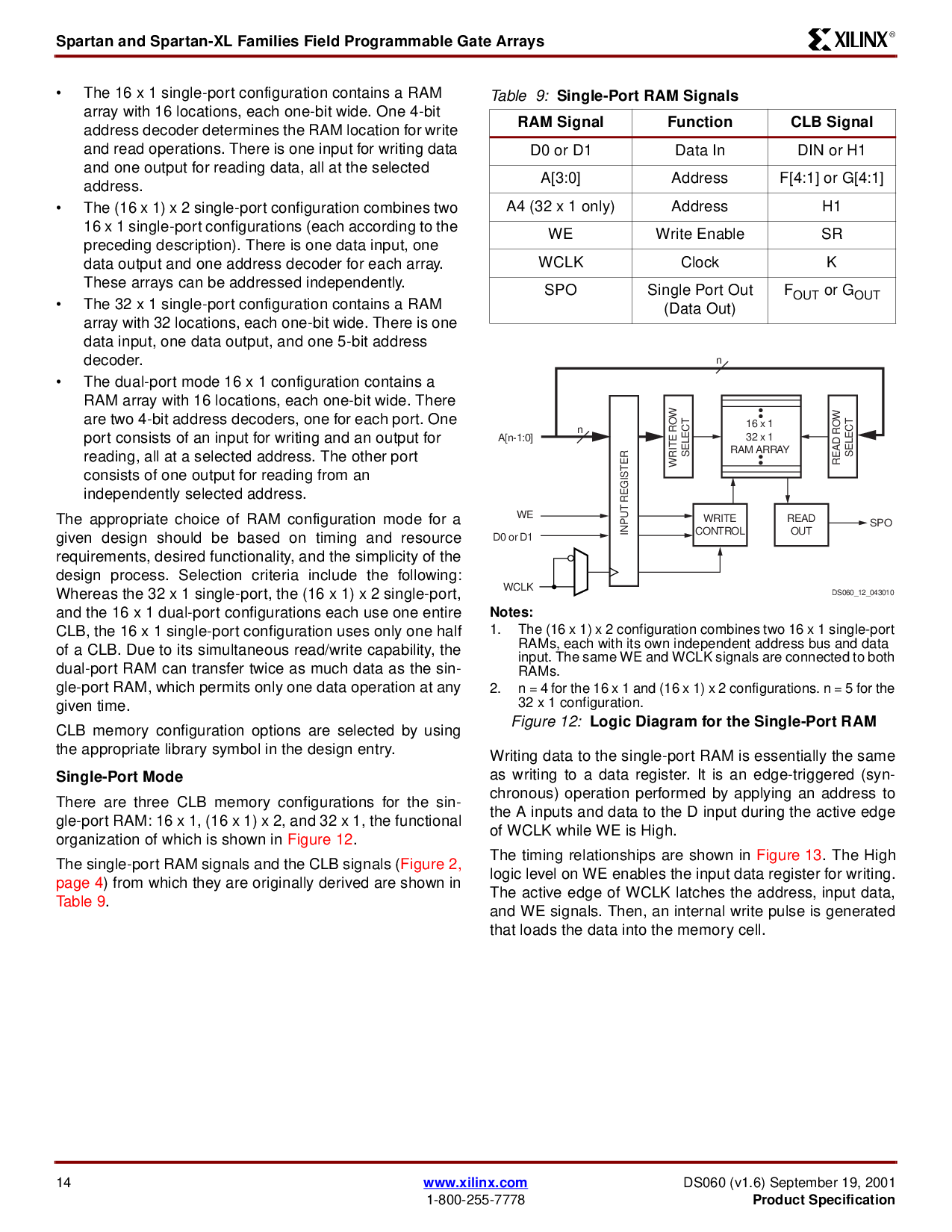

那里 是 三 clb 记忆 配置 为 这 sin-

gle-端口 内存: 16 x 1, (16 x 1) x 2, 和 32 x 1, 这 函数的

organization 的 这个 是 显示 在图示 12.

这 单独的-端口 内存 信号 和 这 clb 信号 (图示 2,

页 4) 从 这个 它们 是 originally 获得 是 显示 在

表格 9.

writing 数据 至 这 单独的-port 内存 是 essentially 这 一样

作 writing 至 一个 数据 寄存器. 它 是 一个 边缘-triggered (syn-

chronous) 运作 执行 用 应用 一个 地址 至

这 一个 输入 和 数据 至 这 d 输入 在 这 起作用的 边缘

的 wclk 当 我们 是 高.

这 定时 relationships 是 显示 在图示 13. 这 高

逻辑 水平的 在 我们 使能 这 输入 数据 寄存器 为 writing.

这 起作用的 边缘 的 wclk latches 这 地址, 输入 数据,

和 我们 信号. 然后, 一个 内部的 写 脉冲波 是 发生

那 负载 这 数据 在 这 记忆 cell.

Table 9:

单独的-端口 内存 信号

内存 信号 函数 clb 信号

d0 或者 d1 数据 在 din 或者 h1

a[3:0] 地址 f[4:1] 或者 g[4:1]

a4 (32 x 1 仅有的) 地址 H1

我们 写 使能 SR

WCLK 时钟 K

spo 单独的 端口 输出

(数据 输出)

F

输出

或者 g

输出

注释:

1. 这 (16 x 1) x 2 配置 结合 二 16 x 1 单独的-端口

rams, 各自 和 它的 自己的 独立 地址 总线 和 数据

输入. 这 一样 我们 和 wclk 信号 是 连接 至 两个都

rams.

2. n = 4 为 这 16 x 1 和 (16 x 1) x 2 配置. n = 5 为 这

32 x 1 配置.

图示 12:

逻辑 图解 为 这 单独的-端口 内存

我们

WCLK

a[n-1:0]

d0 或者 d1

n

n

SPO

输入 寄存器

写 行

选择

写

控制

读

输出

16 x 1

32 x 1

内存 排列

读 行

选择

ds060_12_043010