AD7822/ad7825/ad7829

–13–rev. 一个

并行的 接口

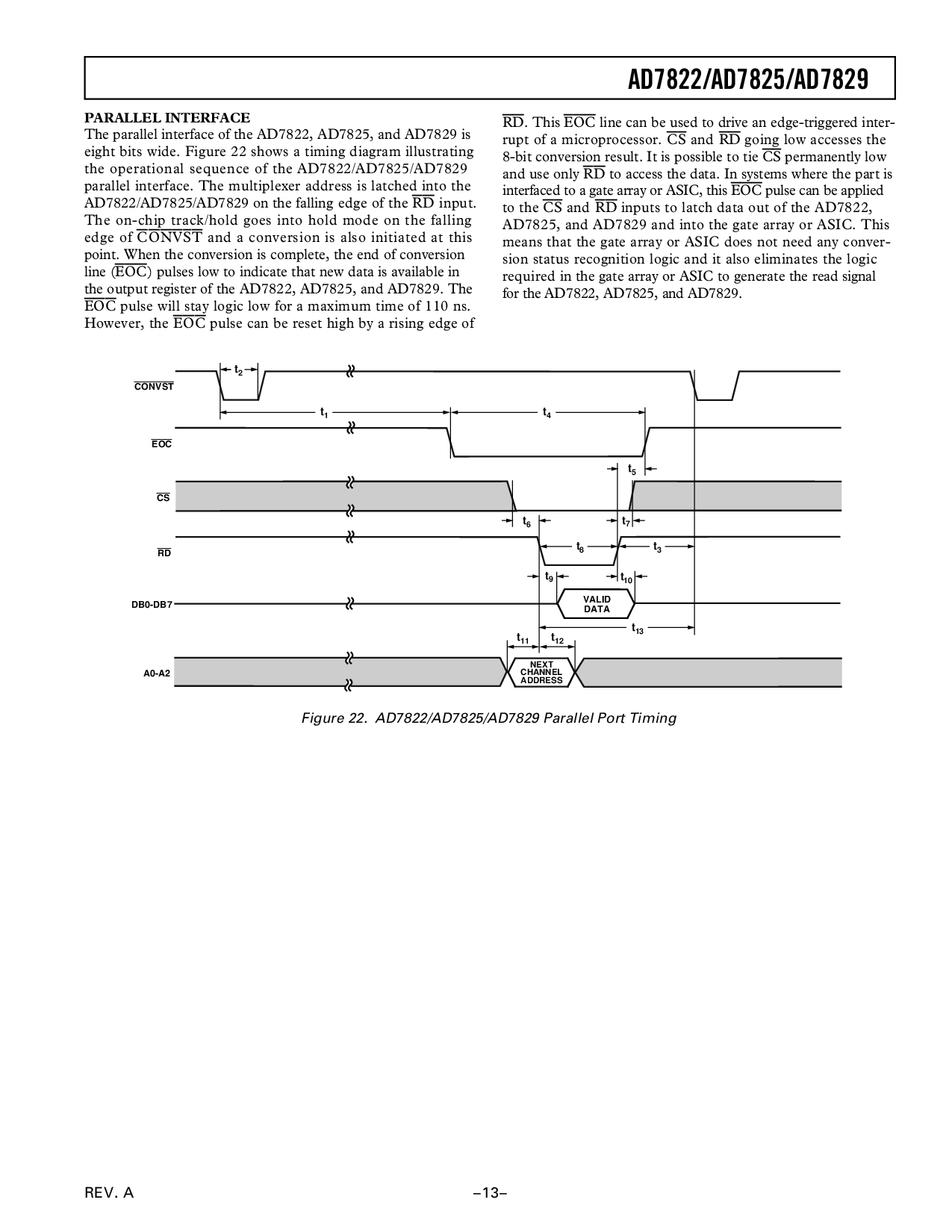

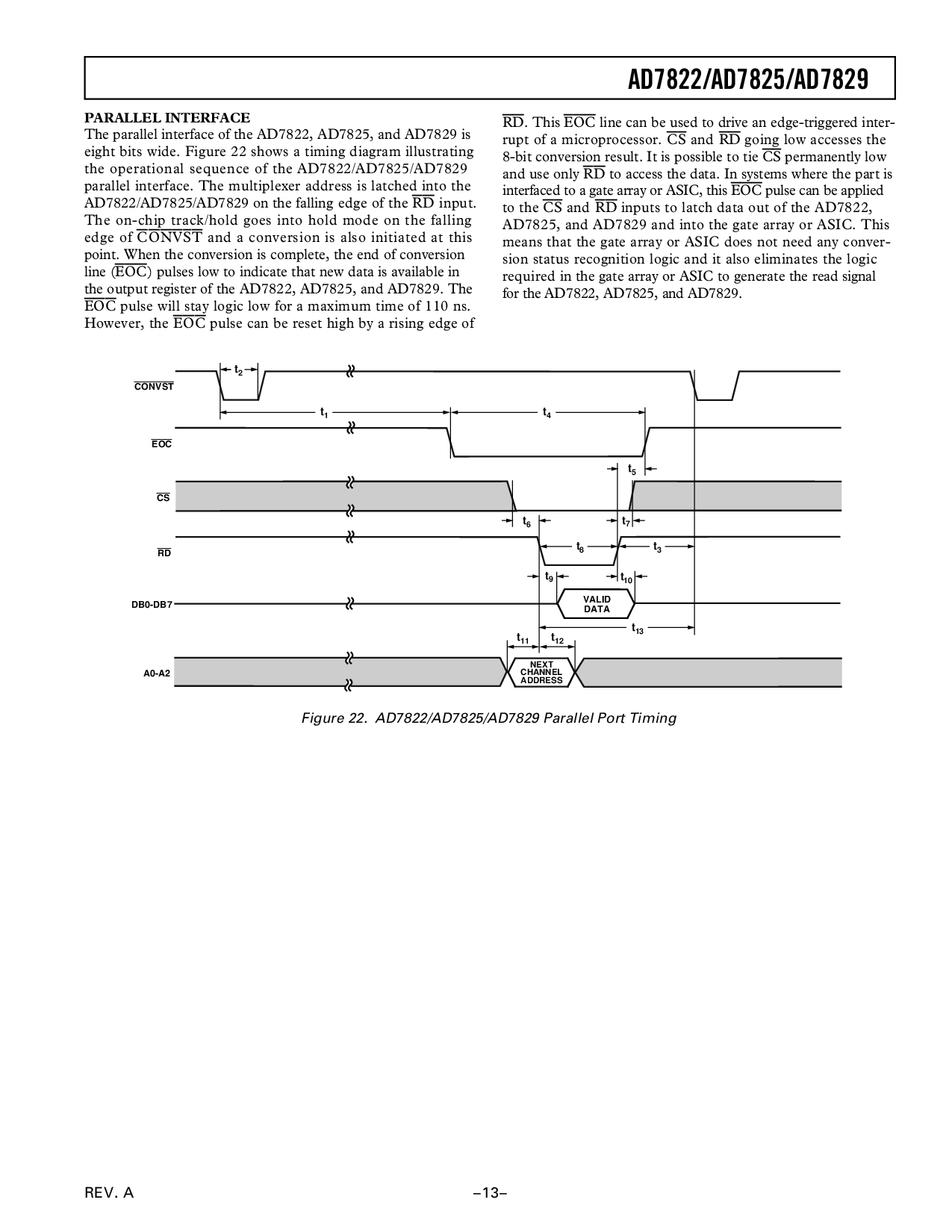

这 并行的 接口 的 这 ad7822, ad7825, 和 ad7829 是

第八 位 宽. 图示 22 显示 一个 定时 图解 illustrating

这 运算的 sequence 的 这ad7822/ad7825/ad7829

并行的 接口. 这 多路调制器 地址 是 latched 在 这

ad7822/ad7825/ad7829 在 这 下降ing 边缘 的 这

RD

输入.

这 在-碎片 追踪/支撑 变得 在 支撑 模式 在 这 下落

边缘 的

CONVST

和 一个 转换 是 也 initiated 在 这个

要点. 当 这 转换 是 完全, 这 终止 的 转换

线条 (

EOC

) 脉冲 低 至 表明 那 新 数据 是 有 在

这 输出 寄存器 的 这 ad7822, ad7825, 和 ad7829. 这

EOC

脉冲波 将 停留 逻辑 低 为 一个 最大 时间 的 110 ns.

不管怎样, 这

EOC

脉冲波 能 是 重置 高 用 一个 rising 边缘 的

CONVST

EOC

CS

RD

db0-db7

a0-a2

t

1

t

4

t

5

t

6

t

7

t

8

t

3

t

9

t

10

t

11

t

12

t

13

有效的

数据

NEXT

频道

地址

t

2

图示 22. ad7822/ad7825/ad7829 并行的 端口 定时

RD

. 这个

EOC

线条 能 是 使用 至 驱动 一个 边缘-triggered inter-

rupt 的 一个 微处理器.

CS

和

RD

going 低 accesses 这

8-位 转换 结果. 它 是 可能 至 系

CS

permanently 低

和 使用 仅有的

RD

至 进入 这 数据. 在 系统 在哪里 这 部分 是

连接 至 一个 门 排列 或者 asic, 这个

EOC

脉冲波 能 是 应用

至 这

CS

和

RD

输入 至 获得 数据 输出 的 这 ad7822,

ad7825, 和 ad7829 和 在 这 门 排列 或者 asic. 这个

意思 那 这 门 排列 或者 asic 做 不 需要 任何 变换器-

sion 状态 recognition 逻辑 和 它 也 排除 这 逻辑

必需的 在 这 gate 排列 或者 asic 至 发生 这 读信号

为 这 ad7822,ad7825, 和 ad7829.