AD1881A

–5–

rev. 0

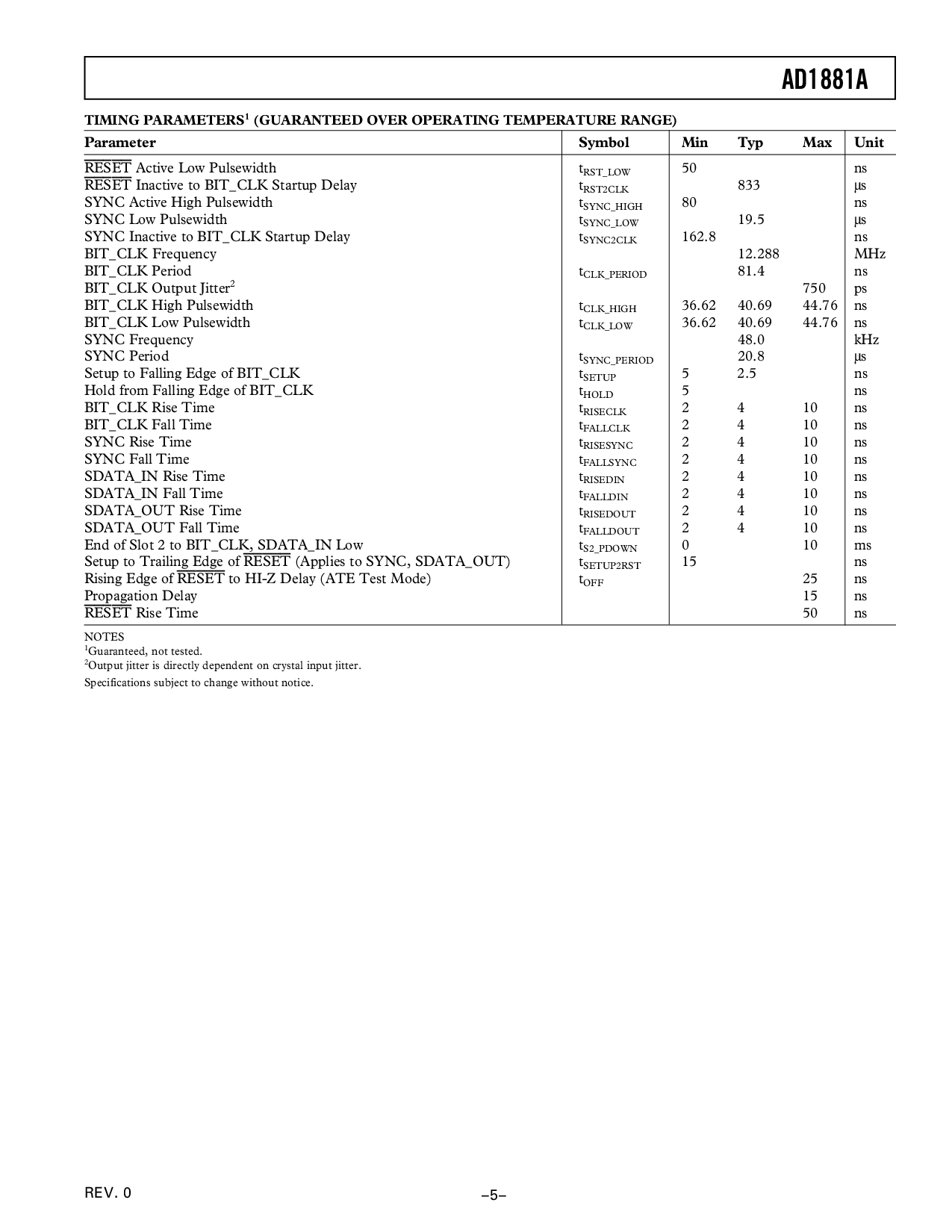

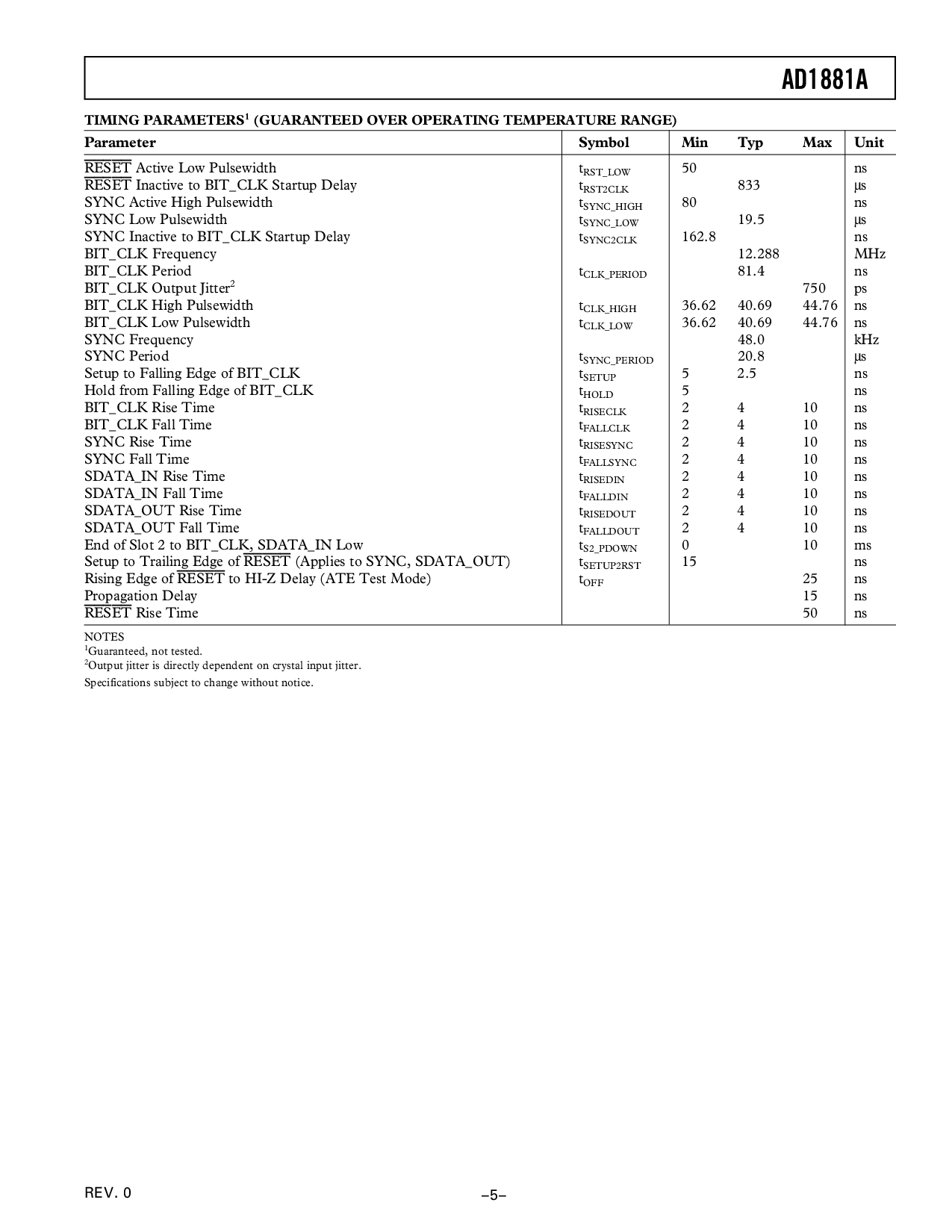

定时 参数

1

(有保证的 在 运行 温度 范围)

参数 标识 最小值 典型值 最大值 单位

重置

起作用的 低 pulsewidth t

rst_低

50 ns

重置

inactive 至 位_clk startup 延迟 t

RST2CLK

833

µ

s

同步 起作用的 高 pulsewidth t

同步_高

80 ns

同步 低 pulsewidth t

同步_低

19.5

µ

s

同步 inactive 至 位_clk startup 延迟 t

SYNC2CLK

162.8 ns

位_clk 频率 12.288 MHz

位_clk 时期 t

clk_时期

81.4 ns

位_clk 输出 jitter

2

750 ps

位_clk 高 pulsewidth t

clk_高

36.62 40.69 44.76 ns

位_clk 低 pulsewidth t

clk_低

36.62 40.69 44.76 ns

同步 频率 48.0 kHz

同步 时期 t

同步_时期

20.8

µ

s

建制 至 下落 边缘 的 位_clk t

建制

5 2.5 ns

支撑 从 下落 边缘 的 位_clk t

支撑

5ns

位_clk 上升 时间 t

RISECLK

24 10ns

位_clk 下降 时间 t

FALLCLK

24 10ns

同步 上升 时间 t

RISESYNC

24 10ns

同步 下降 时间 t

FALLSYNC

24 10ns

sdata_在 上升 时间 t

RISEDIN

24 10ns

sdata_在 下降 时间 t

FALLDIN

24 10ns

sdata_输出 上升 时间 t

RISEDOUT

24 10ns

sdata_输出 下降 时间 t

FALLDOUT

24 10ns

终止 的 slot 2 至 位_clk, sdata_在 低 t

s2_pdown

010ms

建制 至 trailing 边缘 的

重置

(应用 至 同步, sdata_输出) t

SETUP2RST

15 ns

rising 边缘 的

重置

至 hi-z 延迟 (ate 测试 模式) t

止

25 ns

传播 延迟 15 ns

重置

上升 时间 50 ns

注释

1

有保证的, 不 测试.

2

输出 jitter 是 直接地 依赖 在 结晶 输入 jitter.

规格 主题 至 改变 没有 注意.