CY7C53150

CY7C53120

文档 #: 38-10001 rev. *d 页 7 的 12

注释:

15. t

cyc

= 2(1/f), 在哪里 f 是 这 输入 时钟 (clk1) 频率 (20, 10, 5, 2.5, 1.25, 或者 0.625 mhz).

16. 谈及 至

图示 3

为 详细地 度量 信息.

17. 这 数据 支撑 参数, t

DHW

,

是 量过的 至 这 使不能运转 水平 显示 在

图示 5

, 相当 比 至 这 传统的 数据 invalid 水平.

18. 谈及 至

图示 6

和

图示 5

为 详细地 度量 信息.

19. 这 三-状态 情况 是 当 这 设备 是 不 actively 驱动 数据. 谈及 至

图示 2

和

图示 5

为 详细地 度量 信息.

20. 至 满足 这 定时 在之上 为 20-mhz 运作, 这 加载 在 a0–a15, d0–d7, 和 r/w

是 30 pf. 加载 在 e是 20 pf.

21. 一般 模式 电压 是 定义 作 这 平均 值 的 这 波形 在 各自 输入 在 这 时间 切换 occurs.

22. Z

0

= |v[cp2]-v[cp3] |/40ma 为 4.75 <V

DD

<5.25v.

外部 记忆 接口 定时 — cy7c53150, v

DD

±

10%

(v

DD

=4.5v 至 5.5 v, t

一个

= –40°c 至+ 85°c

[2]

)

参数 描述 最小值 最大值 单位

t

cyc

记忆 循环 时间 (系统 时钟 时期)

[15]

100 3200 ns

PW

EH

脉冲波 宽度, e高

[16]

t

cyc

/2 – 5 t

cyc

/2 + 5 ns

PW

EL

脉冲波 宽度, e 低

[16]

t

cyc

/2 – 5 t

cyc

/2 + 5 ns

t

AD

延迟, e高 至 地址 有效的

[20]

— 35 ns

t

AH

地址 支撑 时间 之后 e高

[20]

10 — ns

t

RD

延迟, e高 至 r/w有效的 读

[20]

— 25 ns

t

RH

r/w支撑 时间 读 之后 e高 5 — ns

t

WR

延迟, e高 至 r/w有效的 写 — 25 ns

t

WH

r/w支撑 时间 写 之后 e高 5 — ns

t

DSR

读 数据 建制 时间 至 e高 15 — ns

t

DHR

数据 支撑 时间 读 之后 e高 0 — ns

t

DHW

数据 支撑 时间 写 之后 e高

[17, 18]

10 — ns

t

DDW

延迟, e低 至 数据 有效的 — 12 ns

t

DHZ

数据 三 状态 支撑 时间 之后 e低

[19]

0 — ns

t

DDZ

延迟, e高 至 数据 三-状态

[18]

— 42 ns

t

acc

外部 记忆 进入 时间 (t

acc

= t

cyc

– t

AD

– t

DSR

) 在

20-mhz 输入 时钟

50 — ns

差别的 transceiver 电的 特性

典型的 最小值 最大值 单位

接受者 一般 模式 电压 范围 至 维持 hysteresis

[21]

1.2 V

DD

– 2.2 V

接受者 一般 模式 范围 至 运作 和 未说明的 hysteresis 0.9 V

DD

– 1.75 V

输入 补偿 电压 –0.05v

hys

– 35 0.05v

hys

+ 35 mV

传播 延迟 (f = 0, v

ID

= v

hys

/2 + 200 mv) — 230 ns ns

输入 阻抗 5 — M

Ω

wake-向上 时间 — 10

µ

s

差别的 输出 阻抗 为 cp2 和 cp3

[22]

35

Ω

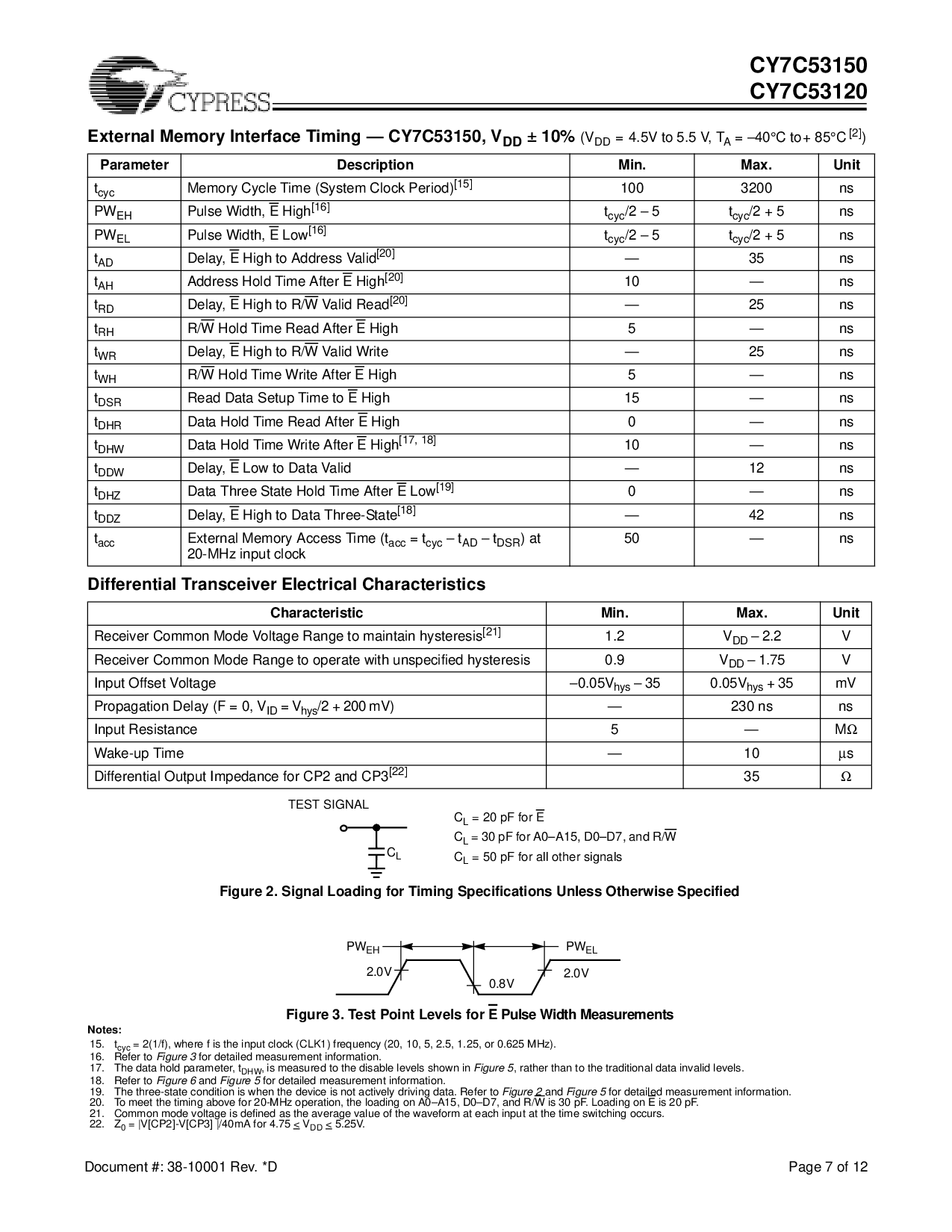

测试 信号

C

L

C

L

= 20 pf 为 e

C

L

= 30 pf 为 a0–a15, d0–d7, 和 r/w

C

L

= 50 pf 为 所有 其它 信号

图示 2. 信号 加载 为 定时 规格 除非 否则 指定

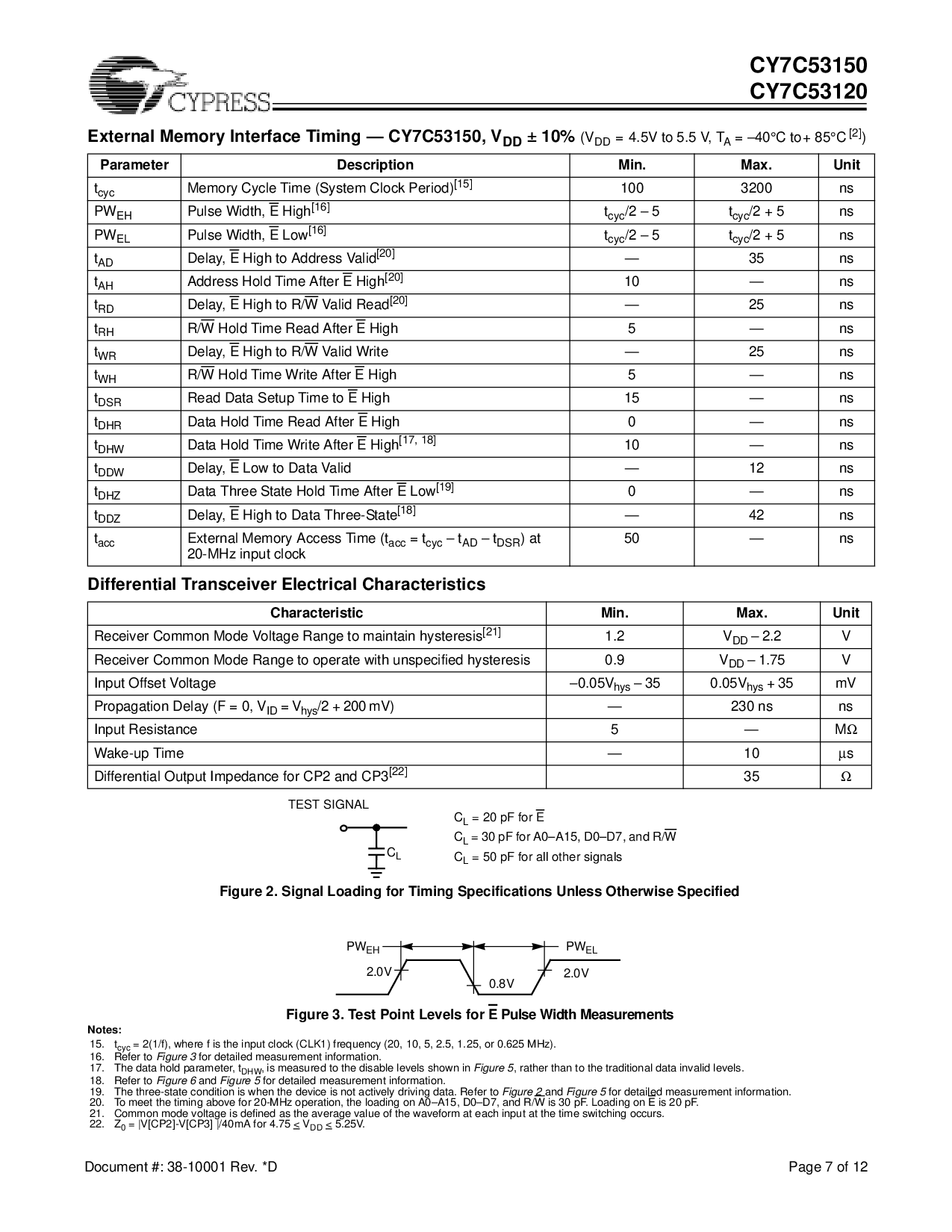

PW

EL

2.0v

PW

EH

2.0v

0.8v

图示 3. 测试 要点 水平 为 e脉冲波 宽度 度量