cy7c68013a/cy7c68014a

cy7c68015a/cy7c68016a

文档 #: 38-08032 rev. *g 页 7 的 55

3.9.2 wakeup 管脚

这 8051 puts 它自己 和 这 rest 的 这 碎片 在 一个 电源-向下

模式 用 设置 pcon.0 = 1. 这个 stops 这 振荡器 和

pll. 当 wakeup 是 asserted 用 外部 逻辑, 这 oscil-

lator restarts, 之后 这 pll stabilizes, 和 然后 这 8051

receives 一个 wakeup 中断. 这个 应用 whether 或者 不

fx2lp 是 连接 至 这 usb.

这 fx2lp exits 这 电源-向下 (usb suspend) 状态 使用

一个 的 这 下列的 方法:

• usb 总线 activity (如果 d+/d– 线条 是 left floating, 噪音 在

这些 线条 将 表明 activity 至 这 fx2lp 和 initiate 一个

wakeup).

• 外部 逻辑 asserts 这 wakeup 管脚

• 外部 逻辑 asserts 这 pa3/wu2 管脚.

这 第二 wakeup 管脚, wu2, 能 也 是 配置 作 一个

一般 目的 i/o 管脚. 这个 准许 一个 简单的 外部 r-c

网络 至 是 使用 作 一个 periodic wakeup 源. 便条 那

wakeup 是 用 default 起作用的 低.

3.10 程序/数据 内存

3.10.1 大小

这 fx2lp 有 16 kbytes 的 内部的 程序/数据 内存,

在哪里 psen#/rd# 信号 是 内部 ored 至 准许 这

8051 至 进入 它 作 两个都 程序 和 数据 记忆. 非 usb

控制 寄存器 呈现 在 这个 空间.

二 记忆 maps 是 显示 在 这 下列的 图解:

图示 3-3

内部的 代号 记忆, ea = 0

图示 3-4

外部 代号 记忆, ea = 1.

3.10.2 内部的 代号 记忆, ea = 0

这个 模式 实现 这 内部的 16-kbyte 块 的 内存

(开始 在 0) 作 联合的 代号 和 数据 记忆. 当

外部 内存 或者 只读存储器 是 增加, 这 外部 读 和 写

strobes 是 suppressed 为 记忆 spaces 那 exist inside

这 碎片. 这个 准许 这 用户 至 连接 一个 64-kbyte 记忆

没有 需要 地址 decodes 至 保持 clear 的 内部的

记忆 spaces.

仅有的 这

内部的

16 kbytes 和

scratch 垫子

0.5 kbytes 内存

spaces 有 这 下列的 进入:

• usb 下载

• usb upload

• 设置-向上 数据 pointer

•I

2

c 接口 激励 加载.

3.10.3 外部 代号 记忆, ea = 1

这 bottom 16 kbytes 的 程序 记忆 是 外部, 和

因此 这 bottom 16 kbytes 的 内部的 内存 是 accessible

仅有的 作 数据 记忆.

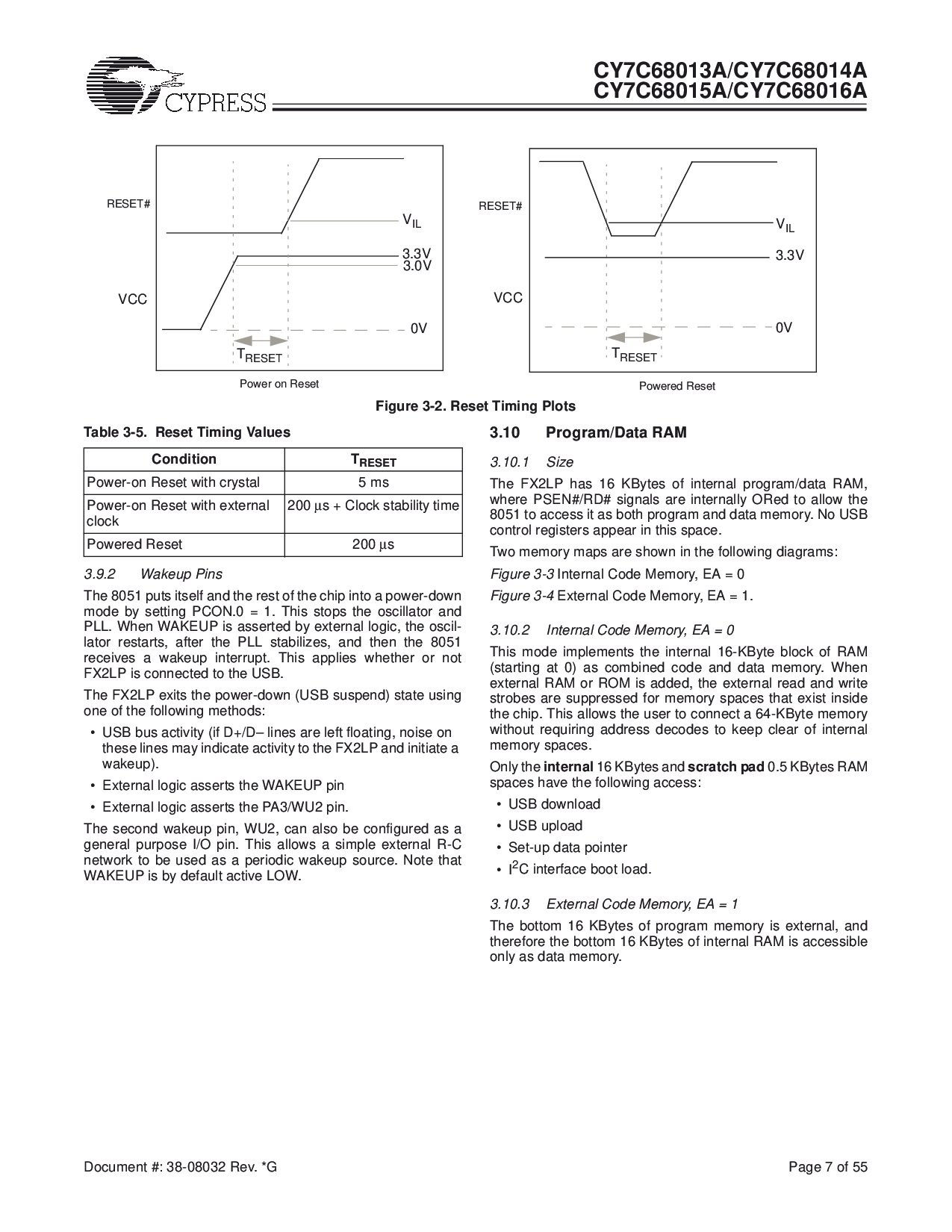

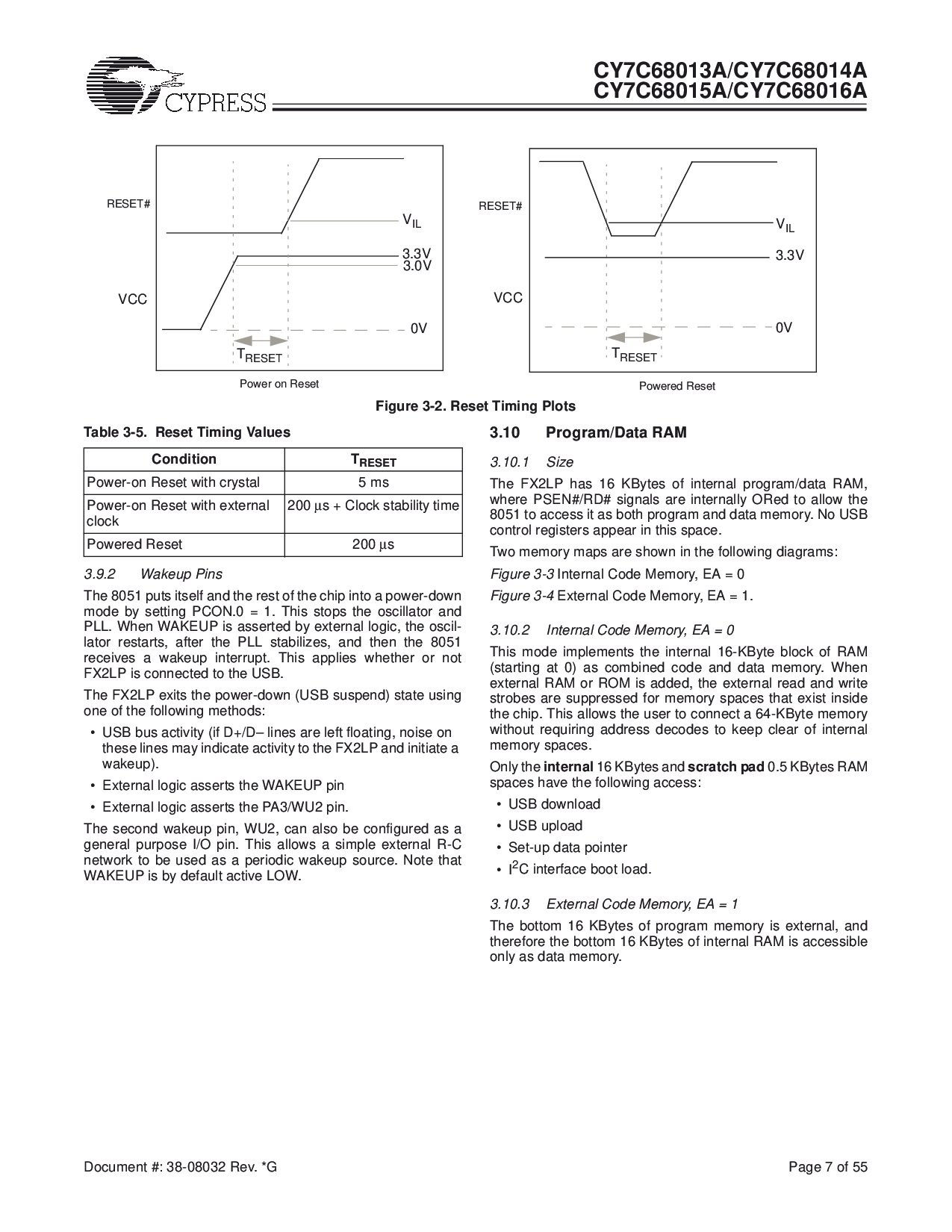

图示 3-2. 重置 定时 plots

V

IL

0V

3.3v

3.0v

T

重置

VCC

RESET#

电源 在 重置

T

重置

VCC

RESET#

V

IL

powered 重置

3.3v

0V

表格 3-5. 重置 定时 值

情况 T

重置

电源-在 重置 和 结晶 5 ms

电源-在 重置 和 外部

时钟

200

µ

s + 时钟 稳固 时间

powered 重置 200

µ

s