IC42S32200

IC42S32200L

整体的 电路 解决方案 公司

11

dr036-0d 02/04/2005

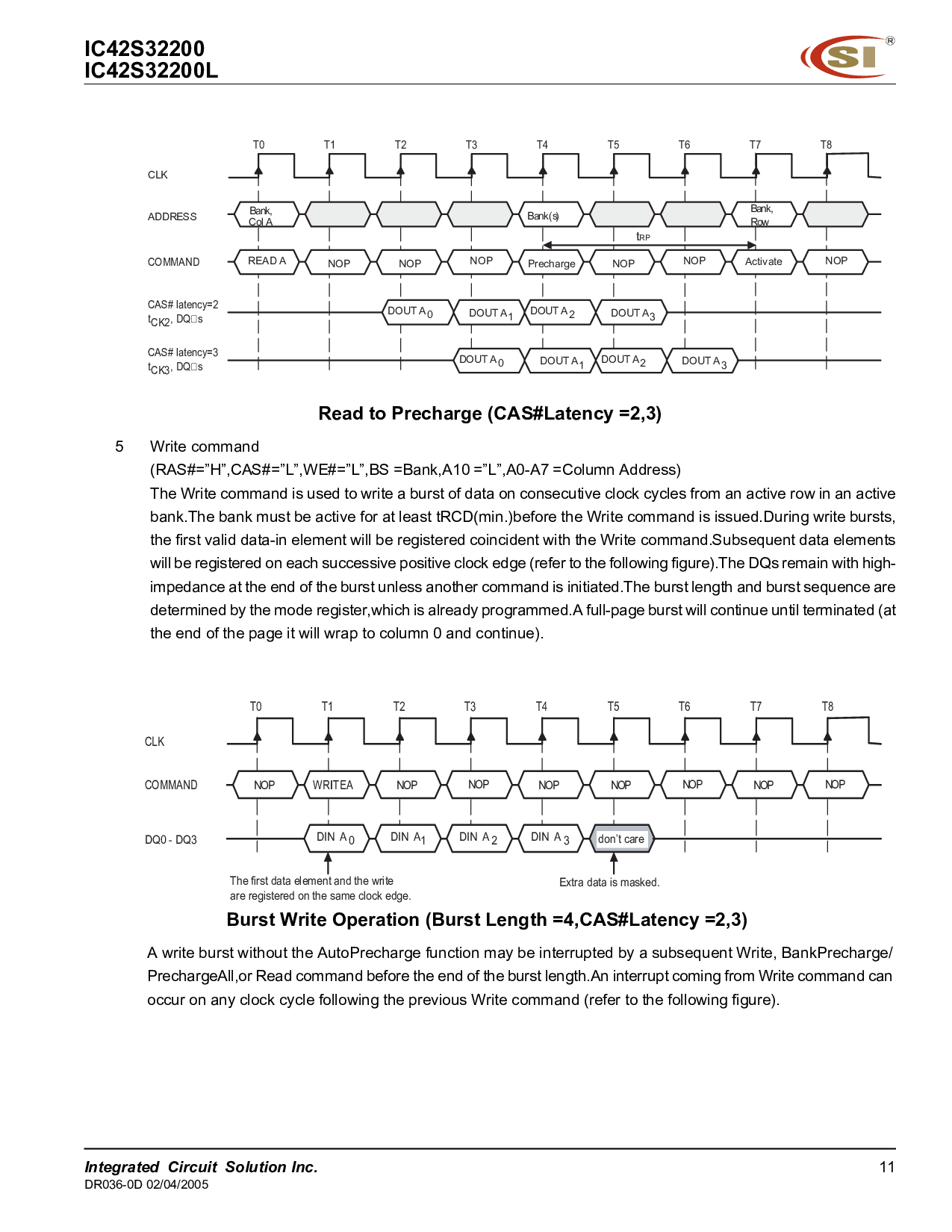

读 至 precharge (cas#latency =2,3)

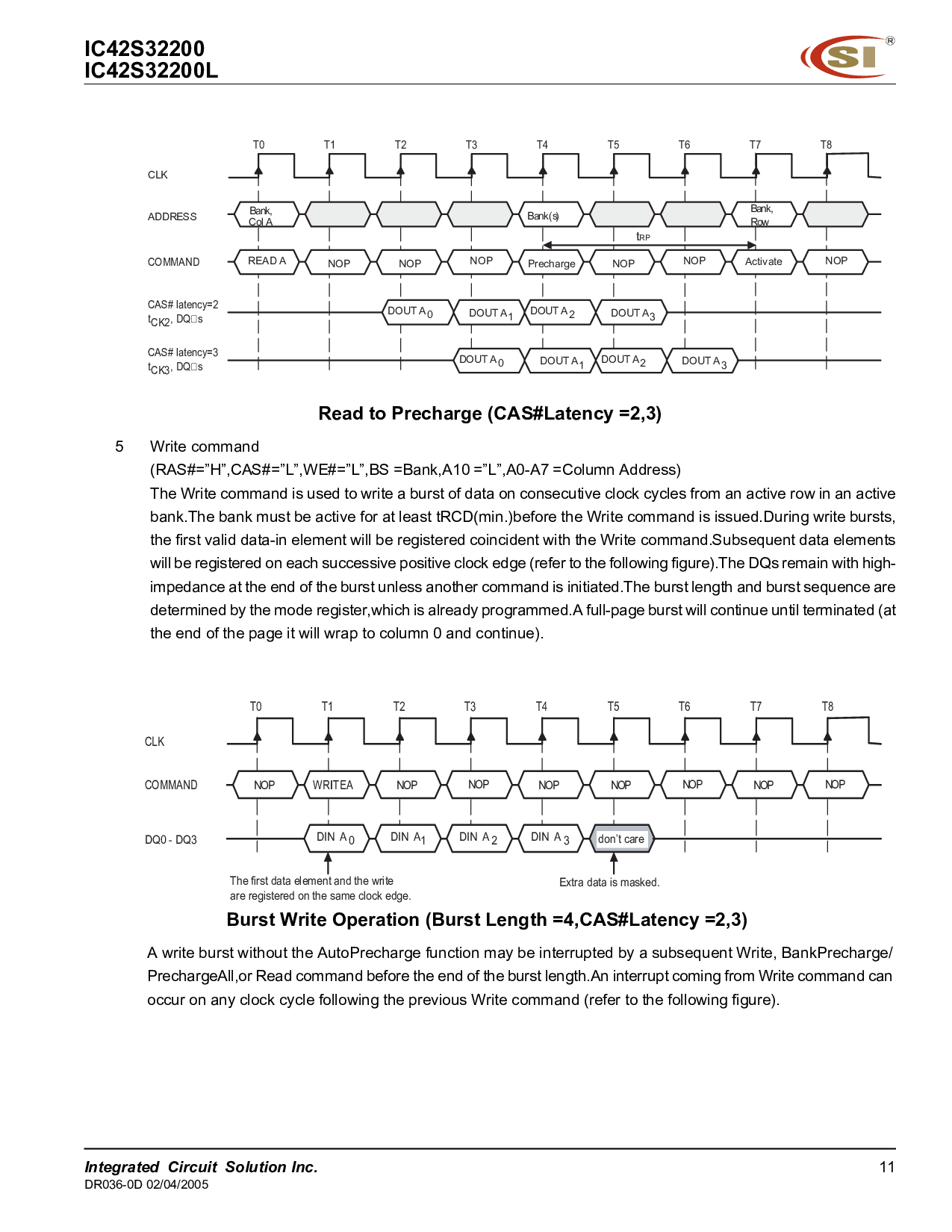

5 写 command

(ras#=”h”,cas#=”l”,we#=”l”,bs =bank,a10 =”l”,a0-a7 =column address)

这 写 command 是 使用 至 写 一个 burst 的 数据 在 consecutive 时钟 循环 从 一个 起作用的 行 在 一个 起作用的

bank.这 bank 必须 是 起作用的 为 在 least trcd(最小值.)在之前 这 写 command 是 issued.在 写 bursts,

这 第一 有效的 数据-在 元素 将 是 注册 coincident 和 这 写 command.subsequent 数据 elements

将 是 注册 在 各自 successive 积极的 时钟 边缘 (谈及 至 这 下列的 图示).这 dqs 仍然是 和 高-

阻抗 在 这 终止 的 这 burst 除非 另一 command 是 initiated.这 burst 长度 和 burst sequence 是

决定 用 这 模式 寄存器,这个 是 already 编写程序.一个 全部-页 burst 将 continue 直到 terminated (在

这 终止 的 这 页 它 将 wrap 至 column 0 和 continue).

CLK

COMMAND

读 一个

NOP

NOP

NOP

NOP

活动

NOP

NOP Precharge

dout 一个

0

dout 一个

1

dout 一个

2

dout 一个

3

dout 一个

0

dout 一个

1

dout 一个

2

dout 一个

3

地址

t

RP

bank,

col 一个

bank(s)

cas# latency=2

t

CK2

, dqs

cas# latency=3

t

CK3

, dqs

T0 T2T1 T3 T4 T5 T6 T7 T8

bank,

行

CLK

COMMAND

din 一个

3

NOP

WRITEA

I

NOP

NOP

NOP

NOP

NOP

NOP NOP

din 一个

0

din 一个

1

din 一个

2

dq0 - dq3

这 第一 数据 元素 和 这 写

是 注册 在 这 一样 时钟 边缘.

extra 数据 是 masked.

don’t小心

T0 T2T1 T3 T4 T5 T6 T7 T8

burst 写 运作 (burst 长度 =4,cas#latency =2,3)

一个 写 burst 没有 这 autoprecharge 函数 将 是 interrupted 用 一个 subsequent 写, bankprecharge/

prechargeall,或者 读 command 在之前 这 终止 的 这 burst 长度.一个 中断 coming 从 写 command 能

出现 在 任何 时钟 循环 下列的 这 previous 写 command (谈及 至 这 下列的 图示).