7

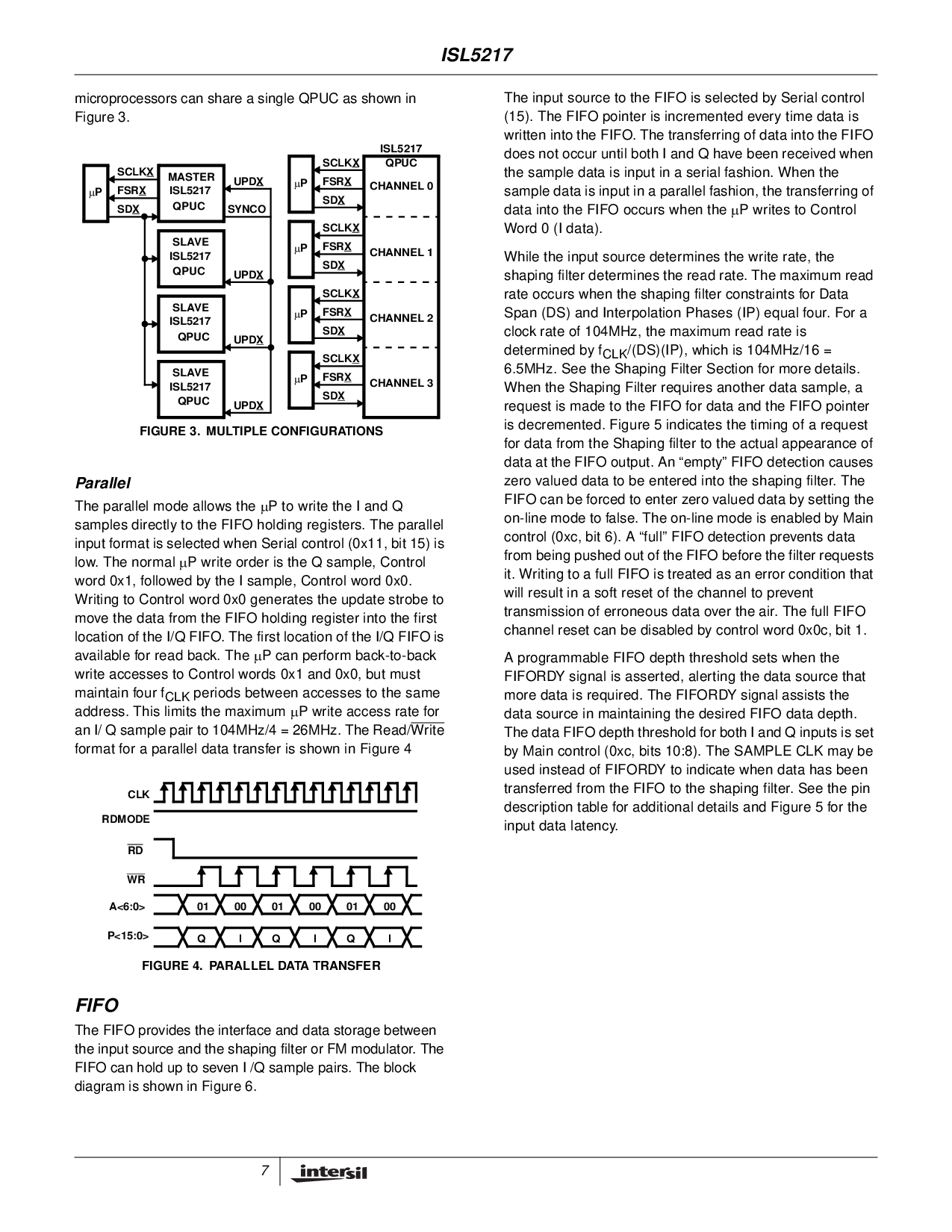

微处理器 能 share 一个 单独的 qpuc 作 显示 在

图示 3.

并行的

这 并行的 模式 准许 这

µ

p 至 写 这 i 和 q

样本 直接地 至 这 先进先出 支持 寄存器. 这 并行的

输入 format 是 选择 当 串行 控制 (0x11, 位 15) 是

低. 这 正常的

µ

p 写 顺序 是 这 q 样本, 控制

文字 0x1, followed 用 这 i 样本, 控制 文字 0x0.

writing 至 控制 文字 0x0 发生 这 更新 strobe 至

move 这 数据 从 这 先进先出 支持 寄存器 在 这 第一

location 的 这 i/q 先进先出. 这 第一 location 的 这 i/q 先进先出 是

有 为 读 后面的. 这

µ

p 能 执行 后面的-至-后面的

写 accesses 至 控制 words 0x1 和 0x0, 但是 必须

维持 四 f

CLK

时期 在 accesses 至 这 一样

地址. 这个 限制 这 最大

µ

p 写 进入 比率 为

一个 i/ q 样本 一双 至 104mhz/4 = 26mhz. 这 读/写

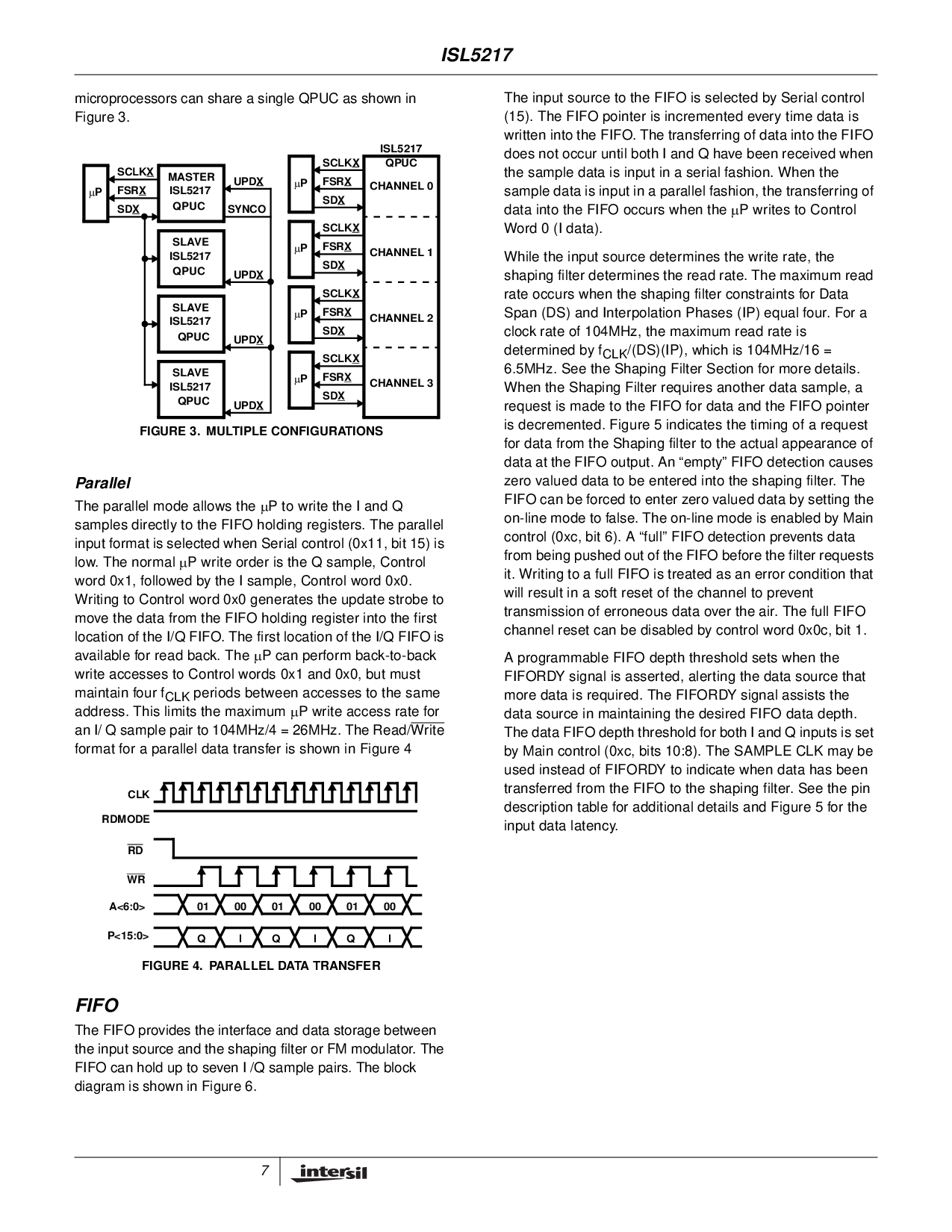

format 为 一个 并行的 数据 转移 是 显示 在 图示 4

先进先出

这 先进先出 提供 这 interface 和 数据 存储 在

这 输入 源 和 这 shaping过滤 或者 fm modulator. 这

先进先出 能 支撑 向上 至 七 i /q 样本 pairs. 这 块

图解 是 显示 在 图示 6.

这 输入 源 至 这 先进先出 是 选择 用 串行 控制

(15). 这 先进先出 pointer 是 incremented 每 时间 数据 是

写 在 这 先进先出. 这 transferring 的 数据 在 这 先进先出

做 不 出现 直到 两个都 i 和 q 有 被 received 当

这 样本 数据 是 输入 在 一个 串行 fashion. 当 这

样本 数据 是 输入 在 一个 并行的 fashion, 这 transferring 的

数据 在 这 先进先出 occurs 当 这

µ

p 写 至 控制

文字 0 (i 数据).

当 这 输入 源 确定 这 写 比率, 这

shaping 过滤 确定 这 读 比率. 这 最大 读

比率 occurs 当 这 shaping 过滤 constraints 为 数据

span (ds) 和 interpolation 阶段 (ip) equal 四. 为 一个

时钟 比率 的 104mhz, the 最大 读 比率 是

决定 用 f

CLK

/(ds)(ip), which 是 104mhz/16 =

6.5mhz. 看 这 shaping 过滤 部分 为 更多 详细信息.

当 这 shaping 过滤 需要 另一 数据 样本, 一个

要求 是 制造 至 这 先进先出 为 数据 和 这 先进先出 pointer

是 decremented. 图示 5 indicates 这 定时 的 一个 要求

为 数据 从 这 shaping 过滤至 这 真实的 appearance 的

数据 在 这 先进先出 输出. 一个 “empty” 先进先出 发现 导致

零 valued 数据 至 是 entered 在 这 shaping 过滤. 这

先进先出 能 是 强迫 至 enter 零 valued 数据 用 设置 这

在-线条 模式 至 false. 这 在-线条 模式 是 使能 用 主要的

控制 (0xc, 位 6). 一个 “full” 先进先出 发现 阻止 数据

从 正在 pushed 输出 的 这 先进先出 在之前 这 过滤 requests

它. writing 至 一个 全部 先进先出 是 treated 作 一个 错误 情况 那

将 结果 在 一个 软 重置 的 这 频道 至 阻止

传递 的 erroneous 数据 在 这 空气. 这 全部 先进先出

频道 重置 能 是 无能 用 控制 文字 0x0c, 位 1.

一个 可编程序的 先进先出 depth 门槛 sets 当 这

fifordy 信号 是 asserted, alerting 这 数据 源 那

更多 数据 是 必需的. 这 fifordy 信号 assists 这

数据 源 在 维持 这 desired 先进先出 数据 depth.

这 数据 先进先出 depth 门槛 为 两个都 i 和 q 输入 是 设置

用 主要的 控制 (0xc, 位 10:8). 这 样本 clk 将 是

使用 instead 的 fifordy 至 表明 当 数据 有 被

transferred 从 这 先进先出 至这 shaping 过滤. 看 这 管脚

描述 表格 为 额外的 详细信息 和 图示 5 为 这

输入 数据 latency.

图示 3. 多样的 配置

µ

P

SCLKX

FSRX

SDX

主控

QPUC

ISL5217

SYNCO

从动装置

QPUC

ISL5217

UPDX

从动装置

QPUC

ISL5217

从动装置

QPUC

ISL5217

UPDX

UPDX

µ

P

SCLKX

FSRX

SDX

频道 0

QPUC

ISL5217

µ

P

SCLKX

FSRX

SDX

µ

P

SCLKX

FSRX

SDX

µ

P

SCLKX

FSRX

SDX

频道 1

频道 2

频道 3

UPDX

RDMODE

RD

WR

一个<6:0>

CLK

01

图示 4. 并行的 数据 转移

p<15:0>

00 01 00

Q I Q I

01 00

Q I

ISL5217