_______________________________________________________________________________________ 9

__________产品 信息

乘以 运作

这 max547 能 是 使用 为 乘以 产品.

它的 涉及 accepts 两个都 直流 和 交流 信号. 这 volt-

age 在 各自 ref_ 输入 sets 这 全部-规模 输出 电压

为 它的 各自的 dacs. 自从 这 涉及 输入

接受 仅有的 积极的 电压, 乘以 运作 是

限制 至 二 quadrants. 做 不 绕过 这 涉及

输入 当 应用 交流 信号 至 它们. 谈及 至 这

graphs 在 这

典型 运行 特性

为

动态 效能 的 这 dacs 和 输出 缓存区.

数字的 代号 和 相似物 输出 电压

这 max547 使用 补偿 二进制的 编码. 一个 13-位 twos-

complement 代号 能 是 转变 至 一个 13-位 补偿

二进制的 代号 用 adding 2

12

= 4096.

双极 输出 电压 范围 (agnd_ = 0v)

为 对称的 双极 运作, 系 agnd_ 至 这

系统 地面. 表格 3 显示 这 relationship 在

数字的 代号 和 输出 电压. 这 下列的 para-

graphs 给 一个 详细地 explanation 的 这个 模式.

这 dac ladder 输出 电压 (v

DAC

) 是 multiplied 用

2 和 水平的 shifted 用 这 涉及 电压, 这个 是

内部 连接 至 这 输出 放大器 (图示 1).

自从 这 反馈 电阻器 是 这 一样 大小, 这

放大器’s 输出 电压 是 2 时间 这 电压 在 它的

同相 输入, minus 这 涉及 电压.

在哪里 v

DAC

是 这 电压 在 这 放大器’s noninvert-

ing 输入 (dac ladder 输出 电压), 和 ref_ 是 这

电压 应用 至 这 涉及 输入 的 这 dac.

和 agnd_ 连接 至 这 系统 地面, 这 dac

ladder 输出 电压 是:

在哪里 d 是 这 numeric 值 的 这 dac’s 二进制的 输入

代号 和 n 是 这 dac’s 决议 (13 位). 替代

V

DAC

在 这 等式 和 计算 这 输出 电压.

d 范围 从 0 (2

0

) 至 8191 (2

13

- 1).

1LSB REF

–

1

4096

=

vout_ 2

D

2

REF

–

REF

–

= REF

–

D

2

– 1 REF

–

D

4096

–1

13

12

=

()

−

=

V

D

2

(ref

–

)

D

2

(ref

–

)

DAC

n13

==

vout 2(v ) REF

–

DAC

=−

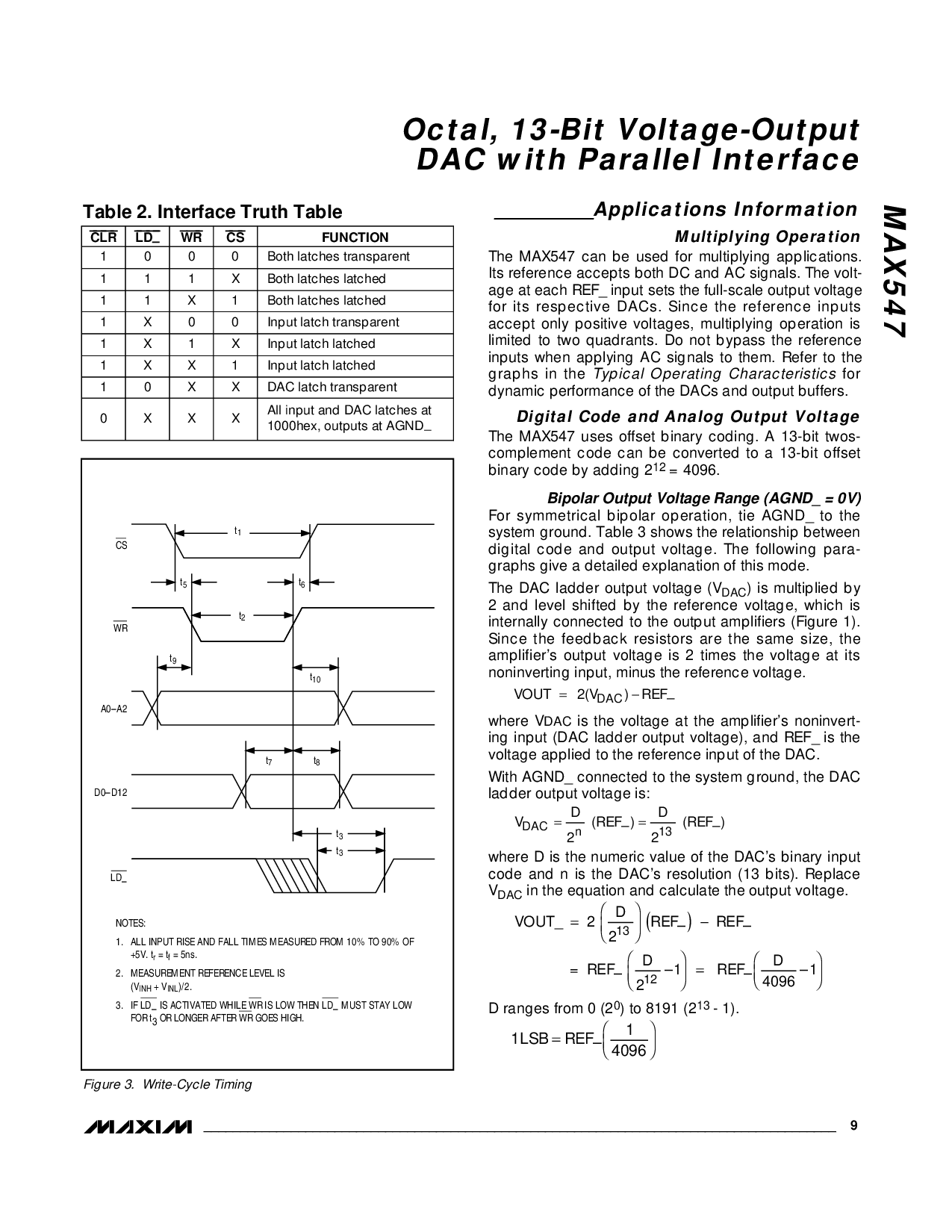

表格 2. 接口 真实 表格

MAX547

octal, 13-位 电压-输出

dac 和 并行的 接口

–

C

—

L

—

R

–

函数

1 两个都 latches transparent

1 两个都 latches latched

1 两个都 latches latched

–

L

—

D

—

–

–

0

1

1

1 输入 获得 transparent

1 输入 获得 latched

1 输入 获得 latched

X

X

X

–

W

—

R

–

0

0

1

X

–

C

—

S

–

0

1

X

1

X

0

X

1

X0

所有 输入 和 dac latches 在

1000hex, 输出 在 agnd

–

XX

X1 dac 获得 transparentx0

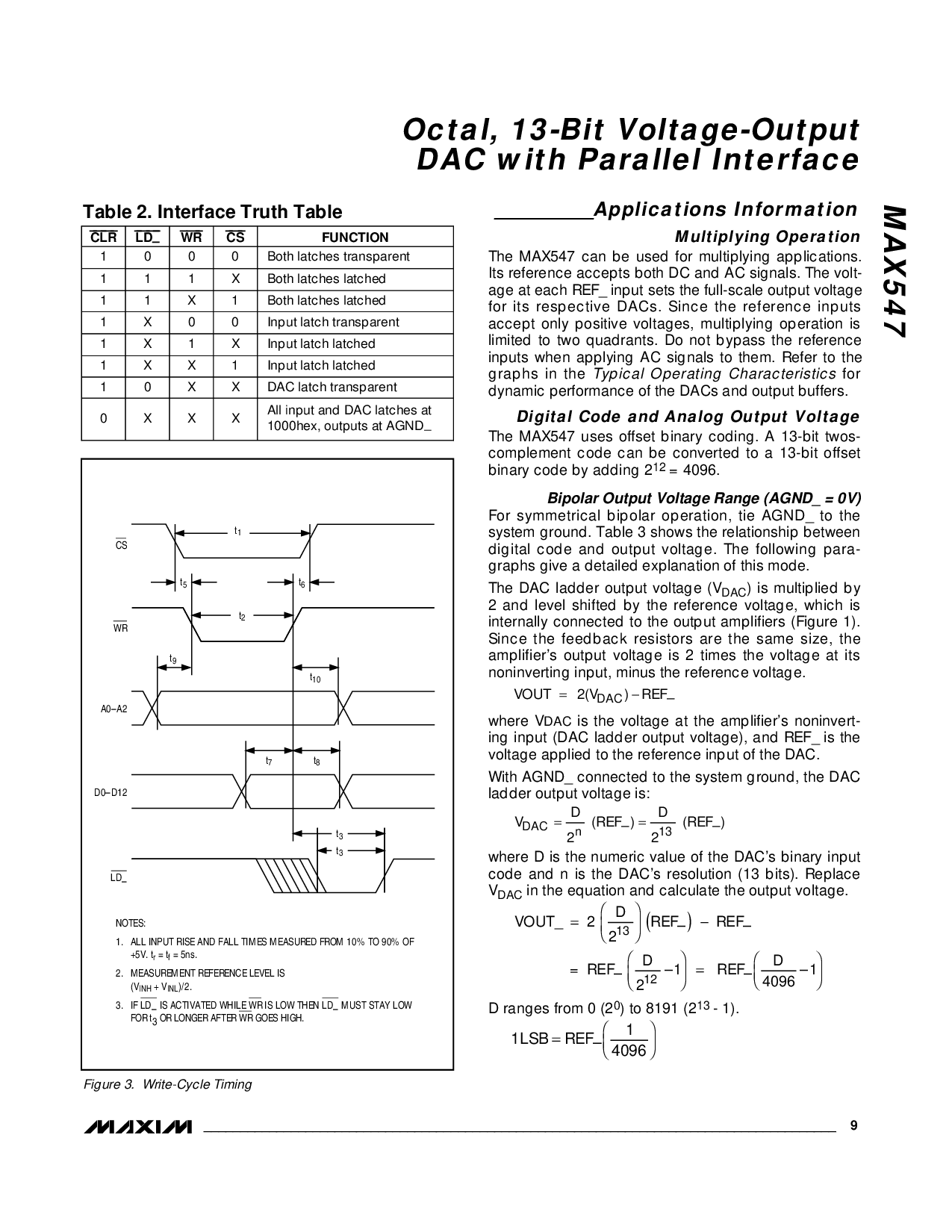

CS

WR

A0–A2

D0–D12

LD

–

注释:

1. 所有 输入 上升 和 下降 时间 量过的 从 10% 至 90% of

+5v. t

r

= t

f

= 5ns.

2. 度量 涉及 水平的 is

(v

INH

+ v

INL

)/2.

3. 如果 ld

–

是 使活动 当 wr 是 低 然后 ld

–

必须 停留 low

为 t

3

或者 变长 之后 wr 变得 高.

t

1

t

2

t

9

t

10

t

7

t

8

t

5

t

6

t

3

t

3

图示 3. 写-循环 定时