MAX199

multi-范围 (±4v, ±2v, +4v, +2v),

+5v 供应, 12-位 das 和 8+4 总线 接口

_______________________________________________________________________________________ 7

______________________________________________________________管脚 描述

数字的 地面DGND28

+5v 供应. 绕过 和 0.1µf 电容 至 agnd.v

DD

27

INT 变得 低 当 转换 是 完全 和 输出 数据 是 准备好.int24

bandgap 电压-涉及 输出 / 外部 调整 管脚. 绕过 和 一个 0.01µf 电容 至 agnd.

连接 至 v

DD

当 使用 一个 外部 涉及 在 这 ref 管脚.

REFADJ25

涉及 缓存区 输出 / 模数转换器 涉及 输入. 在 内部的 涉及 模式, 这 涉及 缓存区 提供 一个

4.096v 名义上的 输出, externally 可调整的 在 refadj. 在 外部 涉及 模式, 使不能运转 这 内部的

缓存区 用 拉 refadj 至 v

DD

.

REF26

三-状态 数字的 i/o. d2 输出 (hben = 低), d10 输出 (hben = high).d2/d1012

三-状态 数字的 i/o. d1 输出 (hben = 低), d9 输出 (hben = high).d1/d913

三-状态 数字的 i/o. d0 输出 (hben = 低), d8 输出 (hben = high). d0 = lsb.d0/d814

相似物 groundagnd15

相似物 输入 途径CH0–CH716–23

使用 至 multiplex 这 12-位 转换 结果. 当 高, 这 4 msbs 是 多路复用 在 这 数据 总线;

当 低, 这 8 lsbs 是 有 在 这 总线.

HBEN5

关闭. puts 这 设备 在 全部 电源-向下 (fullpd) 模式 当 牵引的 低.shdn6

三-状态 数字的 i/od7–d47–10

三-状态 数字的 i/o. d3 输出 (hben = 低), d11 输出 (hben = high).d3/d1111

当 cs 是 低, 一个 下落 边缘 在 rd 将 使能 一个 读 运作 在 这 数据 总线.rd4

当 cs 是 低, 在 这 内部的 acquisition 模式, 一个 rising 边缘 在 wr latches 在 配置 数据 和 开始 一个

acquisition 加 一个 转换 循环. 当 cs 是 低, 在 这 外部 acquisition 模式, 这 第一 rising 边缘 在

WR 开始 一个 acquisition 和 一个 第二 rising 边缘 在 wr ends acquisition 和 开始 一个 转换 循环.

WR3

管脚

碎片 选择, 起作用的 低.cs2

时钟 输入. 在 外部 时钟 模式, 驱动 clk 和 一个 ttl/cmos 兼容 时钟. 在 内部的 时钟 mode,

放置 一个 电容 (c

CLK

) 从 这个 管脚 至 地面 至 设置 这 内部的 时钟 频率; f

CLK

= 1.56mhz 典型

和 c

CLK

= 100pf.

CLK1

FUNCTIONNAME

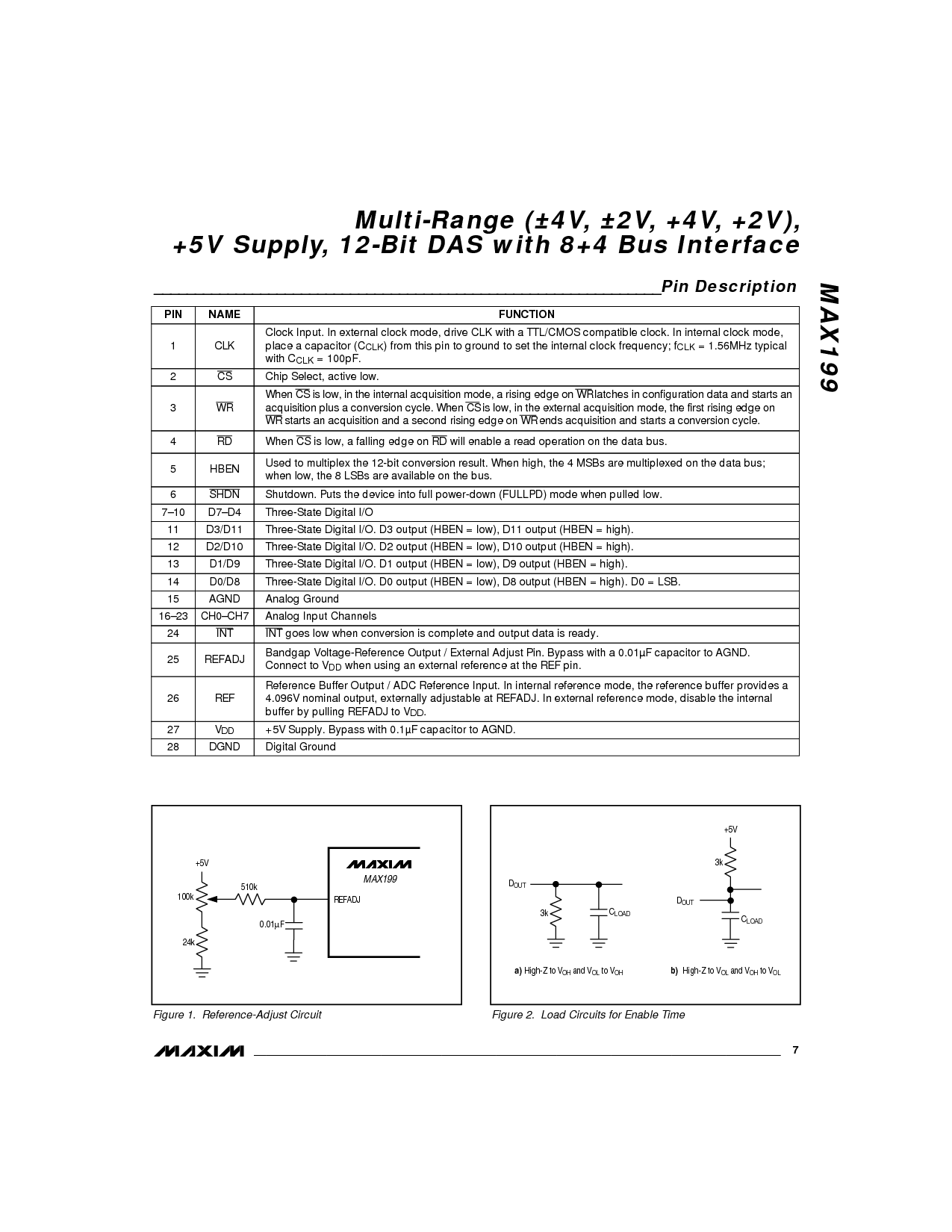

100k

510k

24k

REFADJ

+5V

0.01

µ

F

MAX199

图示 1. 涉及-调整 电路

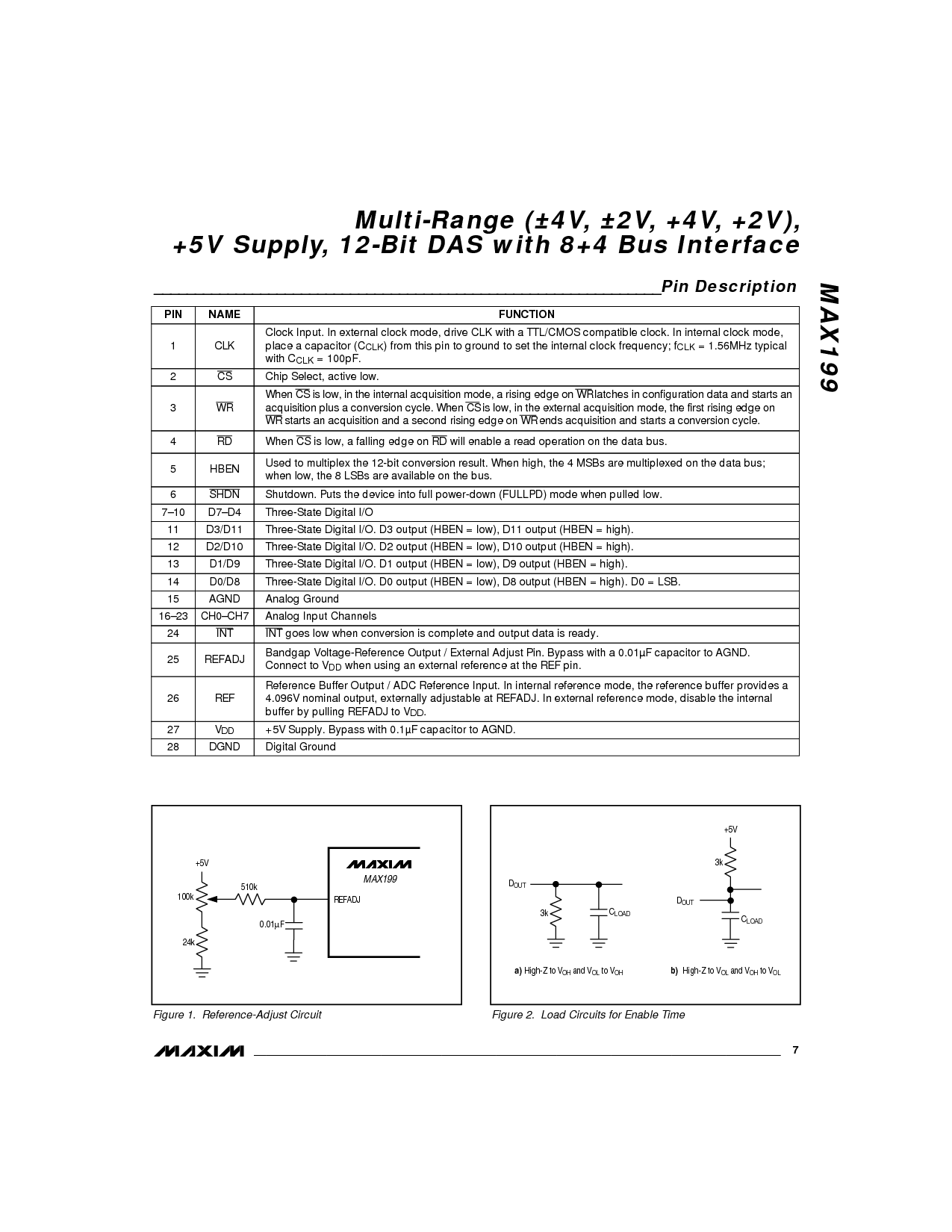

3k

3k

D

输出

D

输出

+5V

一个)

高-z 至 v

OH

和 v

OL

至 v

OH

b)

高-z 至 v

OL

和 v

OH

至 v

OL

C

加载

C

加载

图示 2. 加载 电路 为 使能 时间