MPC9448

MOTOROLA 定时 解决方案2

clk_停止

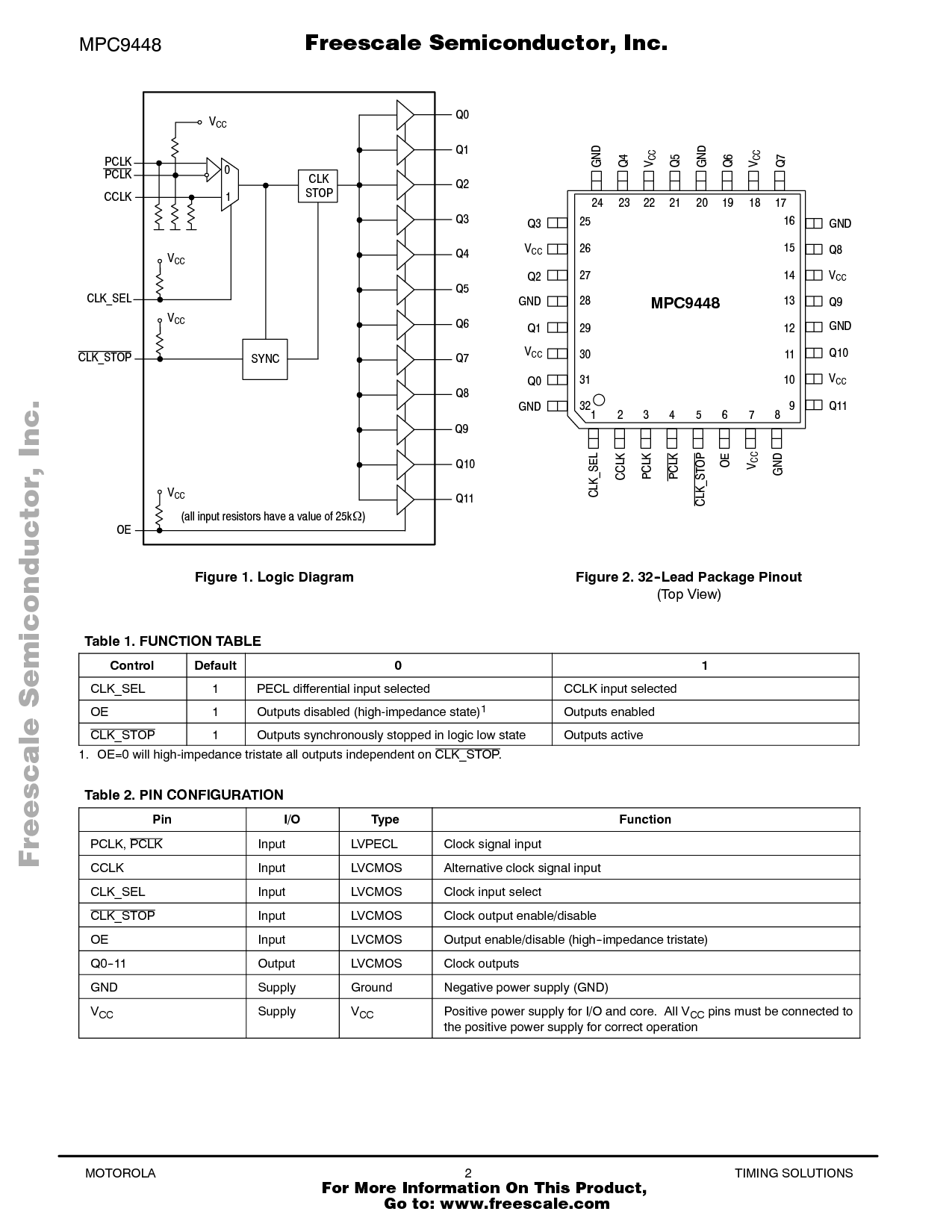

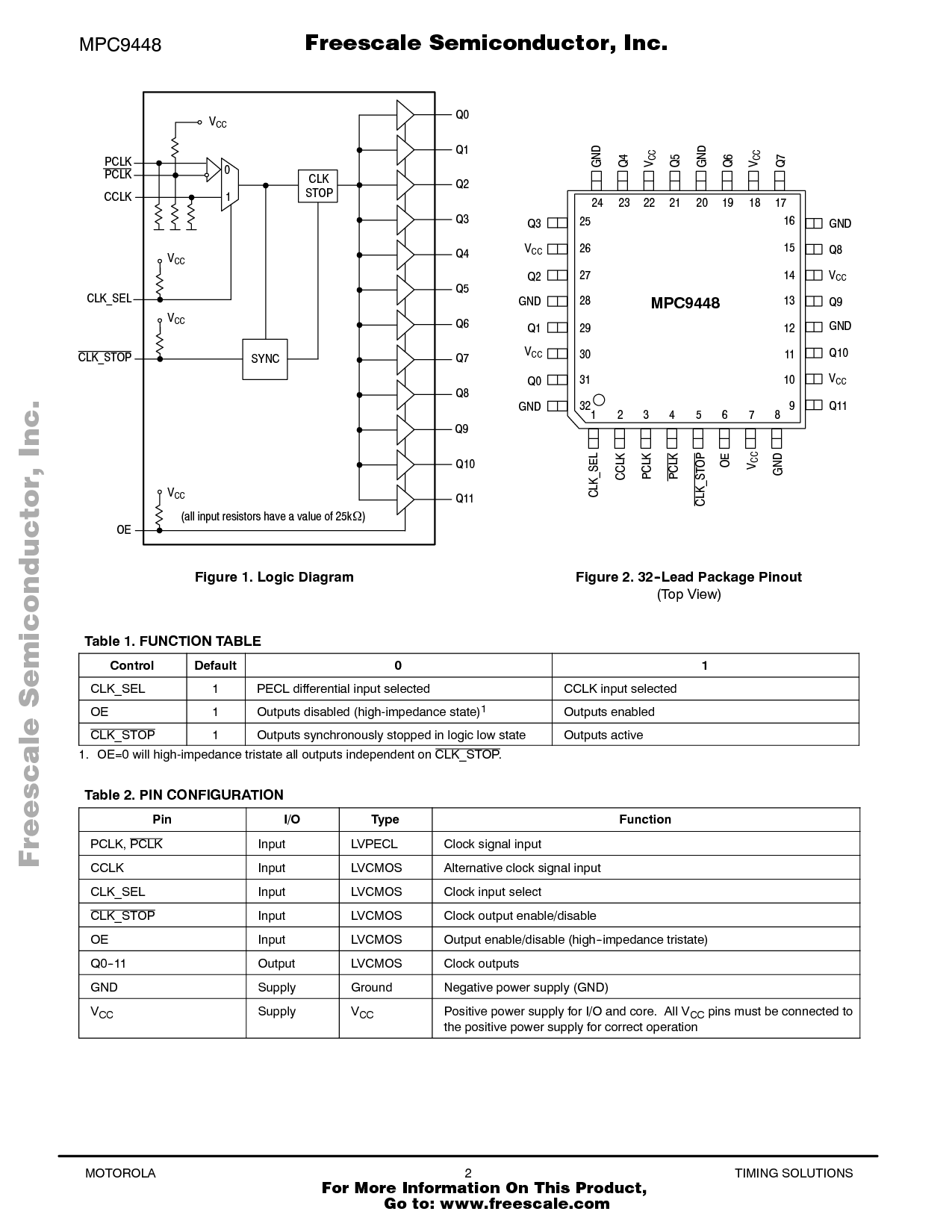

图示 1. 逻辑 图解 图示 2. 32--含铅的 包装 引脚

(顶 视图)

1

0

CCLK

停止

CLK

clk_sel

OE

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

PCLK

Q9

Q11

Q10

clk_停止

同步

PCLK

V

CC

V

CC

V

CC

V

CC

25

26

27

28

29

30

31

32

15

14

13

12

11

10

9

12345678

24 23 22 21 20 19 18 17

16

MPC9448

地

Q4

Q5

地

Q6

Q7

V

CC

V

CC

Q3

Q2

地

Q1

Q0

地

地

Q8

Q9

地

Q10

Q11

clk_sel

CCLK

OE

地

V

CC

V

CC

V

CC

V

CC

V

CC

PCLK

PCLK

(所有 输入 电阻器 有 一个 值 的 25k

Ω

)

表格 1. 函数 表格

控制 Default 0 1

clk_sel 1 PECL 差别的 输入 选择 CCLK 输入 选择

OE 1 输出 无能 (高-阻抗 状态)

1

输出 使能

clk_st运算 1 输出 synchronously stopped 在 逻辑 低 状态 输出 起作用的

1. OE=0 将 高-阻抗 tristate 所有 输出 独立 在 clk_停止.

表格 2. 管脚 配置

管脚 i/o Type 函数

pclk, PCLK 输入 LVPECL 时钟 信号 输入

CCLK 输入 LVCMOS Alternative 时钟 信号 输入

clk_sel 输入 LVCMOS 时钟 输入 选择

clk_st运算 输入 LVCMOS 时钟 输出 使能/使不能运转

OE 输入 LVCMOS 输出 使能/使不能运转 (高--阻抗 tristate)

q0--11 输出 LVCMOS 时钟 输出

地 供应 地面 负的 电源 供应 (地)

V

CC

供应 V

CC

积极的 电源 供应 为 i/o 和 核心. 所有 V

CC

管脚 必须 是 连接 至

这 积极的 电源 供应 为 准确无误的 运作

F

r

e

e

s

c

一个

l

e

S

e

m

i

c

o

n

d

u

c

t

o

r

,

I

freescale 半导体, 公司

为 更多 信息 在 这个 产品,

go 至: www.freescale.com

n

c

.

.

.