6/18

¡ 半导体

msm82c84a-2rs/gs/js

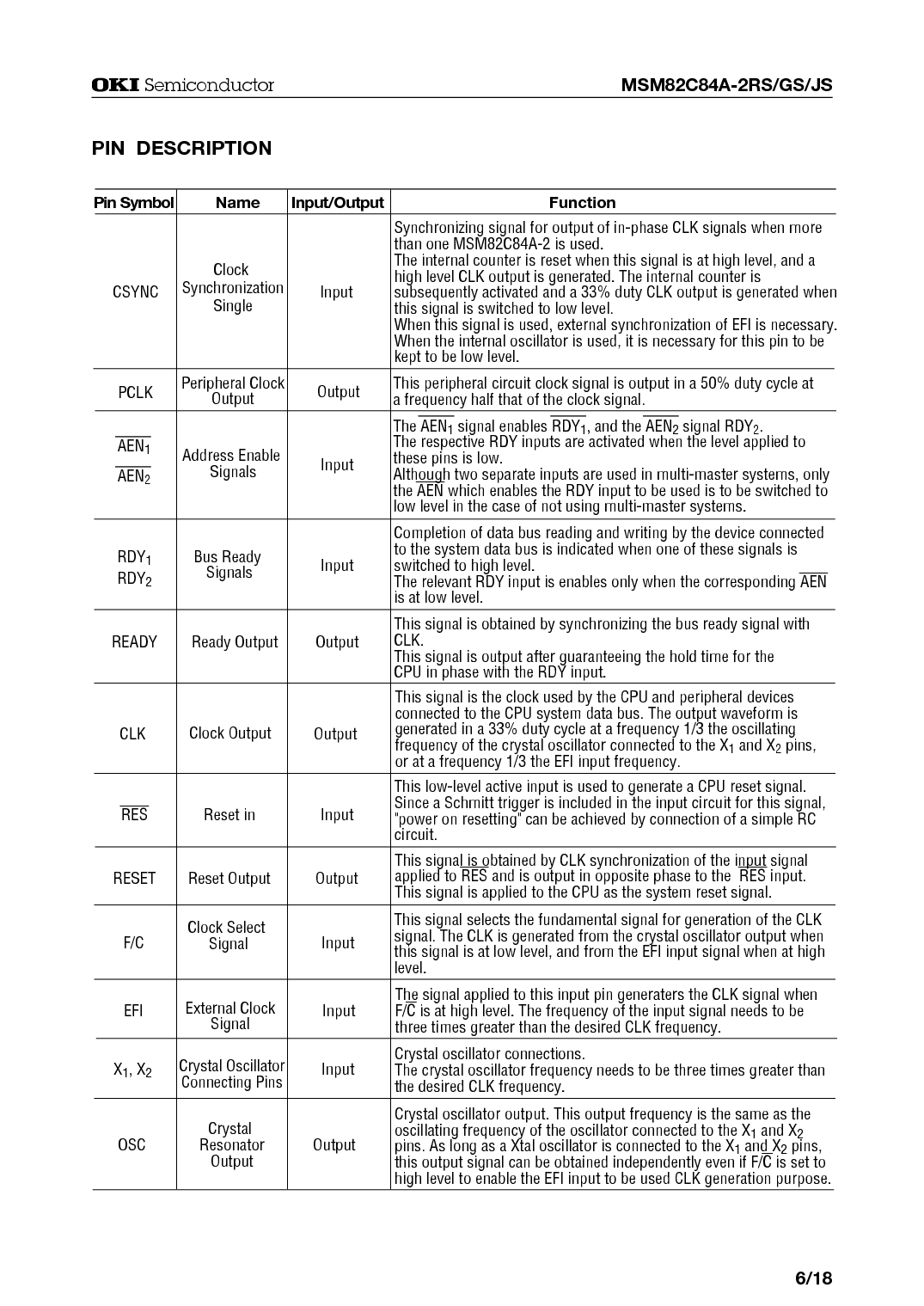

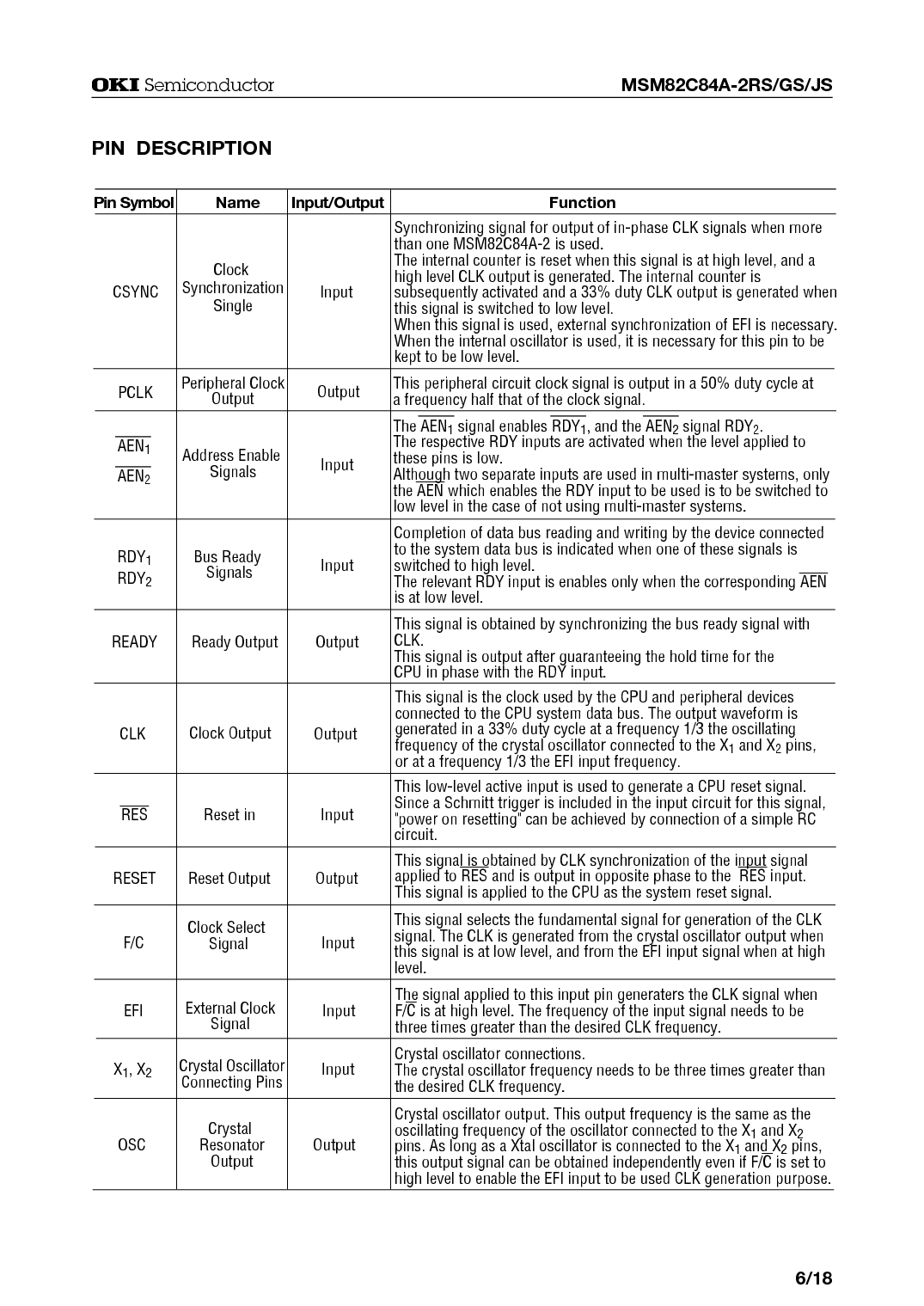

管脚 描述

CSYNC

名字

时钟

同步

单独的

输入

管脚 标识

输入/输出

函数

AEN

1

AEN

2

地址 使能

信号

输入

RDY

1

RDY

2

总线 准备好

信号

输入

准备好

准备好 输出 输出

CLK

时钟 输出

输出

RES

重置 在 输入

同步 信号 为 输出 的 在-阶段 clk 信号 当 更多

比 一个 msm82c84a-2 是 使用.

这 内部的 计数器 是 重置 当 这个 信号 是 在 高 水平的, 和 一个

高 水平的 clk 输出 是 发生. 这 内部的 计数器 是

subsequently 使活动 和 一个 33% 职责 clk 输出 是 发生 当

这个 信号 是 切换 至 低 水平的.

当 这个 信号 是 使用, 外部 同步 的 efi 是 需要.

当 这 内部的 振荡器 是 使用, 它 是 需要 为 这个 管脚 至 是

保持 至 是 低 水平的.

PCLK

输出

这个 附带的 电路 时钟 信号 是 输出 在 一个 50% 职责 循环 在

一个 频率 half 那 的 这 时钟 信号.

这 aen

1

信号 使能 rdy

1

, 和 这 aen

2

信号 rdy

2

.

这 各自的 rdy 输入 是 使活动 当 这 水平的 应用 至

这些 管脚 是 低.

虽然 二 独立的 输入 是 使用 在 multi-主控 系统, 仅有的

这

AEN

这个 使能 这 rdy 输入 至 是 使用 是 至 是 切换 至

低 水平的 在 这 情况 的 不 使用 multi-主控 系统.

completion 的 数据 总线 读 和 writing 用 这 设备 连接

至 这 系统 数据 总线 是 表明 当 一个 的 这些 信号 是

切换 至 高 水平的.

这 相关的 rdy 输入 是 使能 仅有的 当 这 相应的

AEN

是 在 低 水平的.

这个 信号 是 得到 用 同步 这 总线 准备好 信号 和

clk.

这个 信号 是 输出 之后 guaranteeing 这 支撑 时间 为 这

cpu 在 阶段 和 这 rdy 输入.

这个 信号 是 这 时钟 使用 用 这 cpu 和 附带的 设备

连接 至 这 cpu 系统 数据 总线. 这 输出 波形 是

发生 在 一个 33% 职责 循环 在 一个 频率 1/3 这 oscillating

频率 的 这 结晶 振荡器 连接 至 这 x

1

和 x

2

管脚,

或者 在 一个 频率 1/3 这 efi 输入 频率.

这个 低-水平的 起作用的 输入 是 使用 至 发生 一个 cpu 重置 信号.

自从 一个 施密特 触发 是 包含 在 这 输入 电路 为 这个 信号,

"电源 在 resetting" 能 是 达到 用 连接 的 一个 简单的 rc

电路.

重置 重置 输出 输出

这个 信号 是 得到 用 clk 同步 的 这 输入 信号

应用 至

RES

和 是 输出 在 opposite 阶段 至 这

RES

输入.

这个 信号 是 应用 至 这 cpu 作 这 系统 重置 信号.

这个 信号 选择 这 基本的 信号 为 一代 的 这 clk

信号. 这 clk 是 发生 从 这 结晶 振荡器 输出 当

这个 信号 是 在 低 水平的, 和 从 这 efi 输入 信号 当 在 高

水平的.

这 信号 应用 至 这个 输入 管脚 generaters 这 clk 信号 当

f/

C

是 在 高 水平的. 这 频率 的 这 输入 信号 needs 至 是

三 时间 更好 比 这 desired clk 频率.

f/c

时钟 选择

信号

输入

OSC

结晶

共振器

输出

输出

EFI

外部 时钟

信号

输入

附带的 时钟

输出

结晶 振荡器 连接.

这 结晶 振荡器 频率 needs 至 是 三 时间 更好 比

这 desired clk 频率.

X

1

, x

2

结晶 振荡器

连接 管脚

输入

结晶 振荡器 输出. 这个 输出 频率 是 这 一样 作 这

oscillating 频率 的 这 振荡器 连接 至 这 x

1

和 x

2

管脚. 作 长 作 一个 xtal 振荡器 是 连接 至 这 x

1

和 x

2

管脚,

这个 输出 信号 能 是 得到 independently 甚至 如果 f/

C

是 设置 至

高 水平的 至 使能 这 efi 输入 至 是 使用 clk 一代 目的.