4

256mb: x4, x8, x16 sdram micron 技术, inc., reserves 这 正确的 至 改变 产品 或者 规格 没有 注意.

256msdram_e.p65

–

rev. e; pub. 3/02 ©2002, micron 技术, 公司

256mb: x4, x8, x16

SDRAM

一般 描述

这 256mb sdram 是 一个 高-速 cmos,

动态 随机的-进入 记忆 containing

268,435,456 位. 它 是 内部 配置 作 一个 四方形-

bank dram 和 一个 同步的 接口 (所有 信号

是 注册 在 这 积极的 边缘 的 这 时钟 信号,

clk). 各自 的 这 x4’s 67,108,864-位 banks 是 orga-

nized 作 8,192 rows 用 2,048 columns 用

4 位. 各自 的 这 x8’s 67,108,864-位 banks 是 orga-

nized 作 8,192 rows 用 1,024 columns 用 8 位. 各自 的

这 x16’s 67,108,864-位 banks 是 有组织的 作 8,192

rows 用 512 columns 用 16 位.

读 和 写 accesses 至 这 sdram 是 burst

朝向; accesses 开始 在 一个 选择 location 和 con-

tinue 为 一个 编写程序 号码 的 locations 在 一个 pro-

grammed sequence. accesses begin 和 这 registra-

tion 的 一个 起作用的 command, 这个 是 然后 followed 用

一个 读 或者 写 command. 这 地址 位 regis-

tered coincident 和 这 起作用的 command 是 使用

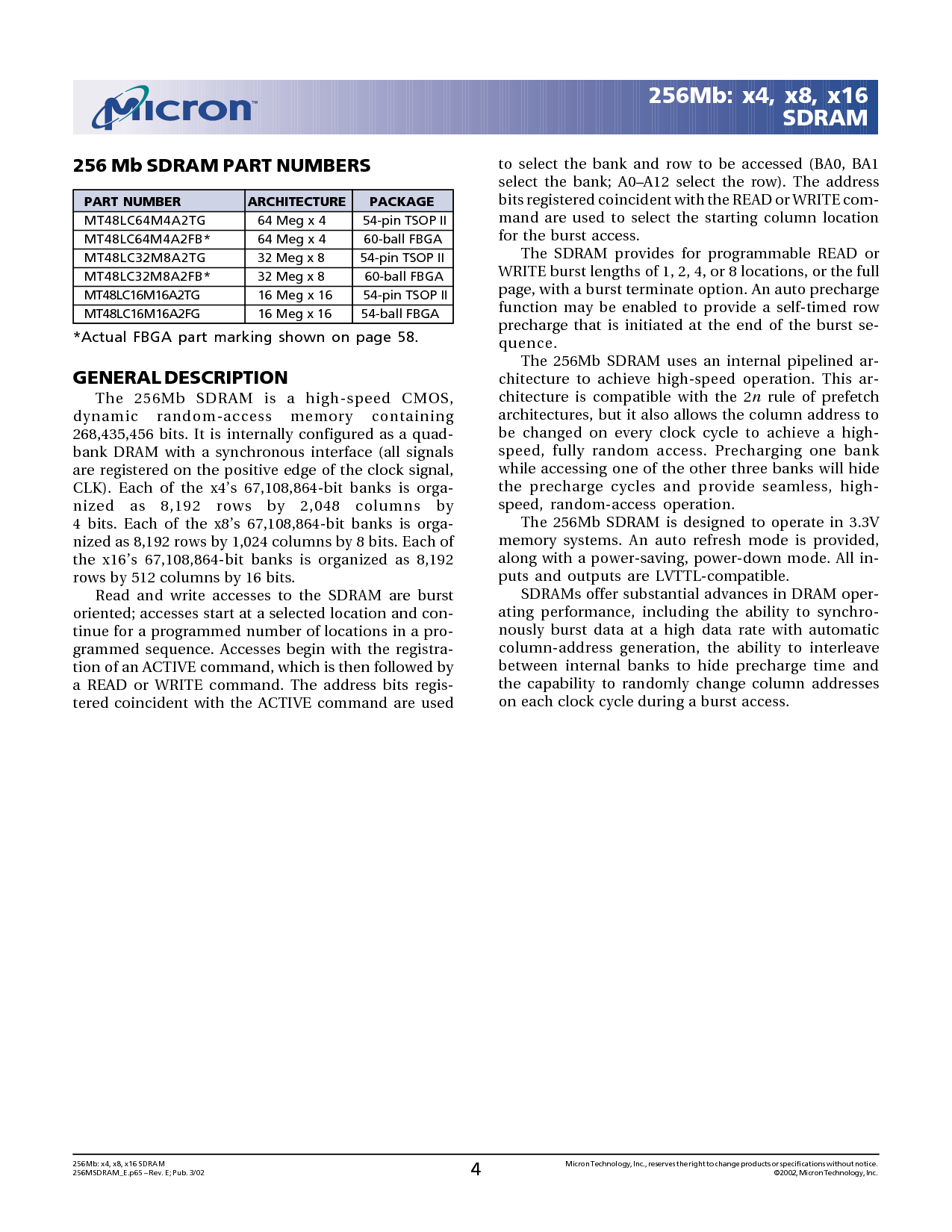

部分 号码 architecture 包装

MT48LC64M4A2TG 64 meg x 4 54-管脚 tsop ii

MT48LC64M4A2FB* 64 meg x 4 60-球 fbga

MT48LC32M8A2TG 32 meg x 8 54-管脚 tsop ii

MT48LC32M8A2FB* 32meg x 8 60-球 fbga

MT48LC16M16A2TG 16meg x 16 54-管脚 tsop ii

MT48LC16M16A2FG 16 meg x 1654-球 fbga

*actual fbga 部分 标记 显示 在 页 58.

256 mb sdram 部分 号码

至 选择 这 bank 和 行 至 是 accessed (ba0, ba1

选择 这 bank; a0–a12 选择 这 行). 这 地址

位 注册 coincident 和 这 读 或者 写 com-

mand 是 使用 至 选择 这 开始 column location

为 这 burst 进入.

这 sdram 提供 为 可编程序的 读 或者

写 burst 长度 的 1, 2, 4, 或者 8 locations, 或者 这 全部

页, 和 一个 burst terminate 选项. 一个 自动 precharge

函数 将 是 使能 至 提供 一个 自-安排时间 行

precharge 那 是 initiated 在 这 终止 的 这 burst se-

quence.

这 256mb sdram 使用 一个 内部的 pipelined ar-

chitecture 至 达到 高-速 运作. 这个 ar-

chitecture 是 兼容 和 这 2

n

rule 的 prefetch

architectures, 但是 它 也 准许 这 column 地址 至

是 changed 在 每 时钟 循环 至 达到 一个 高-

速, 全部地 随机的 进入. precharging 一个 bank

当 accessing 一个 的 这 其它 三 banks 将 hide

这 precharge 循环 和 提供 seamless, 高-

速, 随机的-进入 运作.

这 256mb sdram 是 设计 至 运作 在 3.3v

记忆 系统. 一个 自动 refresh 模式 是 提供,

along 和 一个 电源-节省, 电源-向下 模式. 所有 在-

puts 和 输出 是 lvttl-兼容.

sdrams 提供 substantial advances 在 dram oper-

ating 效能, 包含 这 能力 至 synchro-

nously burst 数据 在 一个 高 数据 比率 和 自动

column-地址 一代, 这 能力 至 interleave

在 内部的 banks 至 hide precharge 时间 和

这 能力 至 randomly 改变 column 地址

在 各自 时钟 循环 在 一个 burst 进入.