6

uc1875/6/7/8

uc2875/6/7/8

uc3875/6/7/8

CLOCKSYNC (bi-directional 时钟 和 synchroniza

-

tion 管脚):

使用 作 一个 输出, 这个 管脚 提供 一个 时钟

信号. 作 一个 输入, 这个 管脚 提供 一个 同步

要点. 在 它的 simplest 用法, 多样的 设备, 各自 和

它们的 自己的 local 振荡器 频率, 将 是 连接 至

-

gether 用 这 CLOCKSYNC 管脚 和 将 同步 在

这 fastest 振荡器. 这个 管脚 将 也 是 使用 至 syn

-

chronize 这 设备 至 一个 外部 时钟, 提供 这 ex

-

ternal 信号 是 的 高等级的 频率 比 这 local

振荡器. 一个 电阻 加载 将 是 需要 在 这个 管脚 至

降低 这 时钟 脉冲波 宽度.

e/aout (错误 放大器 输出):

这个 是 是 这 增益

平台 为 整体的 反馈 控制. 错误 放大器 输出

电压 水平 在下 1 volt 将 强迫 0° 阶段 变换. 自从

这 错误 放大器 有 一个 相当地 低 电流 驱动 capa

-

bility, 这 输出 将 是 overridden 用 驱动 和 一个 suffi

-

ciently 低 阻抗 源.

CS+ (电流 sense):

这 非-反相的 输入 至 这 cur

-

rent-故障 比较器 谁的 涉及 是 设置 内部 至

一个 fixed 2.5v (独立的 从 vref). 当 这 电压 在

这个 管脚 超过 2.5v 这 电流-故障 获得 是 设置, 这

输出 是 强迫 止 和 一个 软-开始 循环 是 initi-

ated. 如果 一个 常量 电压 在之上 2.5v 是 应用 至 这个

管脚 这 输出 是 无能 从 切换 和 使保持 在 一个

低 状态 直到 这 CS+ 管脚 是 brought 在下 2.5v. 这

输出 将 begin 切换 在 0 degrees 阶段 变换 是-

fore 这 SOFTSTART 管脚 begins 至 上升 -- 这个 情况

将 不 prematurely deliver 电源 至 这 加载.

FREQSET (振荡器 频率 设置 管脚):

一个 电阻

和 一个 电容 从 FREQSET 至 地 将 设置 这 oscil

-

lator 频率.

DELAYSET 一个-b, DELAYSET c-d (输出 延迟 con

-

trol):

这 用户 编写程序 电流 流 从 这些

管脚 至 地 设置 这 转变-在 延迟 为 这 相应的

输出 一双. 这个 延迟 是 introduced 在 转变-止 的

一个 转变 和 转变-在 的 另一 在 这 一样 leg 的 这

桥 至 提供 一个 dead 时间 在 这个 这 resonant

切换 的 这 外部 电源 switches takes 放置.

独立的 延迟 是 提供 为 这 二 half-bridges 至

accommodate differences 在 这 resonant 电容

charging 电流.

EA– (错误 放大器 反相的 输入):

这个 是 正常情况下

连接 至 这 电压 分隔物 电阻器 这个 sense

这 电源 供应 输出 电压 水平的.

EA+ (错误 放大器 非-反相的 输入):

这个 是 也不

-

mally 连接 至 一个 涉及 电压 使用 为 compari

-

son 和 这 sensed 电源 供应 输出 电压 水平的 在

这 ea+ 管脚.

地 (信号 地面):

所有 电压 是 量过的 和

遵守 至 地. 这 定时 电容, 在 这 FREQSET

管脚, 任何 绕过 电容 在 这 VREF 管脚, 绕过 ca

-

pacitors 在 VIN 和 这 ramp 电容, 在 这 RAMP

管脚, 应当 是 连接 直接地 至 这 地面 平面

near 这 信号 地面 管脚.

outa-outd (输出 一个-d):

这 输出 是 2A 至

-

tem-柱子 驱动器 优化 为 两个都 场效应晶体管 门 和

水平的-shifting transformers. 这 输出 运作 作 pairs

和 一个 名义上的 50% 职责-循环. 这 一个-b 一双 是 将

至 驱动 一个 half-桥 在 这 外部 电源 平台 和

是 syncronized 和 这 时钟 波形. 这 c-d 一双 将

驱动 这 其它 half-桥 和 切换 阶段 shifted

和 遵守 至 这 一个-b 输出.

PWRGND (电源 地面):

VC 应当 是 绕过 和

一个 陶瓷的 电容 从 这 VC 管脚 至 这 部分 的 这

地面 平面 那 是 连接 至 pwrgnd. 任何 re

-

quired 大(量) reservoir 电容 应当 并行的 这个 一个.

电源 地面 和 信号 地面 将 是 joined 在 一个 sin

-

gle 要点 至 优化 噪音 拒绝 和 降低 直流

drops.

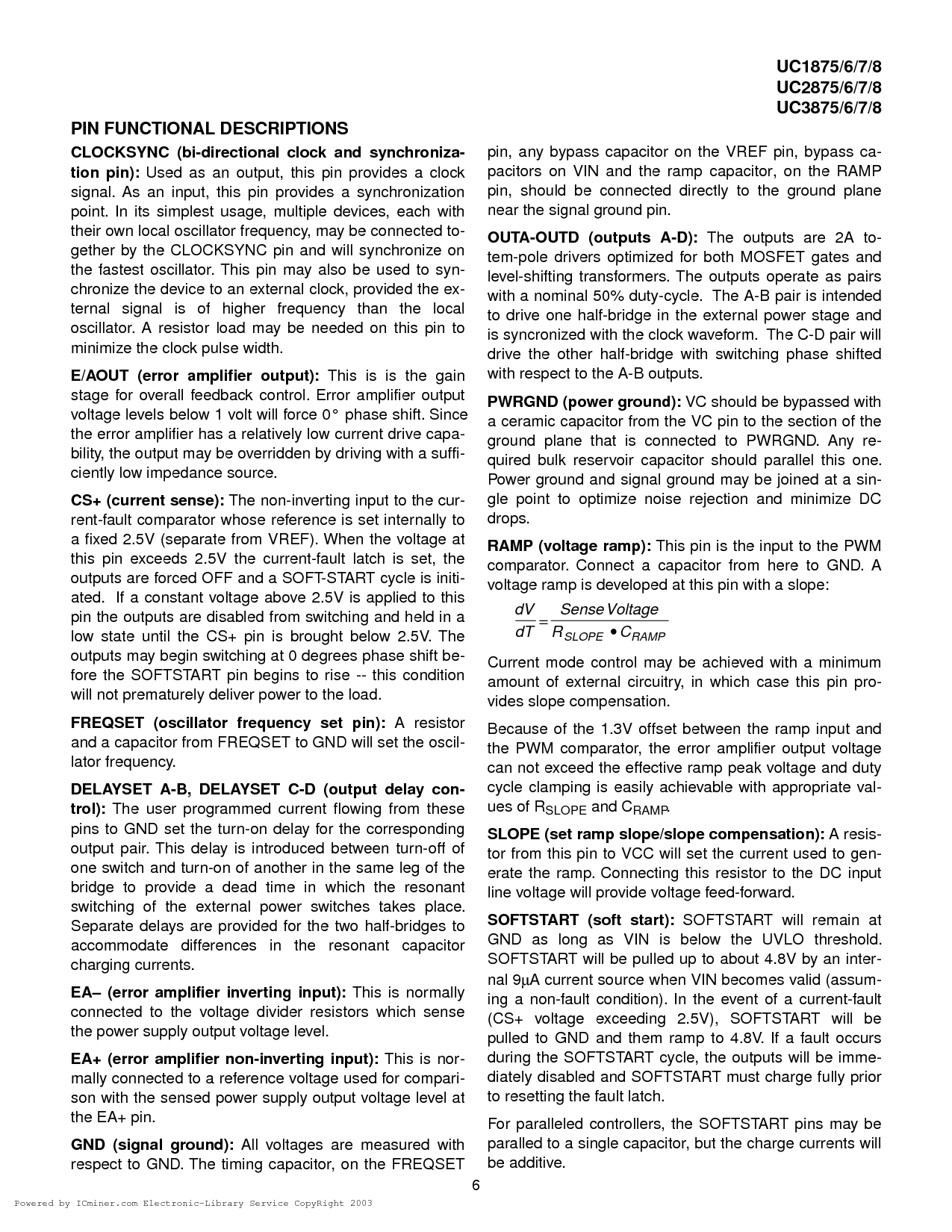

RAMP (电压 ramp):

这个 管脚 是 这 输入 至 这 PWM

比较器. 连接 一个 电容 从 here 至 地. 一个

电压 ramp 是 开发 在 这个 管脚 和 一个 斜度:

dV

dT

Sense 电压

RC

斜度 RAMP

=

•

电流 模式 控制 将 是 达到 和 一个 最小

数量 的 外部 电路系统, 在 这个 情况 这个 管脚 pro-

vides 斜度 补偿.

因为 的 这 1.3v 补偿 在 这 ramp 输入 和

这 PWM 比较器, 这 错误 放大器 输出 电压

能 不 超过 这 有效的 ramp 顶峰 电压 和 职责

循环 夹紧 是 容易地 achievable 和 适合的 val

-

ues 的 R

斜度

和 c

RAMP

.

斜度 (设置 ramp 斜度/斜度 补偿):

一个 resis

-

tor 从 这个 管脚 至 VCC 将 设置 这 电流 使用 至 gen

-

erate 这 ramp. 连接 这个 电阻 至 这 直流 输入

线条 电压 将 提供 电压 喂养-向前.

SOFTSTART (软 开始):

SOFTSTART 将 仍然是 在

地 作 长 作 VIN 是 在下 这 UVLO 门槛.

SOFTSTART 将 是 牵引的 向上 至 关于 4.8v 用 一个 inter

-

nal 9

µ

一个 电流 源 当 VIN 变为 有效的 (assum

-

ing 一个 非-故障 情况). 在 这 事件 的 一个 电流-故障

(cs+ 电压 exceeding 2.5v), SOFTSTART 将 是

牵引的 至 地 和 它们 ramp 至 4.8v. 如果 一个 故障 occurs

在 这 SOFTSTART 循环, 这 输出 将 是 imme

-

diately 无能 和 SOFTSTART 必须 承担 全部地 较早的

至 resetting 这 故障 获得.

为 paralleled 控制者, 这 SOFTSTART 管脚 将 是

paralled 至 一个 单独的 电容, 但是 这 承担 电流 将

是 additive.

管脚 函数的 描述

powered 用 icminer.com 电子的-库 维护 版权 2003