ad8801/ad8803

rev. 一个

–5–

为 例子, 当 v

REFH

= +5 v 和 v

REFL

= 0 v 这 下列-

ing 输出 电压 将 是 发生 为 这 下列的 代号:

DV

OX

输出 状态

(v

REFH

= +5 v, v

REFL

= 0 v)

255 4.98 v 全部-规模

128 2.50 v half-规模 (midscale 重置 值)

1 0.02 v 1 lsb

0 0.00 v 零-规模

涉及 输入 (v

REFH

, v

REFL

)

这 涉及 输入 管脚 设置 这 输出 电压 范围 的 所有 第八

dacs. 在 这 情况 的 这 ad8801 仅有的 这 v

REFH

管脚 是 avail-

能 至 establish 一个 用户 设计 全部-规模 输出 电压. 这

外部 涉及 电压 能 是 任何 值 在 0 和 v

DD

但是 必须 不 超过 这 v

DD

供应 电压. 在 这 情况 的 这

ad8803, 这个 有 进入 至 这 v

REFL

这个 establishes 这

零-规模 输出 电压, 任何 电压 能 是 应用 在

0 v 和 v

DD

. v

REFL

能 是 小 或者 大 在 电压 比

V

REFH

自从 这 dac 设计 使用 全部地 双向的 switches 作

显示 在 图示 3. 这 输入 阻抗 至 这 dac 有 一个 代号

依赖 变化 那 有 一个 名义上的 worst 情况 量过的 在

55

H

, 这个 是 大概 2 k

Ω

. 当 v

REFH

是 更好 比

V

REFL

, 这 refl 涉及 必须 是 能 至 下沉 电流 输出 的

这 dac ladder, 当 这 refh 涉及 是 sourcing 电流

在 这 dac ladder. 这 dac 设计 降低 涉及

glitch 电流 维持 最小 干扰 在 dac

途径 在 代号 改变.

dac 输出 (o1–o8)

这 第八 dac 输出 呈现 一个 常量 输出 阻抗 的

大概 5 k

Ω

独立 的 代号 设置. 这 distribu-

tion 的 r

输出

从 dac 至 dac 典型地 matches 在里面

±

1%.

不管怎样, 设备 至 设备 相一致 是 处理 lot 依赖

having 一个

±

20% 变化. 这 改变 在 r

输出

和 温度

有 一个 500 ppm/

°

c 温度 系数. 在 电源 shut-

向下 所有 第八 输出 是 打开 短路.

DAC

REG

#1

EN

地址

DEC

DAC

DAC

REG

#8

D10

D9

D8

D7

SER

REG

D

D0

...

...

...

DAC

1

ad8801/ad8803

D7

D0

DAC

8

D7

D0

8

R

R

V

DD

V

REFH

O1

O2

O3

O4

O5

O6

O7

O8

CS

CLK

SDI

SHDN

地

RS

V

REFL

..

..

..

.

.

.

(ad8801 仅有的) (ad8803 仅有的)

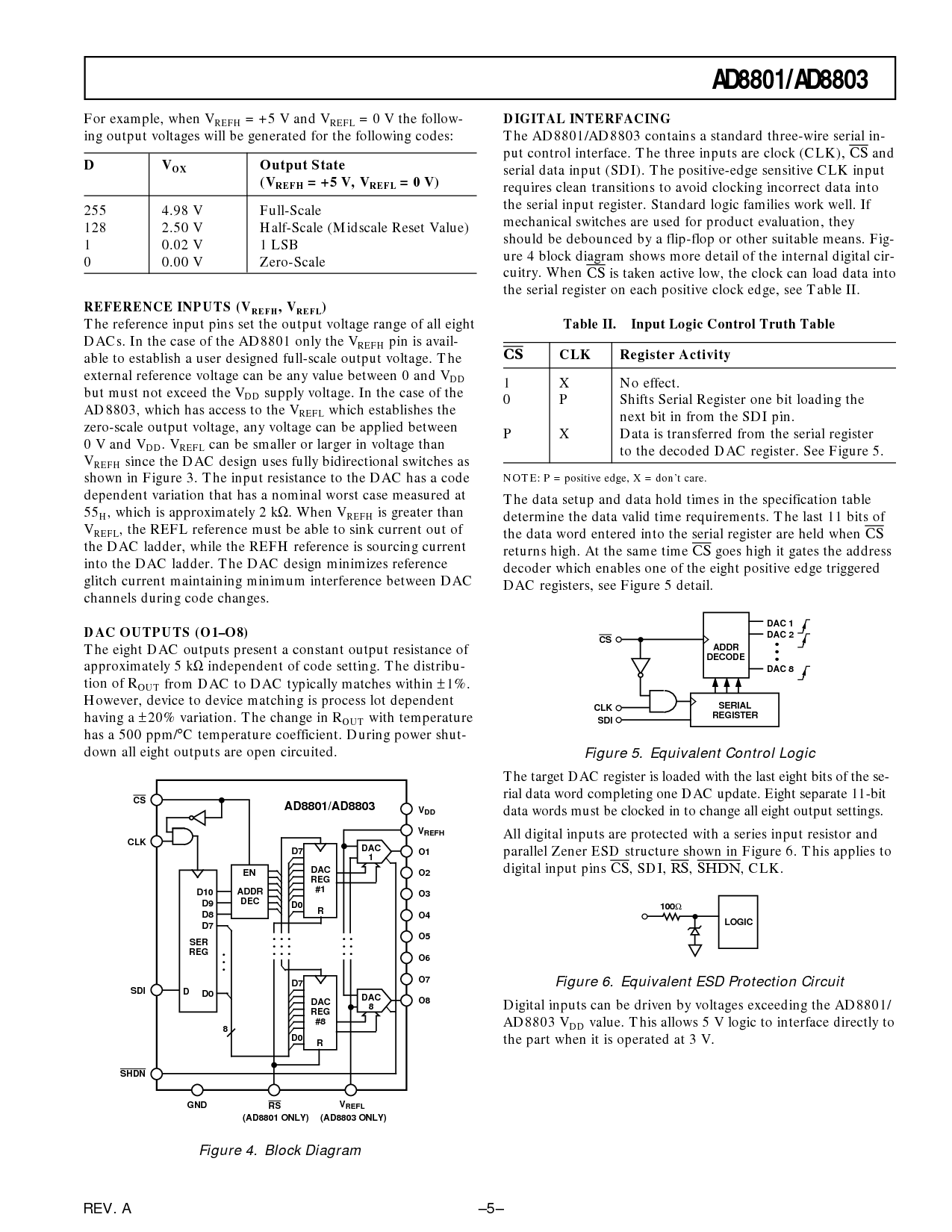

图示 4. 块 图解

数字的 接合

这 ad8801/ad8803 包含 一个 标准 三-线 串行 在-

放 控制 接口. 这 三 输入 是 时钟 (clk),

CS

和

串行 数据 输入 (sdi). 这 积极的-边缘 敏感的 clk 输入

需要 clean transitions 至 避免 clocking incorrect 数据 在

这 串行 输入 寄存器. 标准 逻辑 families 工作 好. 如果

机械的 switches 是 使用 为 产品 evaluation, 它们

应当 是 debounced 用 一个 flip-flop 或者 其它 合适的 意思. 图-

ure 4 块 图解 显示 更多 detail 的 这 内部的 数字的 cir-

cuitry. 当

CS

是 带去 起作用的 低, 这 时钟 能 加载 数据 在

这 串行 寄存器 在 各自 积极的 时钟 边缘, 看 表格 ii.

表格 ii. 输入 逻辑 控制 真实 表格

CS

CLK 寄存器 activity

1 X 非 效应.

0 P shifts 串行 寄存器 一个 位 加载 这

next 位 在 从 这 sdi 管脚.

P X 数据 是 transferred 从 这 串行 寄存器

至 这 解码 dac 寄存器. 看 图示 5.

便条: p = 积极的 边缘, x = don’t 小心.

这 数据 建制 和 数据 支撑 时间 在 这 规格 表格

决定 这 数据 有效的 时间 (所需的)东西. 这 last 11 位 的

这 数据 文字 entered 在 这 串行 寄存器 是 使保持 当

CS

returns 高. 在 这 一样 时间

CS

变得 高 它 门 这 地址

解码器 这个 使能 一个 的 这 第八 积极的 边缘 triggered

dac 寄存器, 看 图示 5 detail.

.

.

.

dac 1

dac 2

dac 8

地址

DECODE

串行

寄存器

CS

CLK

SDI

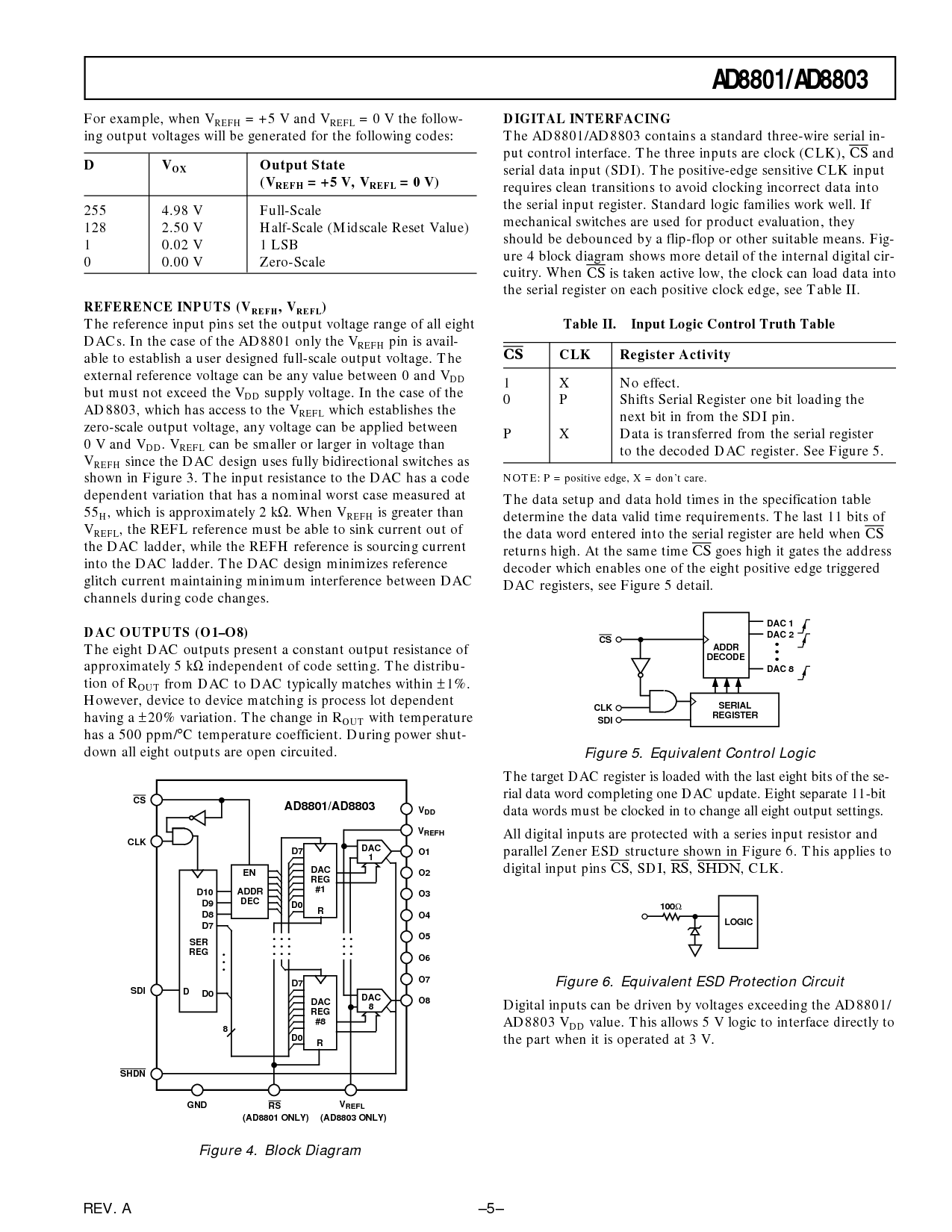

图示 5. 相等的 控制 逻辑

这 目标 dac 寄存器 是 承载 和 这 last 第八 位 的 这 se-

rial 数据 文字 完成 一个 dac 更新. 第八 独立的 11-位

数据 words 必须 是 clocked 在 至 改变 所有 第八 输出 settings.

所有 数字的 输入 是 保护 和 一个 序列 输入 电阻 和

并行的 齐纳 静电释放 结构 显示 在 图示 6. 这个 应用 至

数字的 输入 管脚

CS

, sdi,

RS

,

SHDN

, clk.

逻辑

100

Ω

图示 6. 相等的 静电释放 保护 电路

数字的 输入 能 是 驱动 用 电压 exceeding 这 ad8801/

ad8803 v

DD

值. 这个 准许 5 v 逻辑 至 接口 直接地 至

这 部分 当 它 是 运作 在 3 v.