ad7792/ad7793

rev. 0 | 页 6 的 32

定时 特性

AV

DD

= 2.7 v 至 5.25 v; dv

DD

= 2.7 v 至 5.25 v; 地 = 0 v, 输入 逻辑 0 = 0 v, 输入 逻辑 1 = dv

DD

, 除非 其它wise 指出.

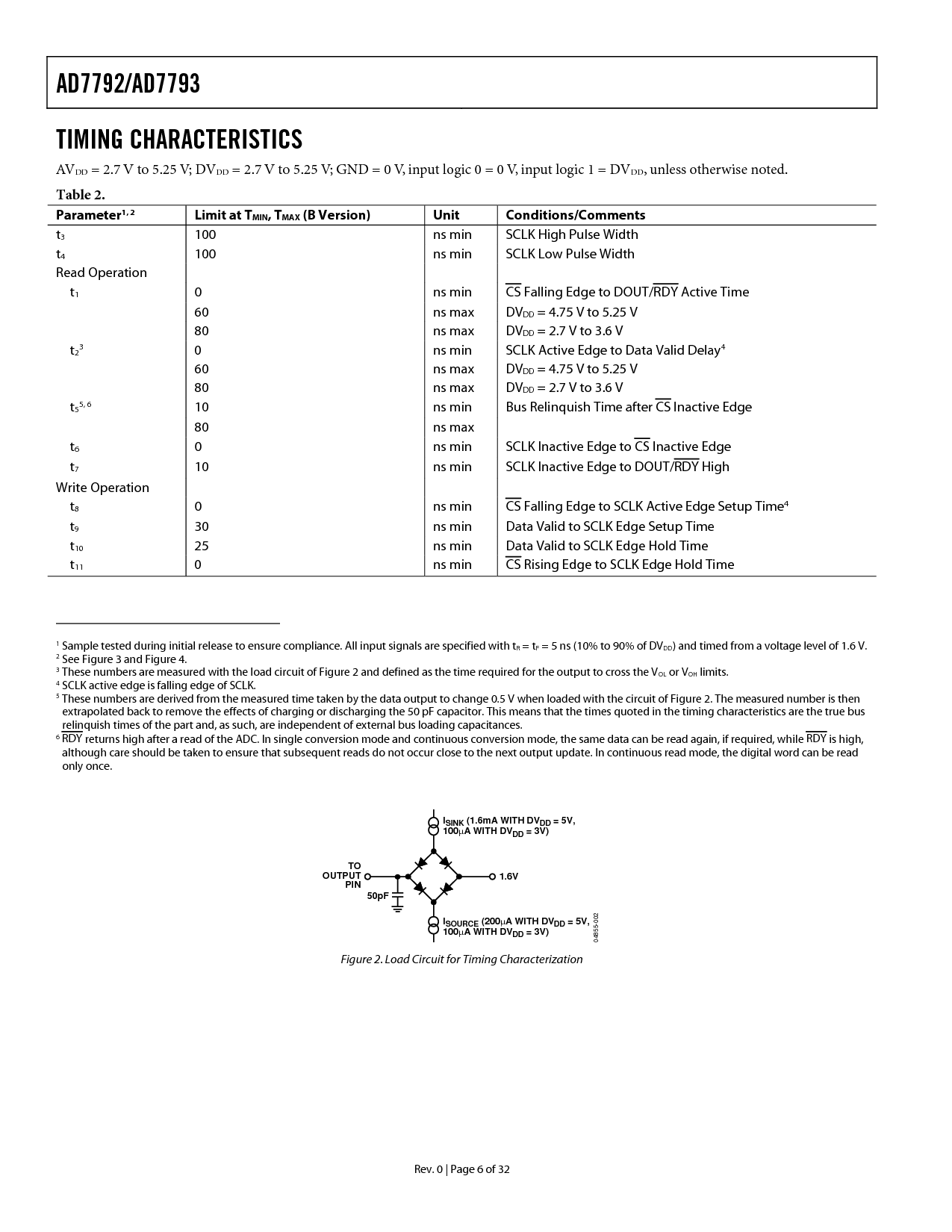

表格 2.

参数

1, 2

限制 在 t

最小值

, t

最大值

(b 版本) 单位 情况/comments

t

3

100 ns 最小值 sclk 高 脉冲波 宽度

t

4

100 ns 最小值 sclk 低 脉冲波 宽度

读 运作

t

1

0 ns 最小值

CS

下落 边缘 至 dout/rdy 起作用的 时间

60 ns 最大值 DV

DD

= 4.75 v 至 5.25 v

80 ns 最大值 DV

DD

= 2.7 v 至 3.6 v

t

2

3

0 ns 最小值 sclk 起作用的边缘 至 数据 有效的 延迟

4

60 ns 最大值 DV

DD

= 4.75 v 至 5.25 v

80 ns 最大值 DV

DD

= 2.7 v 至 3.6 v

t

5

5, 6

10 ns 最小值

总线 relinquish 时间 之后 cs

inactive 边缘

80 ns 最大值

t

6

0 ns 最小值

sclk inactive 边缘 至 cs

inactive 边缘

t

7

10 ns 最小值

sclk inactive 边缘 至 dout/rdy

高

写 运作

t

8

0 ns 最小值

CS

下落 边缘 至 sclk 起作用的 边缘 建制 时间

4

t

9

30 ns 最小值 数据 有效的 至sclk 边缘 建制 时间

t

10

25 ns 最小值 数据 有效的 至sclk 边缘 支撑 时间

t

11

0 ns 最小值

CS

rising 边缘 至 sclk 边缘 支撑 时间

1

样本 测试 在 最初的 释放 至 确保遵从. 所有 输入 信号 是 指定 和 t

R

= t

F

= 5 ns (10% 至 90% 的 dv

DD

) 和 安排时间 从 一个 电压 水平的 的 1.6 v.

2

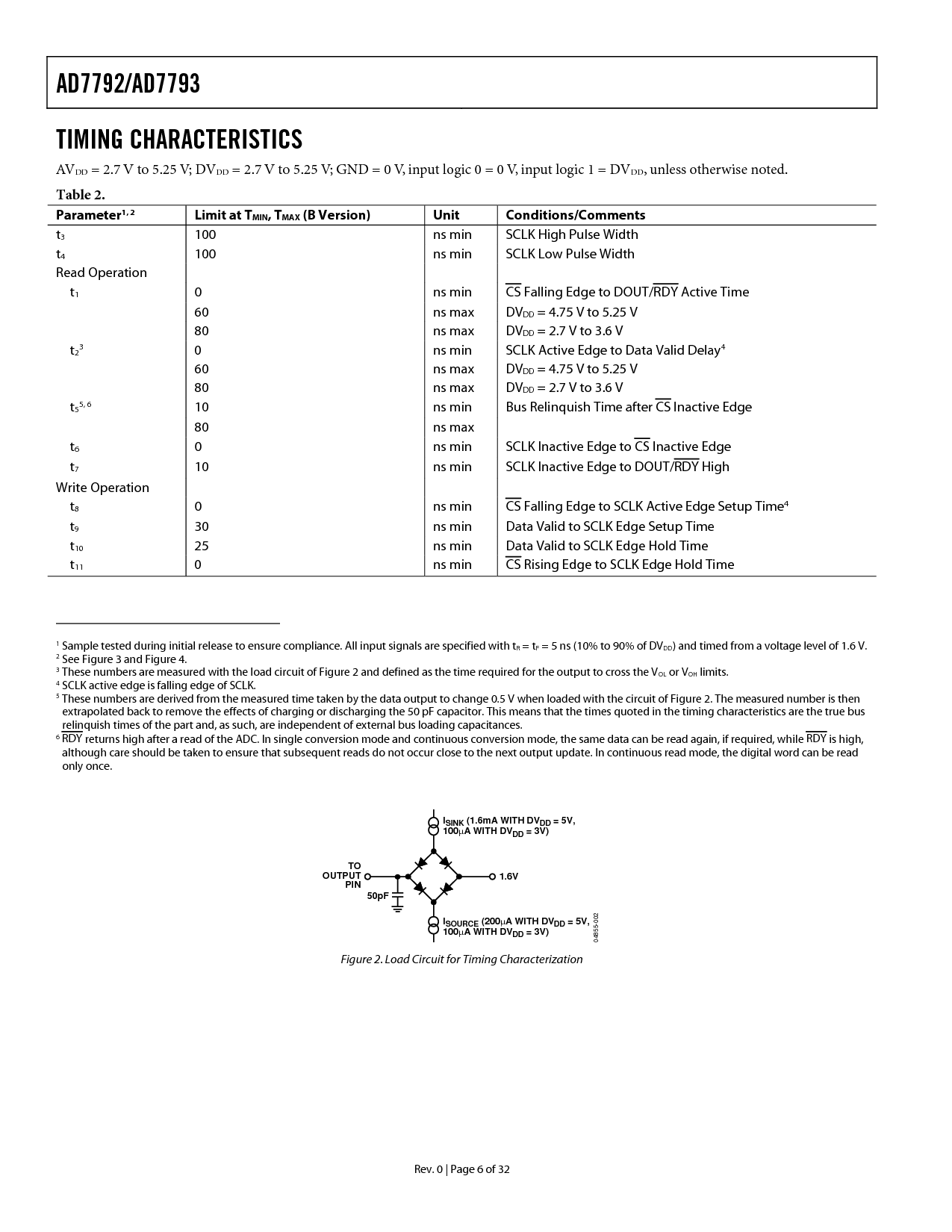

看 图示 3 和 图示 4.

3

这些 号码 是 量过的 和 这 加载 电路 的 图示 2 和 定义 作 这 时间 必需的 为 这 输出 至 交叉 这 v

OL

或者 v

OH

限制.

4

sclk 起作用的 边缘 是 下落 边缘 的 sclk.

5

这些 号码 是 获得 从 这 量过的 时间 带去 用 这 数据 输出 至 改变 0.5 v 当 承载 和 这 电路 的 figure 2. 这 量过的 号码 是 然后

extrapolated 后面的 至 除去 这 影响 的 charging 或者 discharging 这 50 pf 电容. 这个 意思 那 这 时间 quoted 在 这定时 特性 是 这 真实 总线

relinquish 时间 的 这 部分 和, 作 此类, 是 独立 的 外部 总线 加载 capacitances.

6

RDY

returns 高 之后 一个 读 的 这 模数转换器. 在 单独的 转换 模式 和 持续的 转换 模式, 这 一样 数据 能 是 读 again, 如果 必需的, 当

RDY

是 高,

虽然 小心 应当 是 带去 至 确保 那 subsequent 读 做 不 出现 关闭 至 这 next 输出 更新. 在 持续的 读模式, 这 数字的 文字 能 是 读

仅有的 once.

04855-002

I

下沉

(1.6ma 和 dv

DD

= 5v,

100

µ

一个 和 dv

DD

= 3v)

I

源

(200

µ

一个 和 dv

DD

= 5v,

100

µ

一个 和 dv

DD

= 3v)

1.6v

至

输出

管脚

50pF

图示 2. 加载 电路 为 定时 描绘