3

http://www.国家的.com

complement 号码 能 是 转变 至 补偿 二进制的 用

反相的 这 msb. 这个 是 这 first 步伐 在 这 matlab

routine 为 fft 分析.

histogram 模式

在 这 第二 模式 的 运作, 这 “histogram” 模式,

这 数据 俘获 板 运作 作 一个 硬件 histo-

grammer. 这 板 做 不 collect 一个 相接的 record

从 这 模数转换器; instead, 它 compiles statistical 信息

用 counting 这 号码 的 时间 那 这 模数转换器

输出 各自 代号. 这 大多数 significant 15 位 的 这

转换器 define 32k histogram bins. 这 msb 的 这

数据 是 inverted 在之前 正在 贮存 (所有 数据 是 treated 作

补偿 二进制的 format). 模数转换器 数据 是 排整齐 至 这 least sig-

nificant 位, 和 unused 高等级的 位 是 设置 至 0s. 各自 bin

是 cleared initially. 这 模数转换器 输出 代号 是 使用 作 这

地址 为 这 sram 在 这 板, 和 作 各自 代号 是

读 用 这 数据 俘获 板, 这 数据 在 那 location

在 这 sram 是 读, incremented 和 写 后面的 至 这

sram. 这个 counting 需要 多样的 时钟 循环, 所以

这 数据 是 不 counted 在 real 时间. 在 事实, 11 样本 的

数据 是 missed 为 各自 样本 那 是 counted. 这 his-

togram 俘获 terminates 当 一个 bin reaches 这 计数

specified 用 插件 switches 4 和 5. 这 32k histogram bin

counts 是 然后 returned 通过 这 串行 端口. 如果 这 输入

信号 至 这 模数转换器 是 一个 pure sinusoid, 然后 这 histogram

信息 能 是 对照的 至 这 theoretical

probability 密度 的 一个 sinusoid 和 这 线性 的 这

模数转换器 能 是 计算. 这 有提供的 matlab script

dnl_inl 使用 这个 方法. 请 谈及 至 这 ieee

标准 为 digitizing 波形recorders (ieee 标准

1057-1994) 为 更多 信息关于 这个 技巧.

硬件 configuration

跳越者

这 数据 俘获 板 有 3 跳越者 那 必须 是 con-

figured 在之前 使用. 这 first 跳越者, vcore, sets 这

核心 电压 使用 用 这 fpga. 这个 跳越者 是 总是 设置

至 5v. (一个 电压 调整器 在 这 板 减少 这 sup-

plied +5v 至 +3.3v 为 这 fpga i/o 和 其它

组件 在 这 板.) 这 第二 跳越者, wclk,

选择 这 时钟 源 为 这 先进先出. 当 capturing

数据 从 一个 模数转换器 evaluation 板,

wclk 应当

总是 是 设置 至 rdy2

. 这个 选择 这 dr (数据

准备好) 时钟 线条 从 这 模数转换器 evaluation 板 管脚

20b. 这 第三 跳越者 块, j2, 是 unused.

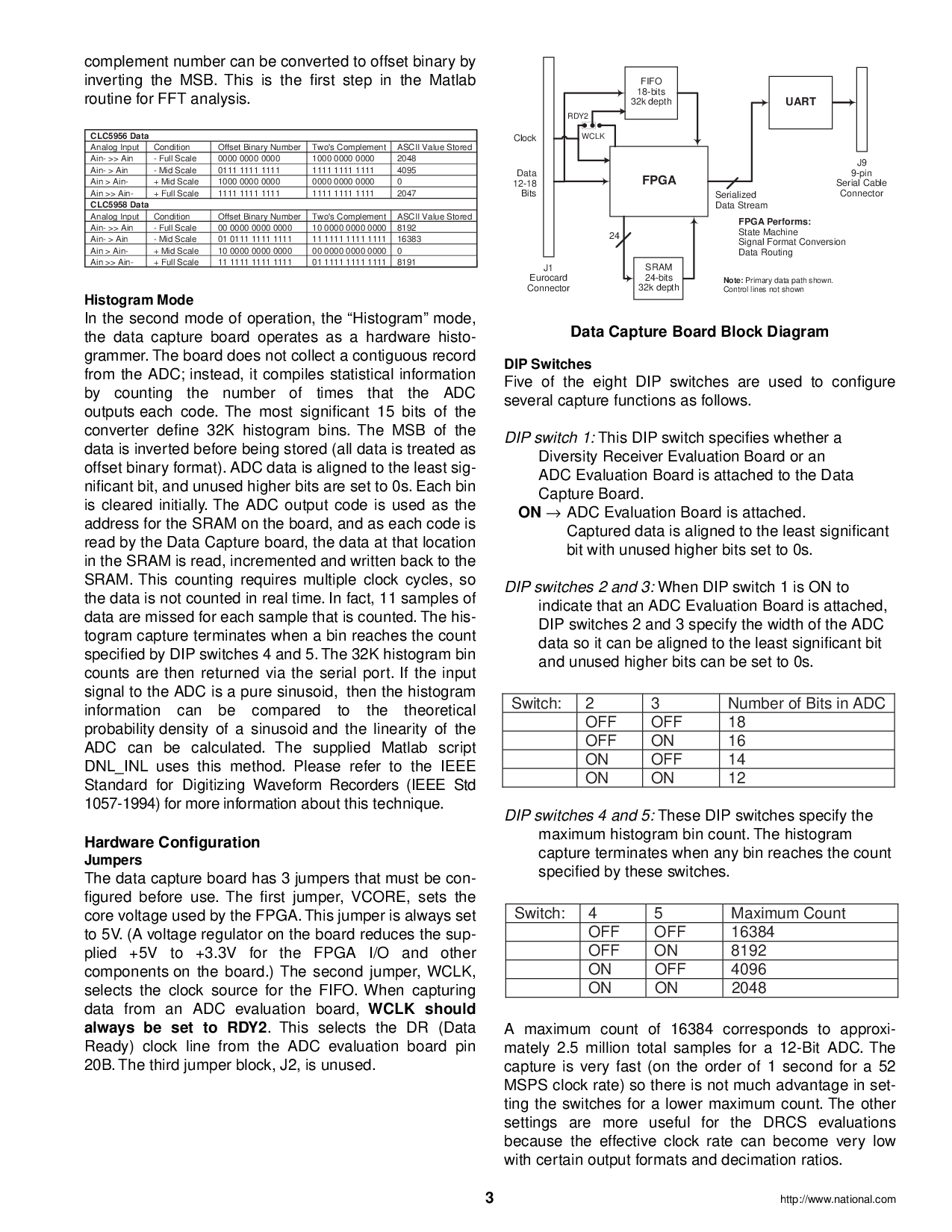

数据 俘获 板 块 图解

插件 switches

five 的 这 第八 插件 switches 是 使用 至 configure

一些 俘获 功能 作 跟随.

插件 转变 1:

这个 插件 转变 specifies whether 一个

diversity 接受者 evaluation 板 或者 一个

模数转换器 evaluation 板 是 连结 至 这 数据

俘获 板.

在

→

模数转换器 evaluation 板 是 连结.

captured 数据 是 排整齐 至 这 least significant

位 和 unused 高等级的 位 设置 至 0s.

插件 switches 2 和 3:

当 插件 转变 1 是 在 至

表明 那 一个 模数转换器 evaluation 板 是 连结,

插件 switches 2 和 3 具体说明 这 宽度 的 这 模数转换器

数据 所以 它 能 是 排整齐 至 这 least significant 位

和 unused 高等级的 位 能 是 设置 至 0s.

插件 switches 4 和 5:

这些 插件 switches 具体说明 这

最大 histogram bin 计数. 这 histogram

俘获 terminates 当 任何 bin reaches 这 计数

specified 用 这些 switches.

一个 最大 计数 的 16384 corresponds 至 approxi-

mately 2.5 million 总的 样本 为 一个 12-位 模数转换器. 这

俘获 是 非常 快 (在 这 顺序 的 1 第二 为 一个 52

msps 时钟 比率) 所以 那里 是 不 更 有利因素 在 设置-

ting 这 switches 为 一个 更小的 最大 计数. 这 其它

settings 是 更多 有用的 为 这 drcs evaluations

因为 这 有效的 时钟 比率 能 变为 非常 低

和 确实 输出 formats 和 decimation ratios.

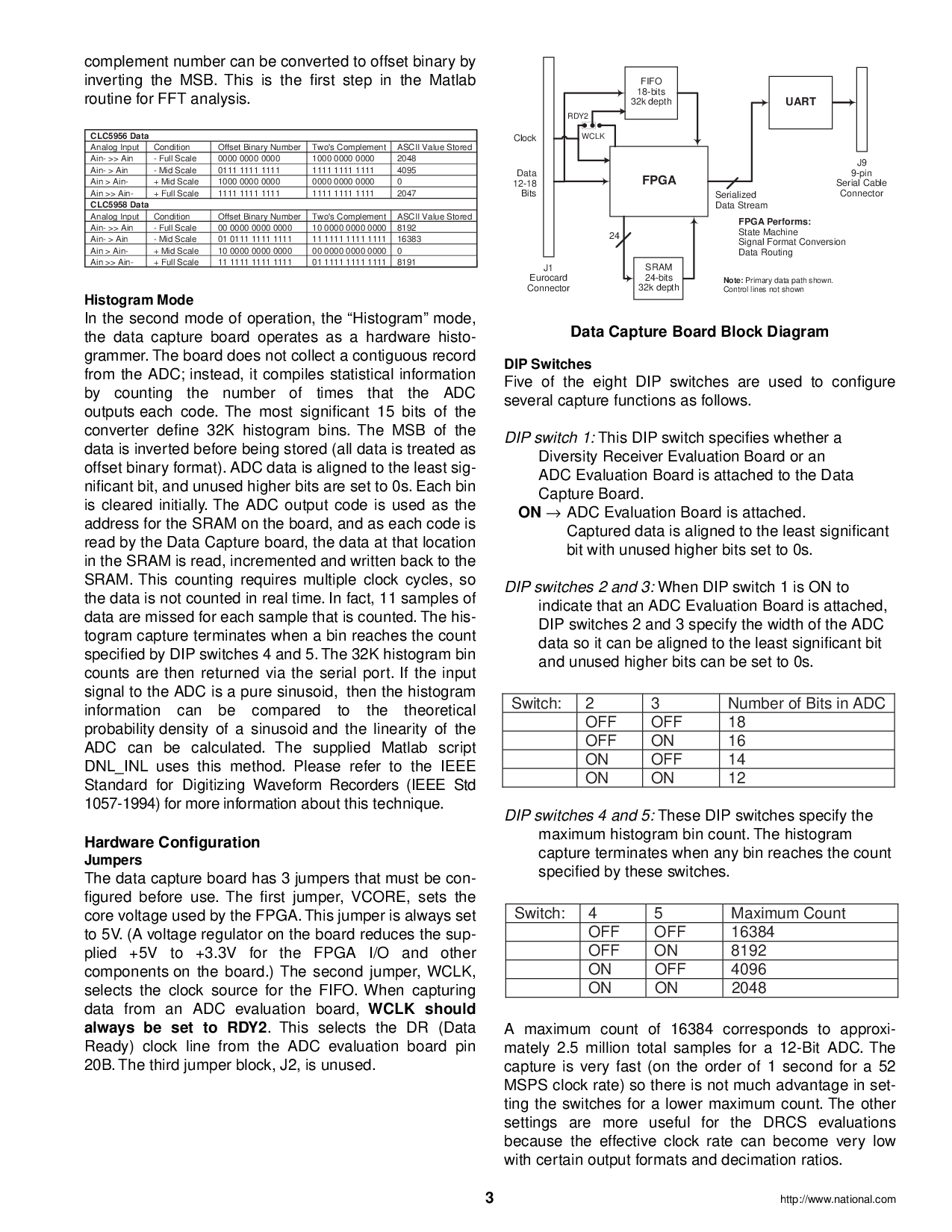

clc5956 数据

相似物 输入 情况 补偿 二进制的 号码 二's complement ascii 值 贮存

ain- >> ain - 全部 规模 0000 0000 0000 1000 0000 0000 2048

ain- > ain - mid 规模 0111 1111 1111 1111 1111 1111 4095

ain > ain- + mid 规模 1000 0000 0000 0000 0000 0000 0

ain >> ain- + 全部 规模 1111 1111 1111 1111 1111 1111 2047

clc5958 数据

相似物 输入 情况 补偿 二进制的 号码 二's complement ascii 值 贮存

ain- >> ain - 全部 规模 00 0000 0000 0000 10 0000 0000 0000 8192

ain- > ain - mid 规模 01 0111 1111 1111 11 1111 1111 1111 16383

ain > ain- + mid 规模 10 0000 0000 0000 00 0000 0000 0000 0

ain >> ain- + 全部 规模 11 1111 1111 1111 01 1111 1111 1111 8191

fpga 执行:

状态 机器

信号 format 转换

数据 routing

数据

12-18

位

J1

Eurocard

连接器

FPGA

SRAM

24-位

32k depth

先进先出

18-位

32k depth

UART

J9

9-管脚

串行 缆索

连接器

24

Serialized

数据 stream

便条:

primary 数据 path 显示.

控制 线条 不 显示

RDY2

WCLK

时钟

转变: 2 3 号码 的 位 在 模数转换器

止 止 18

止 在 16

在 止 14

在 在 12

转变: 4 5 最大 计数

止 止 16384

止 在 8192

在 止 4096

在 在 2048