管脚 描述

看

图示 4

通过

图示 10

为 输入 和 输出 sche-

matics.

管脚 1 — f

最小值

:

一个 电阻 从 这个 管脚 至 地面 sets 这 自由

run 频率 的 这 lm1290. 这 自由 run 频率 应当

是 设置 典型地 作:

f

最小值

=

0.85(f

MINLOCK

)−2khz

在哪里 f

MINLOCK

是 这 最小 锁 频率 必需的 为

这 应用. 这 阻抗 必需的 至 设置 这个 频率

是 大概:

为 例子, 至 find R

最小值

为 VGA 这个 有 f

MINLOCK

=

31.469 khz,

f

最小值

=

0.85(31.469 kHz)−2khz

=

24749

Rounding 至 这 closest 标准 1

%

电阻 给 R

最小值

=

21.5 k

Ω

.

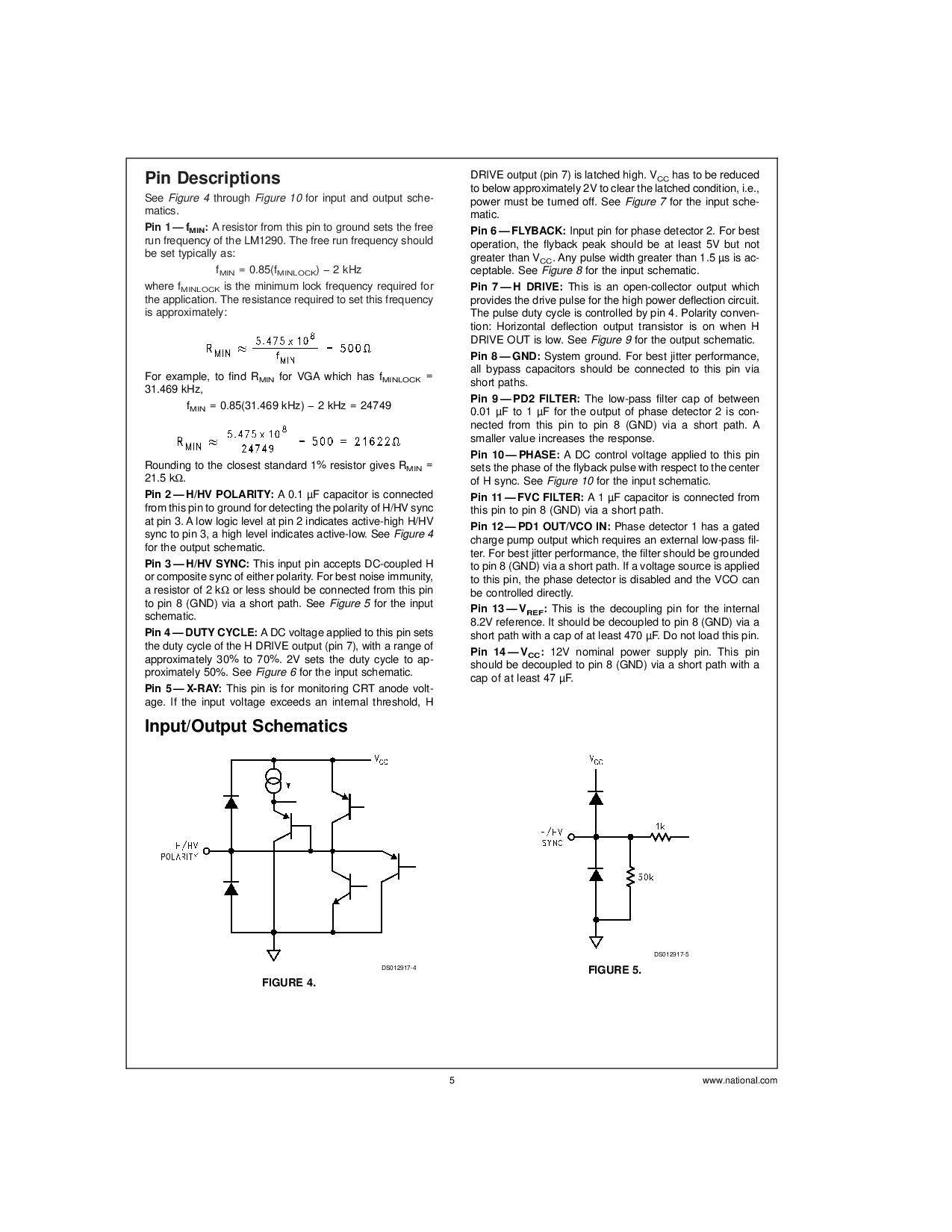

管脚 2 — h/hv 极性:

一个 0.1 µF 电容 是 连接

从 这个 管脚 至 地面 为 detecting 这 极性 的 h/hv 同步

在 管脚 3. 一个 低 逻辑 水平的 在 管脚 2 indicates 起作用的-高 h/hv

同步 至 管脚 3, 一个 高 水平的 indicates 起作用的-低. 看

图示 4

为 这 输出 图式.

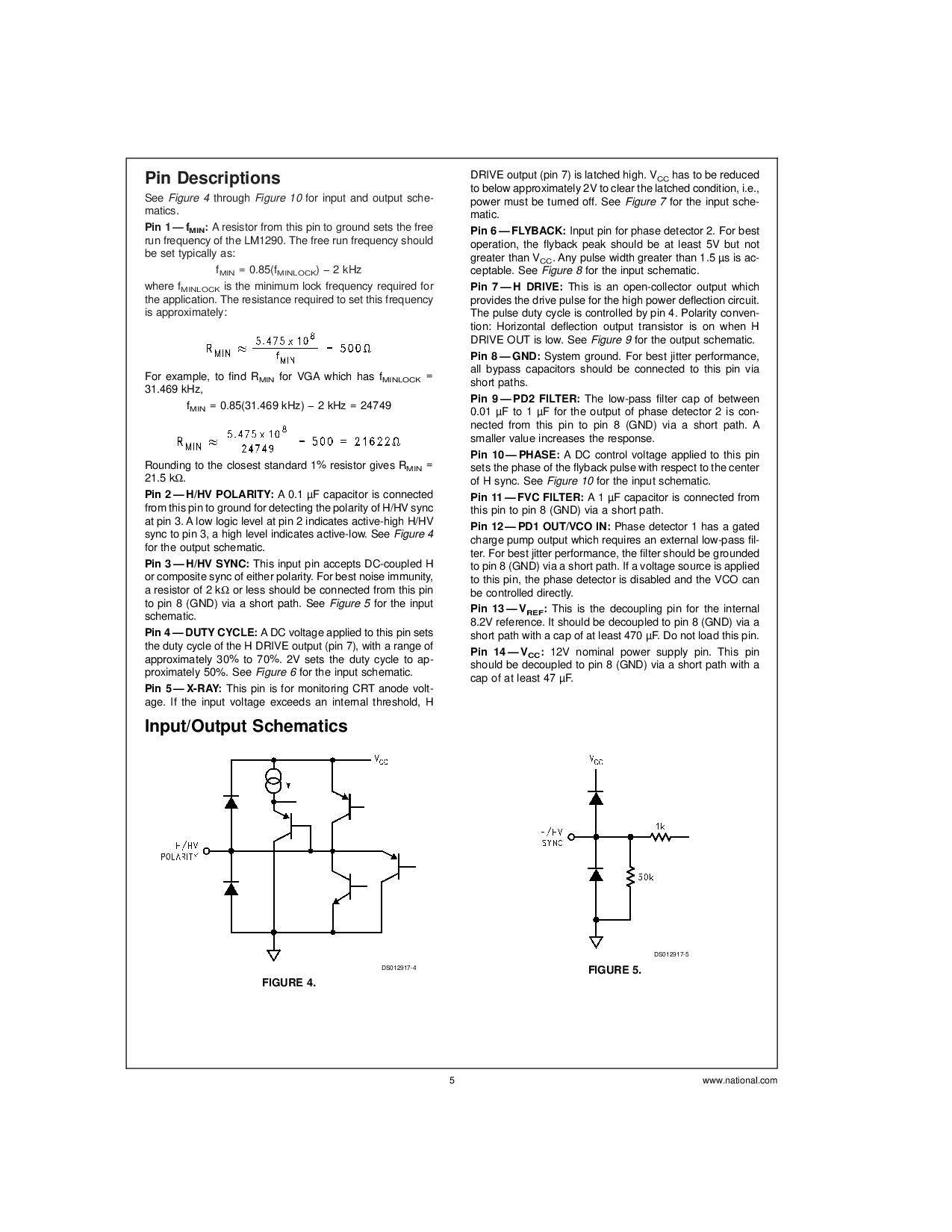

管脚 3 — h/hv 同步:

这个 输入 管脚 accepts 直流-结合 H

或者 composite 同步 的 也 极性. 为 最好的 噪音 免除,

一个 电阻 的 2 k

Ω

或者 较少 应当 是 连接 从 这个 管脚

至 管脚 8 (地) 通过 一个 短的 path. 看

图示 5

为 这 输入

图式.

管脚 4 — 职责 循环:

一个 直流 电压 应用 至 这个 管脚 sets

这 职责 循环 的 这 H 驱动 输出 (管脚 7), 和 一个 范围 的

大概 30

%

至 70

%

. 2V sets 这 职责 循环 至 ap-

proximately 50

%

. 看

图示 6

为 这 输入 图式.

管脚 5 — x-ray:

这个 管脚 是 为 monitoring CRT anode volt-

age. 如果 这 输入 电压 超过 一个 内部的 门槛, H

驱动 输出 (管脚 7) 是 latched 高. V

CC

有 至 是 减少

至 在下 大概 2V 至 clear 这 latched 情况, i.e.,

电源 必须 是 转变 止. 看

图示 7

为 这 输入 sche-

matic.

管脚 6 — flyback:

输入 管脚 为 阶段 探测器 2. 为 最好的

运作, 这 flyback 顶峰 应当 是 在 least 5V 但是 不

更好 比 V

CC

. 任何 脉冲波 宽度 更好 比 1.5 µs 是 交流-

ceptable. 看

图示 8

为 这 输入 图式.

管脚 7 — H 驱动:

这个 是 一个 打开-集电级 输出 这个

提供 这 驱动 脉冲波 为 这 高 电源 deflection 电路.

这 脉冲波 职责 循环 是 控制 用 管脚 4. 极性 conven-

tion: Horizontal deflection 输出 晶体管 是 在 当 H

驱动 输出 是 低. 看

图示 9

为 这 输出 图式.

管脚 8 — 地:

系统 地面. 为 最好的 jitter 效能,

所有 绕过 电容 应当 是 连接 至 这个 管脚 通过

短的 paths.

管脚 9 — PD2 过滤:

这 低-通过 过滤 cap 的 在

0.01 µF 至 1 µF 为 这 输出 的 阶段 探测器 2 是 con-

nected 从 这个 管脚 至 管脚 8 (地) 通过 一个 短的 path. 一个

小 值 增加 这 回馈.

管脚 10 — 阶段:

一个 直流 控制 电压 应用 至 这个 管脚

sets 这 阶段 的 这 flyback 脉冲波 和 遵守 至 这 中心

的 H 同步. 看

图示 10

为 这 输入 图式.

管脚 11 — FVC 过滤:

一个 1 µF 电容 是 连接 从

这个 管脚 至 管脚 8 (地) 通过 一个 短的 path.

管脚 12 — PD1 输出/vco 在:

阶段 探测器 1 有 一个 gated

承担 打气 输出 这个 需要 一个 外部 低-通过 fil-

ter. 为 最好的 jitter 效能, 这 过滤 应当 是 grounded

至 管脚 8 (地) 通过 一个 短的 path. 如果 一个 电压 源 是 应用

至 这个 管脚, 这 阶段 探测器 是 无能 和 这 VCO 能

是 控制 直接地.

管脚 13 — V

REF

:

这个 是 这 解耦 管脚 为 这 内部的

8.2v 涉及. 它 应当 是 decoupled 至 管脚 8 (地) 通过 一个

短的 path 和 一个 cap 的 在 least 470 µf. 做 不 加载 这个 管脚.

管脚 14 — V

CC

:

12V 名义上的 电源 供应 管脚. 这个 管脚

应当 是 decoupled 至 管脚 8 (地) 通过 一个 短的 path 和 一个

cap 的 在 least 47 µf.

输入/输出 Schematics

ds012917-4

图示 4.

ds012917-5

图示 5.

www.国家的.com5