CY7C006

CY7C016

8

注释:

19. BUSY

= 高 为 这 writing 端口.

20. CE

L

= ce

R

= 低.

21. 这 内部的 写 时间 的 这 记忆 是 定义 用 这 overlap 的 ce

或者 sem低 和 r/w低. 两个都 信号 必须 是 低 至 initiate 一个 写, 和 也 信号 能

terminate 一个 写 用 going 高. 这 数据 输入 设置-向上 和 支撑 定时 应当 是 关联 至 这 rising 边缘 的 这 信号 th在 terminates 这 写.

22. 如果 oe是 低 在 一个 r/w控制 写 循环, 这 写 脉冲波 宽度 必须 是 这 大 的 t

PWE

或者 (t

HZWE

+ t

SD

) 至 准许 这 i/o 驱动器 至 转变 止 和 数据 至 是 放置 在

这 总线 为 这 必需的 t

SD

. 如果 oe是 高 在 一个 r/w控制 写 循环 (作 在 这个 例子), 这个 必要条件 做 不 应用 和 这 写 脉冲波 能 是 作 短的 作 这

指定 t

PWE

.

23. r/w

必须 是 高 在 所有 地址 transitions.

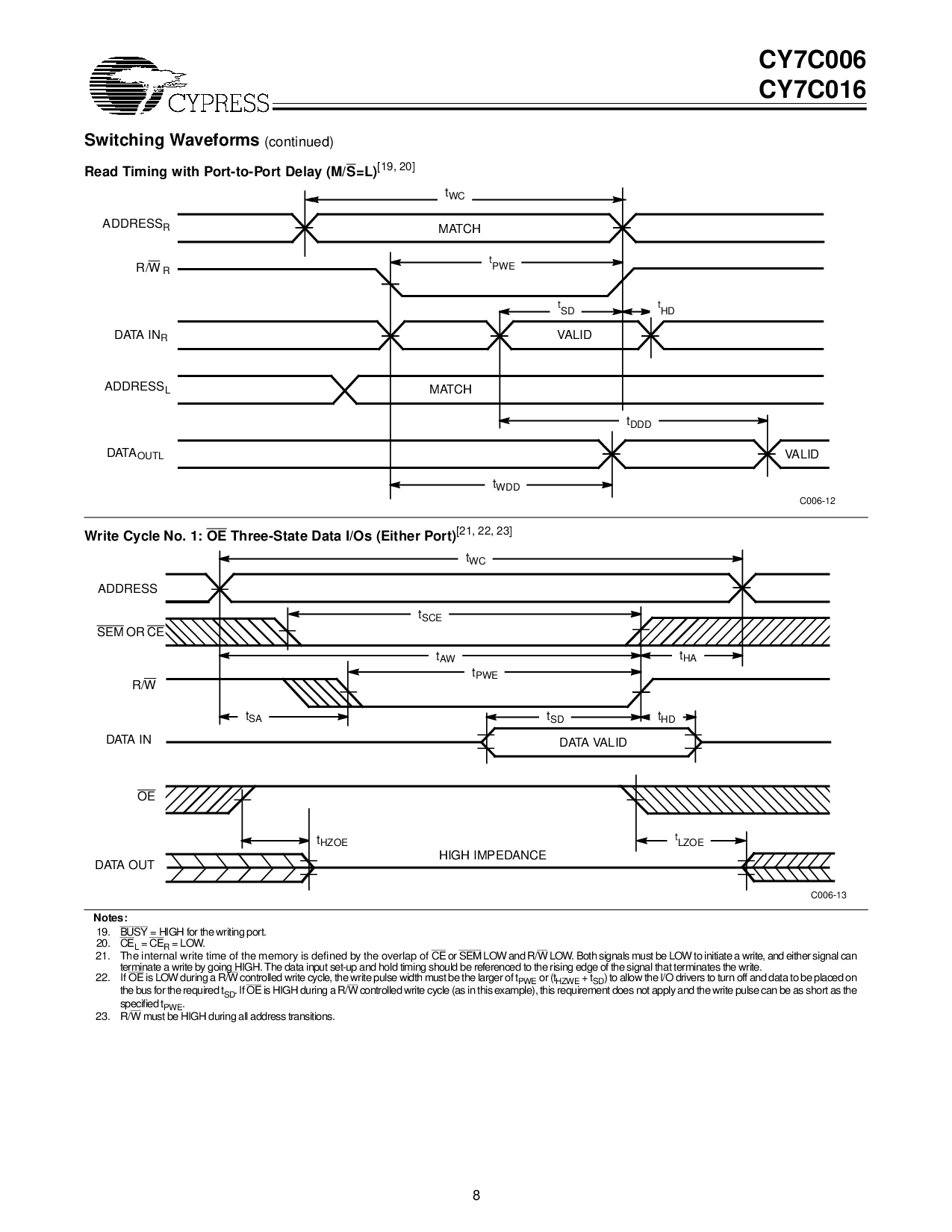

切换 波形

(持续)

VA LID

t

DDD

t

WDD

相一致

相一致

r/w

R

数据 在

R

数据

OUTL

c006-12

t

WC

地址

R

t

PWE

VA LID

t

SD

t

HD

地址

L

读 定时 和 端口-至-端口 延迟 (m/s=l)

[19, 20]

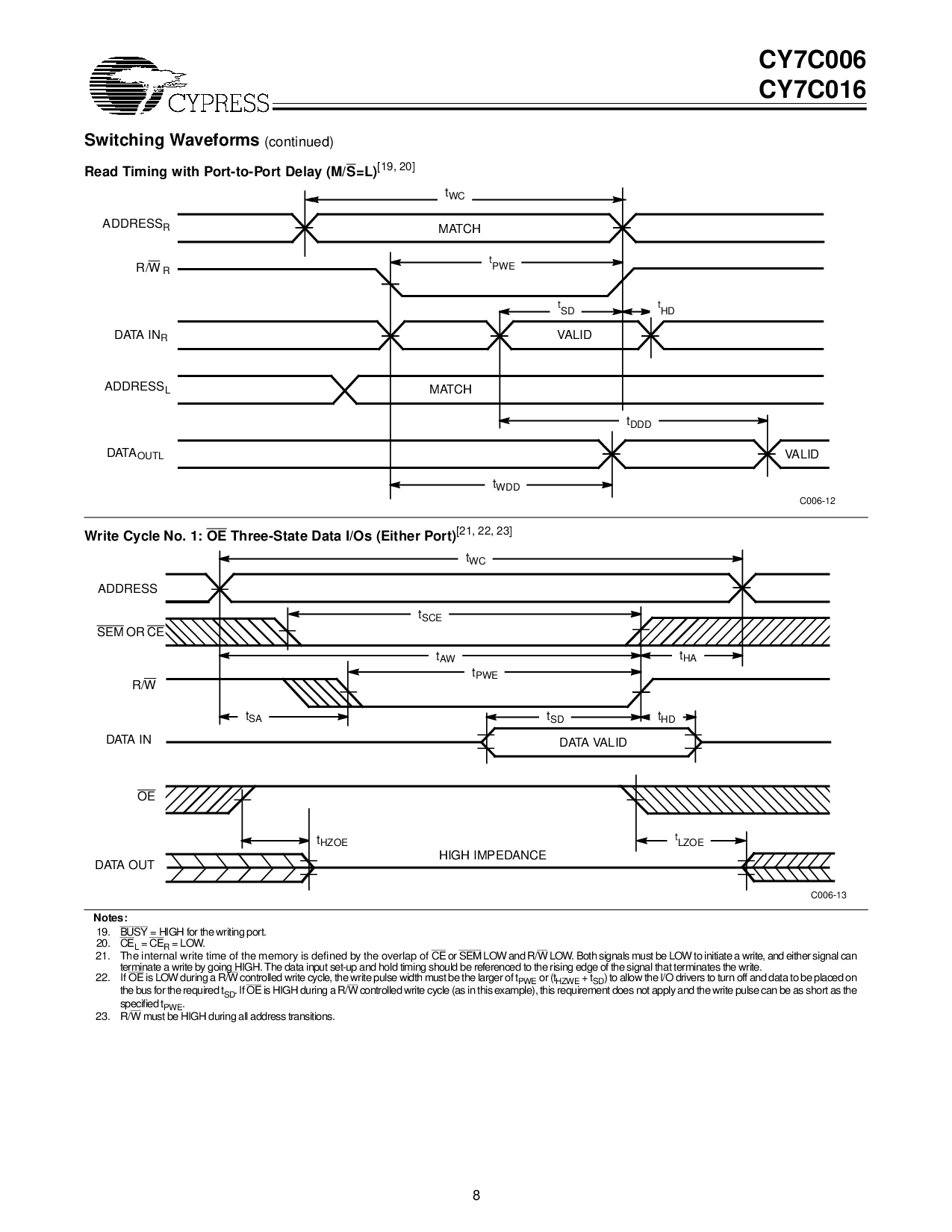

c006-13

t

AW

t

WC

数据 有效的

高 阻抗

t

SCE

t

SA

t

PWE

t

HD

t

SD

t

HA

t

HZOE

t

LZOE

SEM 或者 CE

r/w

地址

OE

数据 输出

数据 在

写 循环 非. 1: oe三-状态 数据 i/os (也 端口)

[21, 22, 23]