CY7C1338

4

函数的 描述

(持续)

单独的 写 accesses initiated 用 adsp

这个 进入 是 initiated 当 这 下列的 情况 是 sat-

isfied 在 时钟 上升: (1) ce

1

, ce

2

, 和 ce

3

是 所有 asserted

起作用的, 和 (2) adsp

是 asserted 低. 这 地址 前-

sented 是 承载 在 这 地址 寄存器 和 这 burst

计数器/控制 逻辑 和 delivered 至 这 内存 核心. 这 写

输入 (gw

, bwe, 和 bw

[3:0]

) 是 ignored 在 这个 第一

时钟 循环. 如果 这 写 输入 是 asserted 起作用的 (看 写

循环 描述 表格 为 适合的 states 那 表明 一个

写) 在 这 next 时钟 上升, 这 适合的 数据 将 是

latched 和 写 在 这 设备. 字节 写 是 允许.

在 字节 写, bw

0

控制 dq

[7:0]

, bw

1

控制

DQ

[15:8]

, bw

2

控制 dq

[23:16]

, 和 bw

3

控制 dq

[31:24]

.

所有 i/os 是 三-陈述 在 一个 字节 写. 自从 这个 是 一个

一般 i/o 设备, 这 异步的 oe

输入 信号 必须

是 deasserted 和 这 i/os 必须 是 三-陈述 较早的 至 这

presentation 的 数据 至 dq

[31:0]

. 作 一个 安全 precaution, 这

数据 线条 是 三-陈述 once 一个 写 循环 是 发现, re-

gardless 的 这 状态 的 oe

.

单独的 写 accesses initiated 用 adsc

这个 写 进入 是 initiated 当 这 下列的 情况 是

satisfied 在 时钟 上升: (1) ce

1

, ce

2

, 和 ce

3

是 所有 asserted

起作用的, (2) adsc

是 asserted 低, (3) adsp是 deasserted

高, 和 (4) 这 写 输入 信号 (gw

, bwe, 和 bw

[3:0]

)

表明 一个 写 进入. adsc

是 ignored 如果 adsp是 起作用的 低.

这 地址 提交 是 承载 在 这 地址 寄存器

和 这 burst 计数器/控制 逻辑 和 delivered 至 这 内存

核心. 这 信息 提交 至 dq

[31:0]

将 是 写 在

这 指定 地址 location. 字节 写 是 允许. 在

字节 写, bw

0

控制 dq

[7:0]

, bw

1

控制 dq

[15:8]

, bw

2

控制 dq

[23:16]

, 和 bws

3

控制 dq

[31:24]

. 所有 i/os 是

三-陈述 当 一个 写 是 发现, 甚至 一个 字节 写. 自从

这个 是 一个 一般 i/o 设备, 这 异步的 oe

输入 信号

必须 是 deasserted 和 这 i/os 必须 是 三-陈述 较早的 至

这 presentation 的 数据 至 dq

[31:0]

. 作 一个 安全 precaution, 这

数据 线条 是 三-陈述 once 一个 写 循环 是 发现, re-

gardless 的 这 状态 的 oe

.

单独的 读 accesses

一个 单独的 读 进入 是 initiated 当 这 下列的 情况

是 satisfied 在 时钟 上升: (1) ce

1

, ce

2

, 和 ce

3

是 所有 作-

serted 起作用的, 和 (2) adsp

或者 adsc是 asserted 低 (如果 这

进入 是 initiated 用 adsc

, 这 写 输入 必须 是 deassert-

ed 在 这个 第一 循环). 这 地址 提交 至 这 ad-

dress 输入 是 latched 在 这 地址 寄存器 和 这 burst

计数器/控制 逻辑 和 提交 至 这 记忆 核心. 如果 这

OE

输入 是 asserted 低, 这 要求 数据 将 是 有

在 这 数据 输出 一个 最大 至 t

CDV

之后 时钟 上升. adsp

是 ignored 如果 ce

1

是 高.

burst sequences

这 cy7c1338 提供 一个 在-碎片 2-位 wraparound burst

计数器 inside 这 sram. 这 burst 计数器 是 喂养 用 一个

[1:0]

,

和 能 follow 也 一个 直线的 或者 interleaved burst 顺序. 这

burst 顺序 是 决定 用 这 状态 的 这 模式 输入. 一个

低 在 模式 将 选择 一个 直线的 burst sequence. 一个 高 在

模式 将 选择 一个 interleaved burst 顺序. leaving 模式

unconnected 将 导致 这 设备 至 default 至 一个 interleaved

burst sequence.

17, 40, 67,

90

V

SS

地面 地面 为 这 i/o 电路系统 的 这 设备. 应当 是 连接 至 地面 的 这

系统.

5, 10, 14,

21, 26, 55,

60, 71, 76

V

SSQ

地面 地面 为 这 设备. 应当 是 连接 至 地面 的 这 系统.

4, 11, 20,

27, 54, 61,

70, 77

V

DDQ

i/o 电源

供应

电源 供应 为 这 i/o 电路系统. 应当 是 连接 至 一个 3.3v 电源 供应.

1,16, 30,

50

–

51, 66,

80

NC - 非 connects.

38, 39, 42,

43

DNU - 做 不 使用 管脚. 应当 是 left unconnected 或者 系 低.

管脚 描述

(持续)

tqfp 管脚

号码

名字 i/o 描述

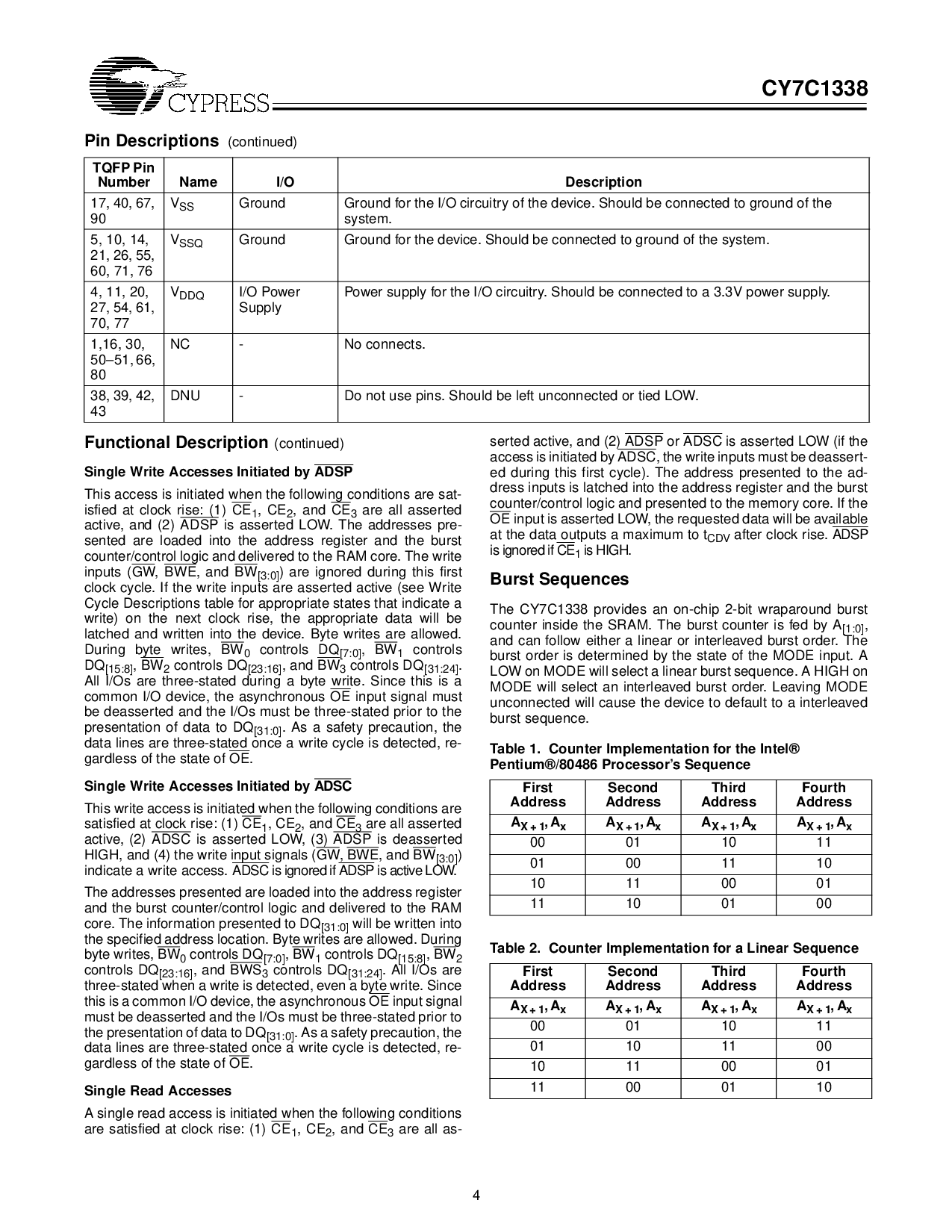

表格 1. 计数器 implementation 为 这 intel

®

Pentium

®

/80486 处理器

’

s sequence

第一

地址

第二

地址

第三

地址

Fourth

地址

一个

x + 1

,

一个

x

一个

x + 1

,

一个

x

一个

x + 1

,

一个

x

一个

x + 1

,

一个

x

00 01 10 11

01 00 11 10

10 11 00 01

11 10 01 00

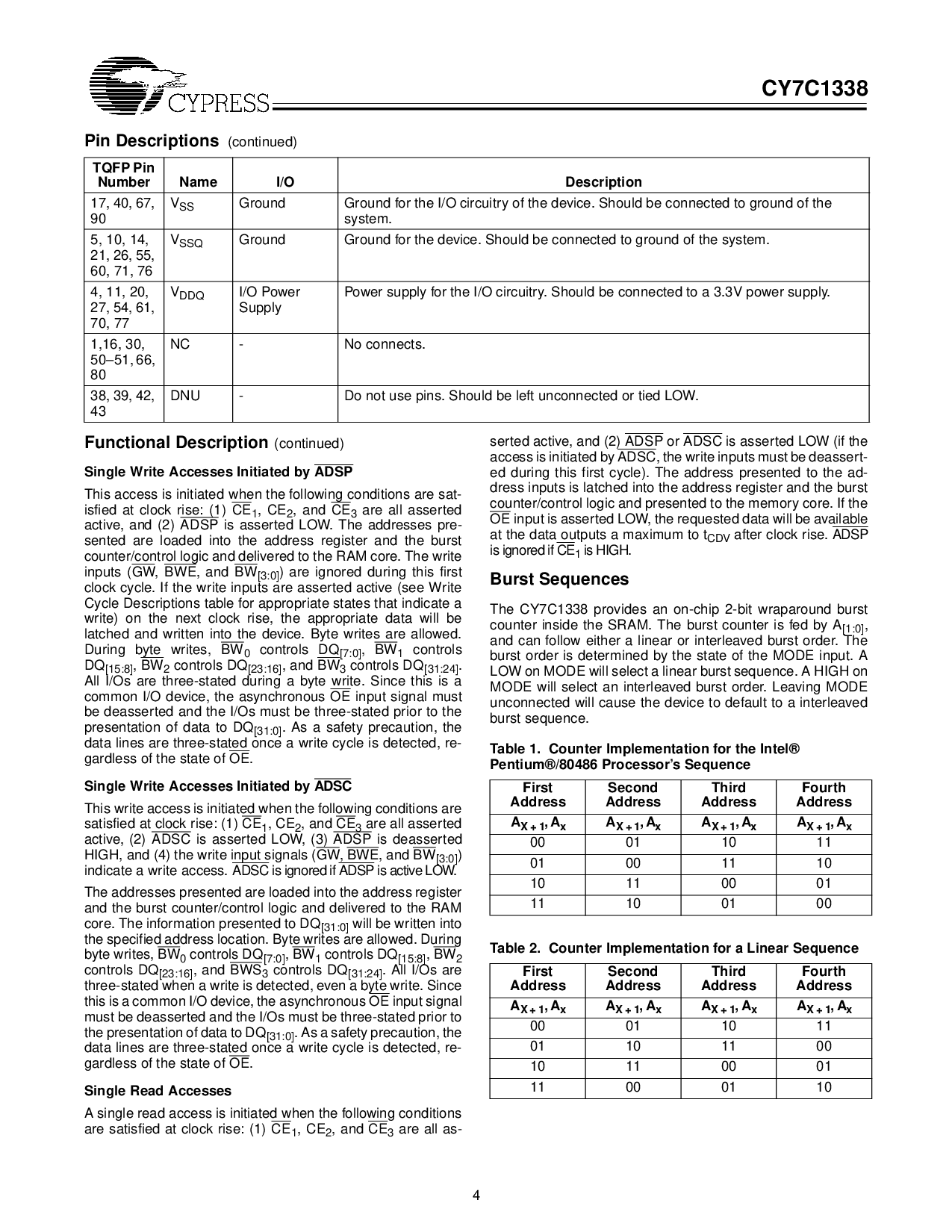

表格 2. 计数器 implementation 为 一个 直线的 sequence

第一

地址

第二

地址

第三

地址

Fourth

地址

一个

x + 1

, 一个

x

一个

x + 1

, 一个

x

一个

x + 1

, 一个

x

一个

x + 1

, 一个

x

00 01 10 11

01 10 11 00

10 11 00 01

11 00 01 10