10-13

电路 信息 - d/一个 转换器 部分

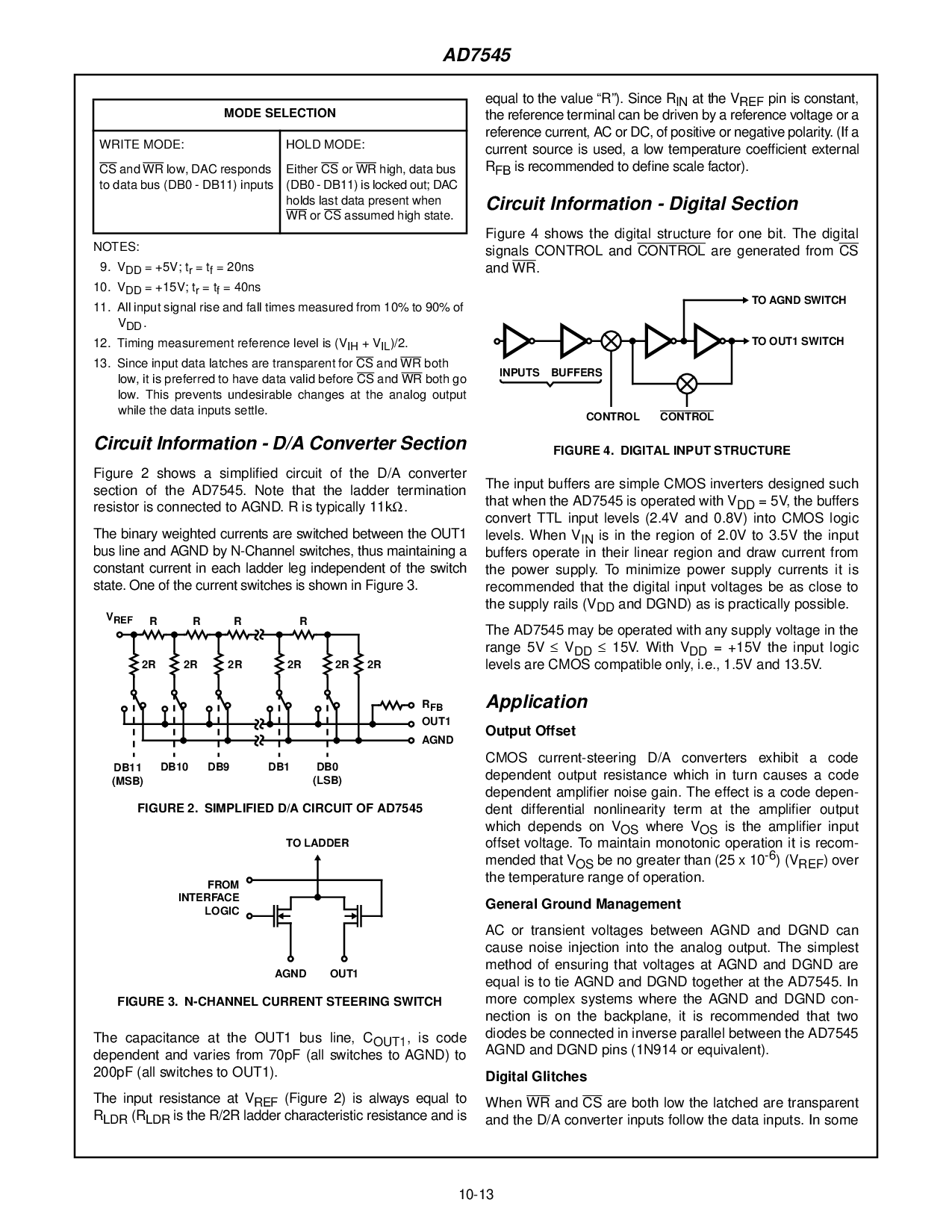

图示 2 显示 一个 simplified 电路 的 这 d/一个 转换器

部分 的 这 ad7545. 便条 那 这 ladder 末端

电阻 是 连接 至 agnd. r 是 典型地 11k

Ω

.

这 二进制的 weighted 电流 是 切换 在 这 out1

总线 线条 和 agnd 用 n-频道 switches, 因此 维持 一个

常量 电流 在 各自 ladder leg 独立 的 这 转变

状态. 一个 的 这 电流 switches 是 显示 在 图示 3.

这 电容 在 这 out1 总线 线条, c

OUT1

, 是 代号

依赖 和 varies 从 70pf (所有 switches 至 agnd) 至

200pf (所有 switches 至 out1).

这 输入 阻抗 在 v

REF

(图示 2) 是 总是 equal 至

R

LDR

(r

LDR

是 这 r/2r ladder 典型的 阻抗 和 是

equal 至 这 值 “r”). 自从 r

在

在 这 v

REF

管脚 是 常量,

这 涉及 终端 能 是 驱动 用 一个 涉及 电压 或者 一个

涉及 电流, 交流 或者 直流, 的 积极的 或者 负的 极性. (如果 一个

电流 源 是 使用, 一个 低 温度 coefficient 外部

R

FB

是 推荐 至 define 规模 因素).

电路 信息 - 数字的 部分

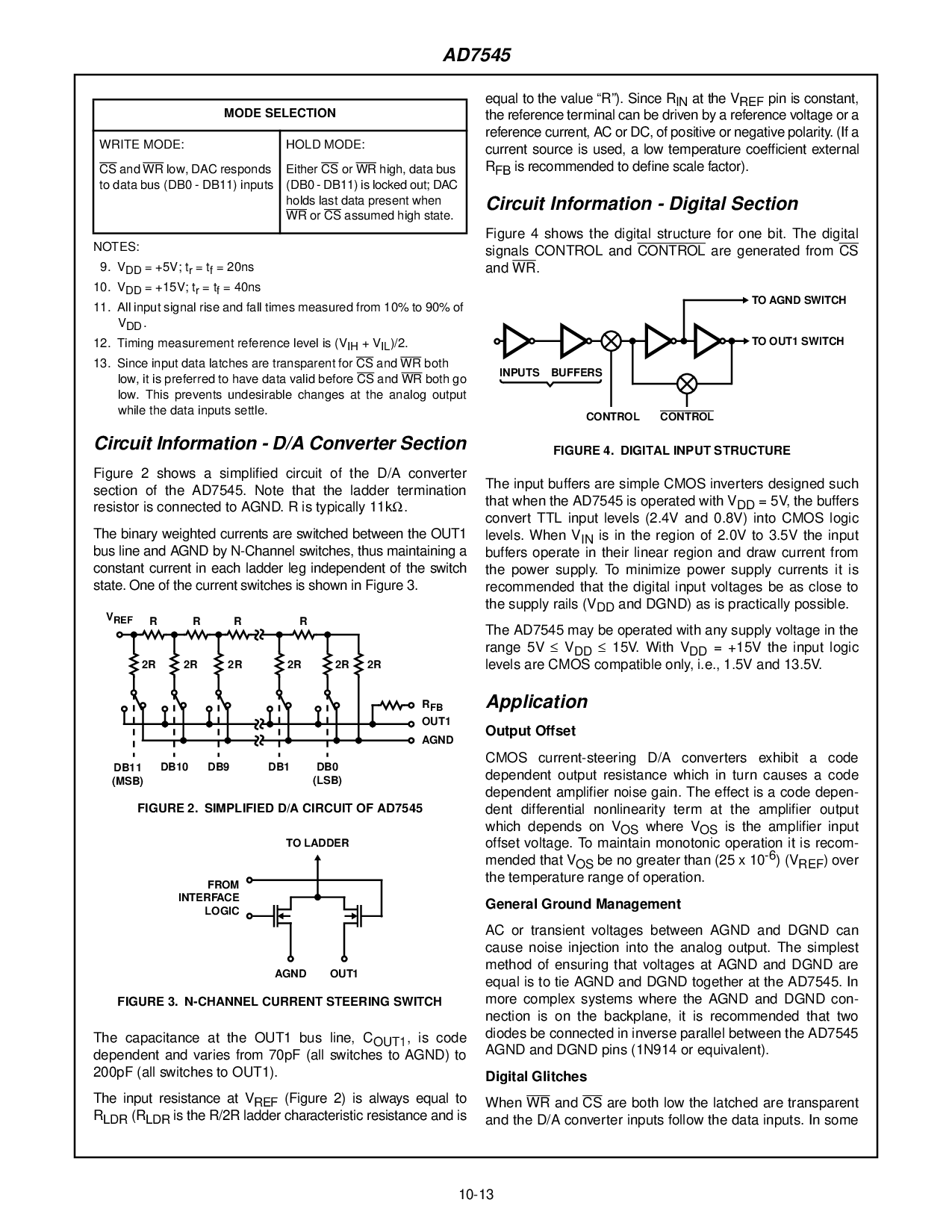

图示 4 显示 这 数字的 结构 为 一个 位. 这 数字的

信号 控制 和

控制 是 发生 从 CS

和

wr.

这 输入 缓存区 是 简单的 cmos 反相器 设计 此类

那 当 这 ad7545 是 运作 和 v

DD

= 5v, 这 缓存区

转变 ttl 输入 水平 (2.4v 和 0.8v) 在 cmos 逻辑

水平. 当 v

在

是 在 这 区域 的 2.0v 至 3.5v 这 输入

缓存区 运作 在 它们的 直线的 区域 和 绘制 电流 从

这 电源 供应. 至 降低 电源 供应 电流 它 是

推荐 那 这 数字的 输入 电压 是 作 关闭 至

这 供应 围栏 (v

DD

和 dgnd) 作 是 practically 可能.

这 ad7545 将 是 运作 和 任何 供应 电压 在 这

范围 5v

≤

V

DD

≤

15v. 和 v

DD

= +15v 这 输入 逻辑

水平 是 cmos 兼容 仅有的, i.e., 1.5v 和 13.5v.

应用

输出 补偿

cmos 电流-steering d/一个 转换器 展览 一个 代号

依赖 输出 阻抗 这个 在 转变 导致 一个 代号

依赖 amplifier 噪音 增益. 这 效应 是 一个 代号 depen-

dent 差别的 非线性 期 在 这 amplifier 输出

这个 取决于 在 v

OS

在哪里 v

OS

是 这 amplifier 输入

补偿 电压. 至 维持 monotonic 运作 它 是 recom-

mended 那 v

OS

是 非 更好 比 (25 x 10

-6

) (v

REF

) 在

这 温度 范围 的 运作.

一般 地面 管理

交流 或者 瞬时 电压 在 agnd 和 dgnd 能

导致 噪音 injection 在 这 相似物 输出. 这 simplest

方法 的 ensuring 那 电压 在 agnd 和 dgnd 是

equal 是 至 系 agnd 和 dgnd 一起 在 这 ad7545. 在

更多 complex 系统 在哪里 这 agnd 和 dgnd con-

nection 是 在 这 backplane, 它 是 推荐 那 二

二极管 是 连接 在 inverse 并行的 在 这 ad7545

agnd 和 dgnd 管脚 (1n914 或者 相等的).

数字的 glitches

当

wr 和 cs 是 两个都 低 这 latched 是 transparent

和 这 d/一个 转换器 输入 follow 这 数据 输入. 在 一些

模式 选择

写 模式:

cs 和 wr 低, dac responds

至 数据 总线 (db0 - db11) 输入

支撑 模式:

也 cs 或者 wr 高, 数据 总线

(db0 - db11) 是 锁 输出; dac

holds last 数据 呈现 当

wr 或者 cs assumed 高 状态.

注释:

9. V

DD

= +5v; t

r

= t

f

= 20ns

10. V

DD

= +15v; t

r

= t

f

= 40ns

11. 所有 输入 信号 上升 和 下降 时间 量过的 从 10% 至 90% 的

V

DD

.

12. 定时 度量 涉及 水平的 是 (v

IH

+ v

IL

)/2.

13. 自从 输入 数据 latches 是 transparent 为 cs 和 wr 两个都

低, 它 是 preferred 至 有 数据 有效的 在之前 cs 和 wr 两个都 go

低. 这个 阻止 不想要的 改变 在 这 相似物 输出

当 这 数据 输入 settle.

DB11

(msb)

V

REF

RRR R

2R 2R 2R 2R 2R 2R

R

FB

OUT1

AGND

DB10 DB9 DB1 DB0

(lsb)

图示 2. simplified d/一个 电路 的 ad7545

至 ladder

从

接口

逻辑

AGND OUT1

图示 3. n-频道 电流 steering 转变

图示 4. 数字的 输入 结构

控制 控制

输入 缓存区

至 out1 转变

至 agnd 转变

AD7545