数据手册

9

155 Mbps sdh/sonet/atm Transceiver — LXT6155

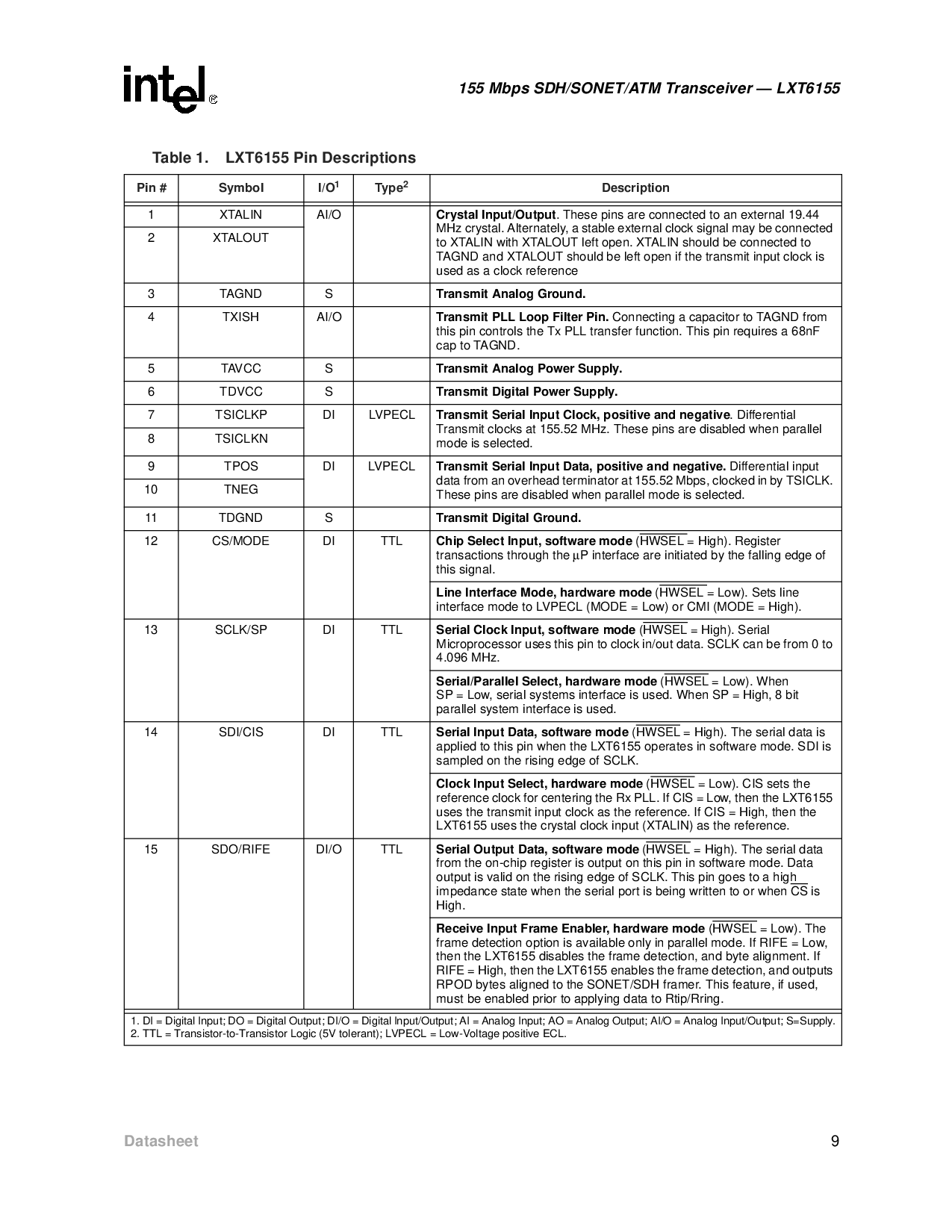

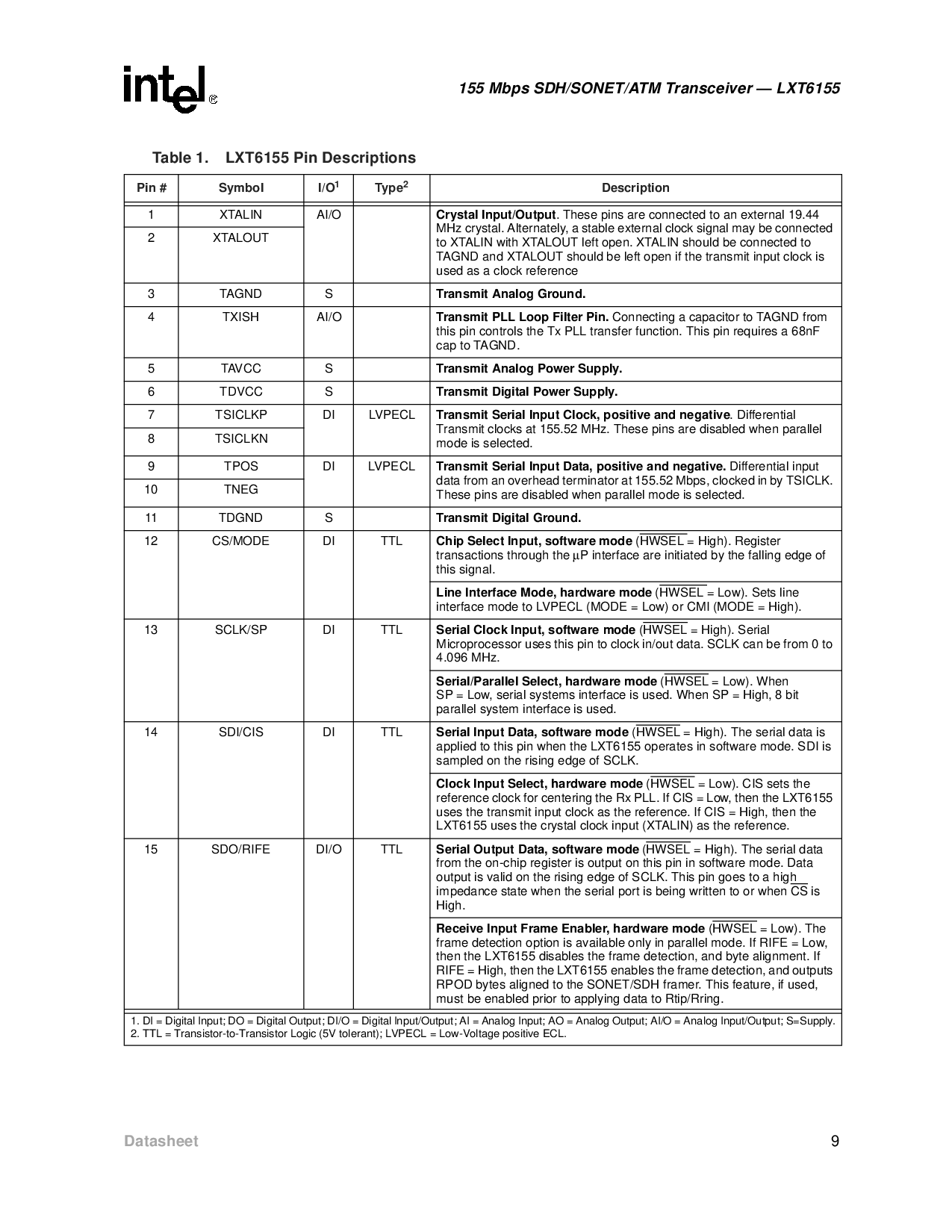

表格 1. LXT6155 管脚 描述

管脚 # 标识 i/o

1

典型值e

2

描述

1 XTALIN ai/o

结晶 输入/输出

. 这些 管脚 是 连接 至 一个 外部 19.44

MHz 结晶. alternately, 一个 稳固的 外部 时钟 信号 将 是 连接

至 XTALIN 和 XTALOUT left 打开. XTALIN 应当 是 连接 至

TAGND 和 XTALOUT 应当 是 left 打开 如果 这 transmit 输入 时钟 是

使用 作 一个 时钟 涉及

2XTALOUT

3TAGNDS

Transmit 相似物 地面.

4 TXISH ai/o

Transmit PLL 循环 过滤 管脚.

连接 一个 电容 至 TAGND 从

这个 管脚 控制 这 Tx PLL 转移 函数. 这个 管脚 需要 一个 68nF

captotagnd.

5TAVCCS

Transmit 相似物 电源 供应.

6 TDVCC S

Transmit 数字的 电源 供应.

7 TSICLKP DI LVPECL

Transmit 串行 输入 时钟, 积极的 和 负的

. 差别的

Transmit clocks 在 155.52 mhz. 这些 管脚 是 无能 当 并行的

模式 是 选择.

8 TSICLKN

9 TPOS DI LVPECL

Transmit 串行 输入 数据, 积极的 和 负的.

差别的 输入

数据 从 一个 overhead terminator 在 155.52 mbps, clocked 在 用 tsiclk.

这些 管脚 是 无能 当 并行的 模式 是 选择.

10 TNEG

11 TDGND S

Transmit 数字的 地面.

12 cs/模式 DI TTL

碎片 选择 输入, 软件 模式

(hwsel

= 高). 寄存器

transactions 通过 这

µ

P 接口 是 initiated 用 这 下落 边缘 的

这个 信号.

线条 接口 模式, 硬件 模式

(hwsel

=低).setsline

interfacemodetolvpecl(模式=低)orcmi(模式=高).

13 sclk/sp DI TTL

串行 时钟 输入, 软件 模式

(hwsel

= 高). 串行

微处理器 使用 这个 管脚 至 时钟 在/输出 数据. SCLK 能 是 从 0 至

4.096 mhz.

串行/并行的 选择, 硬件 模式

(hwsel

=低).当

SP = 低, 串行 系统 接口 是 使用. 当 SP = 高, 8 位

并行的 系统 接口 是 使用.

14 sdi/cis DI TTL

串行 输入 数据, 软件 模式

(hwsel

= 高). 这 串行 数据 是

应用 至 这个 管脚 当 这 LXT6155 运作 在 软件 模式. SDI 是

抽样 在 这 rising 边缘 的 sclk.

时钟 输入 选择, 硬件 模式

(hwsel

= 低). CIS sets 这

涉及 时钟 为 centering 这 Rx pll. 如果 CIS = 低, 然后 这 LXT6155

使用 这 transmit 输入 时钟 作 这 涉及. 如果 CIS = 高, 然后 这

LXT6155 使用 这 结晶 时钟 输入 (xtalin) 作 这 涉及.

15 sdo/rife di/o TTL

串行 输出 数据, 软件 模式

(hwsel

= 高). 这 串行 数据

从 这 在-碎片 寄存器 是 输出 在 这个 管脚 在 软件 模式. 数据

输出 是 有效的 在 这 rising 边缘 的 sclk. 这个 管脚 变得 至 一个 高

阻抗 状态 当 这 串行 端口 是 正在 写 至 或者 当 CS

是

高.

Receive 输入 框架 enabler, 硬件 模式

(hwsel

= 低). 这

框架 发现 选项 是 有 仅有的 在 并行的 模式. 如果 RIFE = 低,

然后 这 LXT6155 使不能运转 这 框架 发现, 和 字节 排成直线. 如果

RIFE = 高, 然后 这 LXT6155 使能 这 框架 发现, 和 输出

RPOD 字节 排整齐 至 这 sonet/sdh framer. 这个 特性, 如果 使用,

必须 是 使能 较早的 至 应用 数据 至 rtip/rring.

1. DI = 数字的 输入; 做 = 数字的 输出; di/o = 数字的 输入/输出; AI = 相似物 输入; AO = 相似物 输出; ai/o = 相似物 输入/输出; s=供应.

2. TTL = 晶体管-至-晶体管 逻辑 (5v tolerant); LVPECL = 低-电压 积极的 ecl.