cs5161, cs5161h

http://onsemi.com

7

–

+

–

+

–

+

V

CC1

SS

V

ID0

V

ID1

V

ID2

V

ID3

V

ID4

V

FFB

低

比较器

V

FFB

快 反馈

LGnd

慢 反馈

PWM

比较器

ss 低

比较器

ss 高

比较器

5 位

DAC

V

CC1

监控

比较器

错误

放大器

V

CC1

V

CC2

C

止

V

门(h)

V

门(l)

PGnd

故障

故障

故障

获得

PGnd

R

S

Q

Q

R

S

Q

Q

R

S

Q

获得

PMW

C

止

一个 shot

止

–

时间

Timeout

时间

–

输出

计时器

边缘 triggered

扩展

止

–

时间

Timeout

正常的

止

–

时间

Timeout

最大

在

–

时间

Timeout

(30

µ

s)

门(h) = 在

门(h) = 止

2.0

µ

一个

60

µ

一个

5.0 v

0.7 v

2.5 v

1.0 v

–

+

–

+

+

–

9.05 v

8.90v

V

FB

竞赛

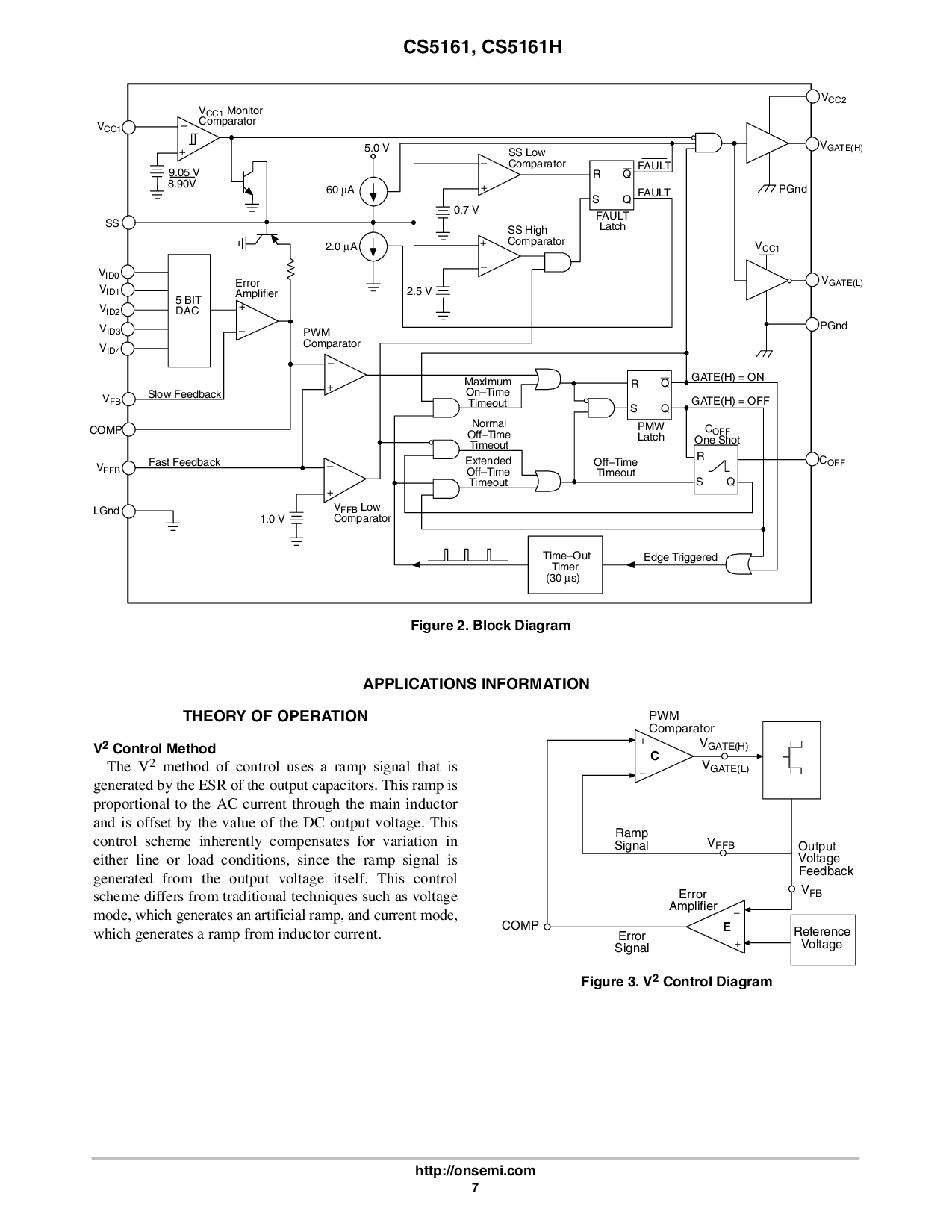

图示 2. 块 图解

产品 信息

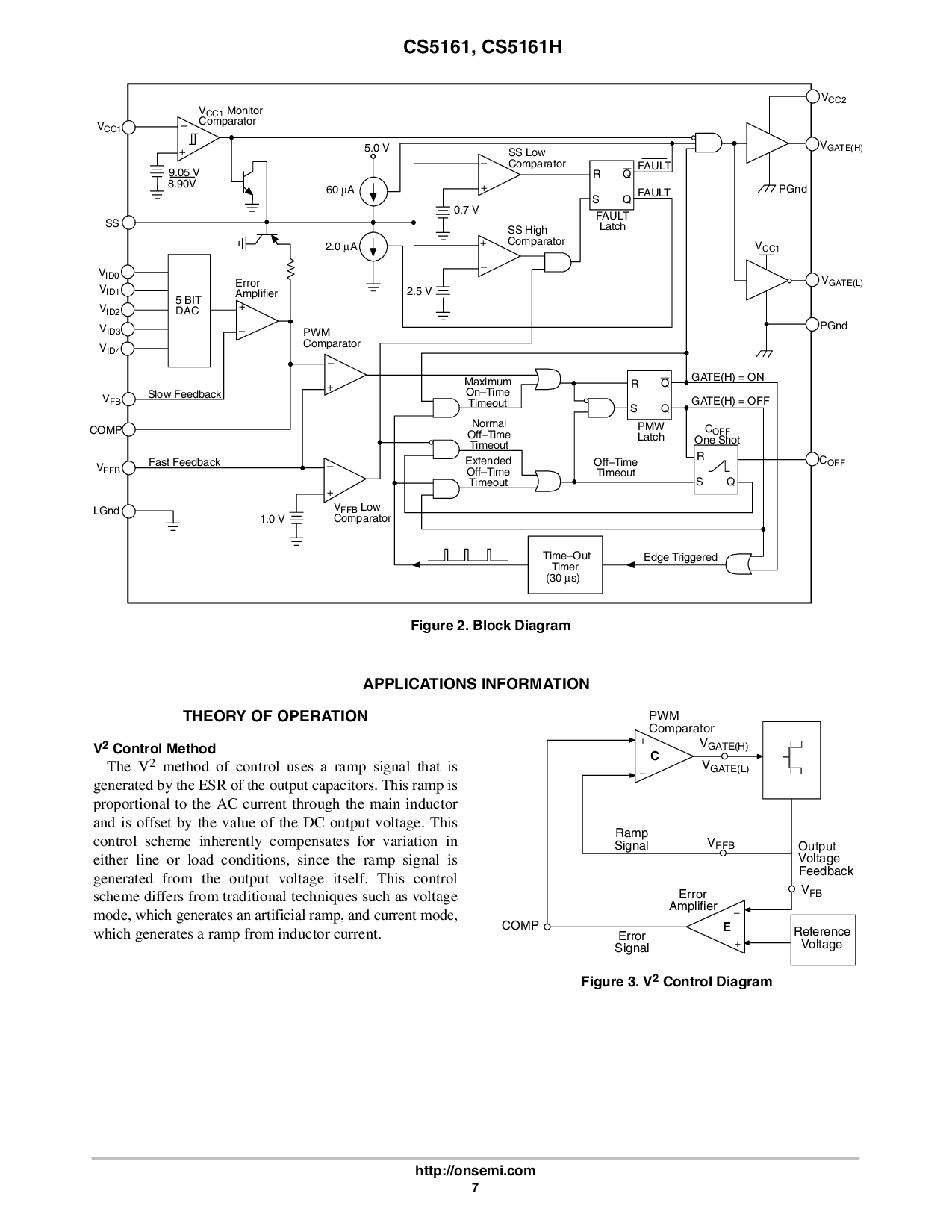

theory 的 运作

V

2

控制 方法

这 v

2

方法 的 控制 使用 一个 ramp 信号 那 是

发生 用这 等效串联电阻 的 这 输出 电容. 这个 ramp 是

均衡的 至 这 交流 电流 通过 这 主要的 inductor

和 是 补偿 用 这 值 的 这 直流 输出 电压. 这个

控制 scheme 本质上 compensates 为 变化 在

也 线条 或者 加载 情况, 自从 这 ramp 信号 是

发生 从 这 输出 电压 它自己. 这个 控制

scheme differs 从 传统的 技巧 此类 作 电压

模式,这个 发生 一个 artificial ramp, 和 电流 模式,

这个 发生 一个 ramp 从 inductor 电流.

图示 3. v

2

控制 图解

竞赛

V

FFB

涉及

电压

+

+

PWM

比较器

Ramp

信号

错误

放大器

错误

信号

输出

电压

反馈

V

FB

V

门(h)

V

门(l)

E

C

–

–