8

LTC1603

1603f

APPLICATIONs iN为MATION

WUU

U

转换 详细信息

这 ltc1603 使用 一个 successive approximation algorithm

和 内部的 样本-和-支撑 电路 至 转变 一个 相似物

信号 至 一个 16-位 并行的 输出. 这 模数转换器 是 完全 和

一个 样本-和-支撑, 一个 精确 涉及 和 一个 内部的

时钟. 这 控制 逻辑 提供 容易 接口 至 微观的-

processors 和 dsps. (请 谈及 至 这 数字的 接口

部分 为 这 数据 format.)

转换 开始 是 控制 用 这 cs 和 convst

输入. 在 这 开始 的 这 转换 这 successive

approximation 寄存器 (sar) resets. once 一个 转换

循环 有 begun 它 不能 是 restarted.

在 这 转换, 这 内部的 差别的 16-位

电容的 dac 输出 是 sequenced 用 这 sar 从 这

大多数 重大的 位 (msb) 至 这 least 重大的 位

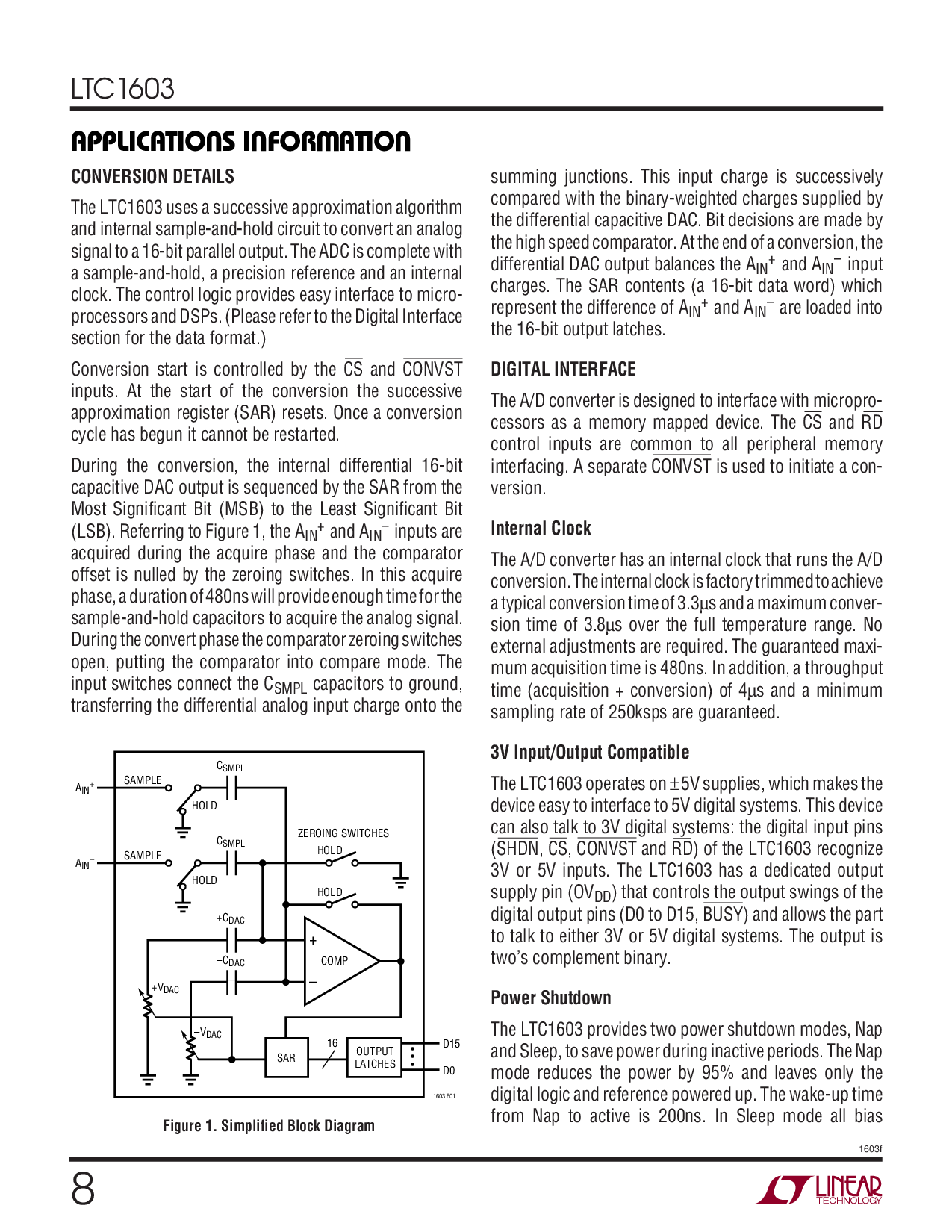

(lsb). referring 至 图示 1, 这 一个

在

+

和 一个

在

–

输入 是

acquired 在 这 acquire 阶段 和 这 比较器

补偿 是 nulled 用 这 zeroing switches. 在 这个 acquire

阶段, 一个 持续时间 的 480ns 将 提供 足够的 时间 为 这

样本-和-支撑 电容 至 acquire 这 相似物 信号.

在 这 转变 阶段 这 比较器 zeroing switches

打开, putting 这 比较器 在 对比 模式. 这

输入 switches 连接 这 c

SMPL

电容 至 地面,

transferring 这 差别的 相似物 输入 承担 面向 这

图示 1. simplified 块 图解

summing 汇合处. 这个 输入 承担 是 successively

对照的 和 这 二进制的-weighted charges 有提供的 用

这 差别的 电容的 dac. 位 decisions 是 制造 用

这 高 速 比较器. 在 这 终止 的 一个 转换, 这

差别的 dac 输出 balances 这 一个

在

+

和 一个

在

–

输入

charges. 这 sar 内容 (一个 16-位 数据 文字) 这个

代表 这 区别 的 一个

在

+

和 一个

在

–

是 承载 在

这 16-位 输出 latches.

数字的 接口

这 一个/d 转换器 是 设计 至 接口 和 micropro-

cessors 作 一个 记忆 编排 设备. 这 cs 和 rd

控制 输入 是 一般 至 所有 附带的 记忆

接合. 一个 独立的 convst 是 使用 至 initiate 一个 con-

版本.

内部的 时钟

这 一个/d 转换器 有 一个 内部的 时钟 那 runs 这 一个/d

转换. 这 内部的 时钟 是 工厂 修整 至 达到

一个 典型 转换 时间 的 3.3

µ

s 和 一个 最大 变换器-

sion 时间 的 3.8

µ

s 在 这 全部 温度 范围. 非

外部 adjustments 是 必需的. 这 有保证的 maxi-

mum acquisition 时间 是 480ns. 在 增加, 一个 throughput

时间 (acquisition + 转换) 的 4

µ

s 和 一个 最小

抽样 比率 的 250ksps 是 有保证的.

3v 输入/输出 兼容

这 ltc1603 运作 在

±

5v 供应, 这个 制造 这

设备 容易 至 接口 至 5v 数字的 系统. 这个 设备

能 也 表达 至 3v 数字的 系统: 这 数字的 输入 管脚

(shdn, cs, convst 和 rd) 的 这 ltc1603 认识

3v 或者 5v 输入. 这 ltc1603 有 一个 专心致志的 输出

供应 管脚 (ov

DD

) 那 控制 这 输出 swings 的 这

数字的 输出 管脚 (d0 至 d15, busy) 和 准许 这 部分

至 表达 至 也 3v 或者 5v 数字的 系统. 这 输出 是

二’s complement 二进制的.

电源 关闭

这 ltc1603 提供 二 电源 关闭 模式, nap

和 睡眠, 至 保存 电源 在 inactive 时期. 这 nap

模式 减少 这 电源 用 95% 和 leaves 仅有的 这

数字的 逻辑 和 涉及 powered 向上. 这 wake-向上 时间

从 nap 至 起作用的 是 200ns. 在 睡眠 模式 所有 偏差

–

+

竞赛

一个

在

+

C

SMPL

支撑

样本

一个

在

–

C

SMPL

+C

DAC

+V

DAC

–C

DAC

–V

DAC

支撑

支撑

样本

支撑

SAR

输出

LATCHES

16

D15

D0

1603 f01

•

•

•

zeroing switches