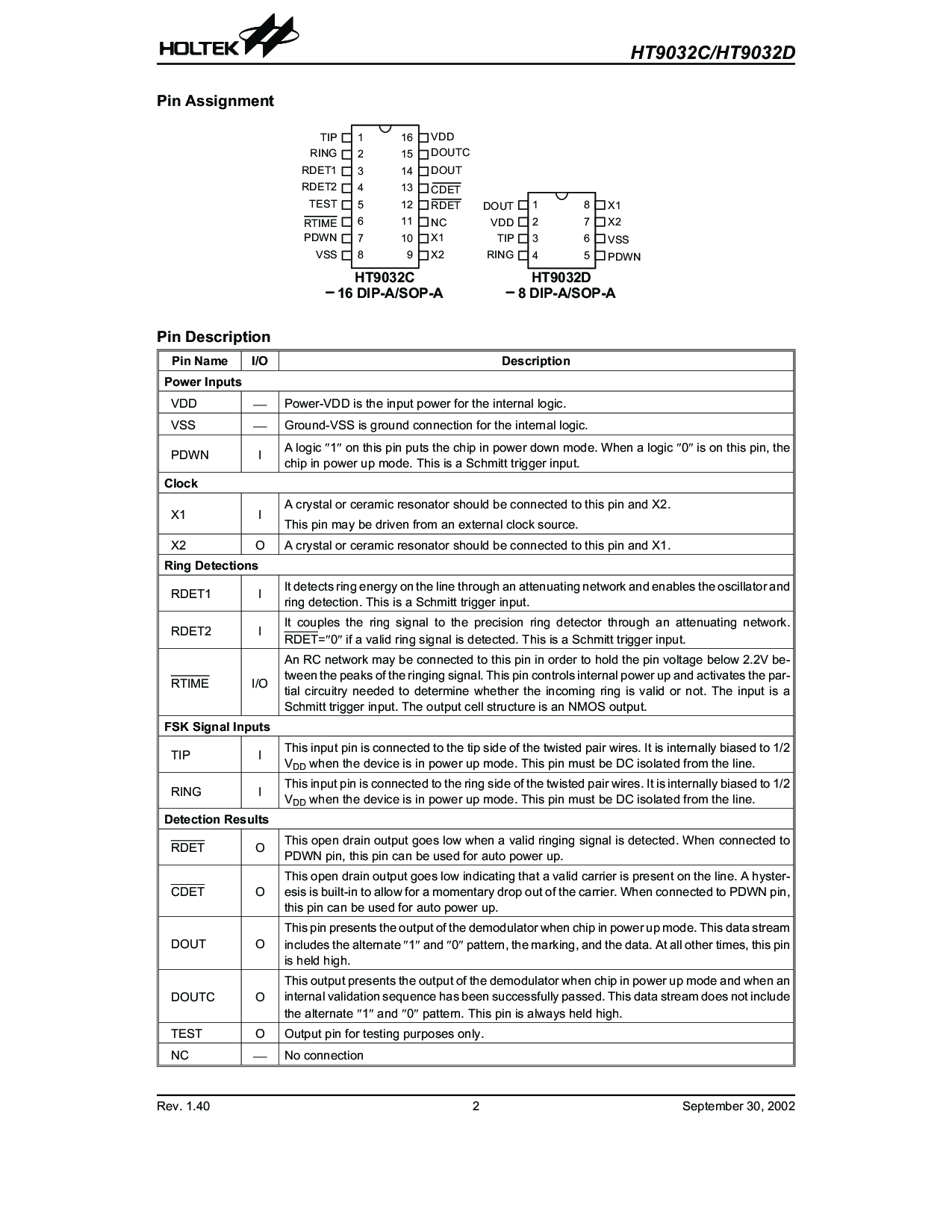

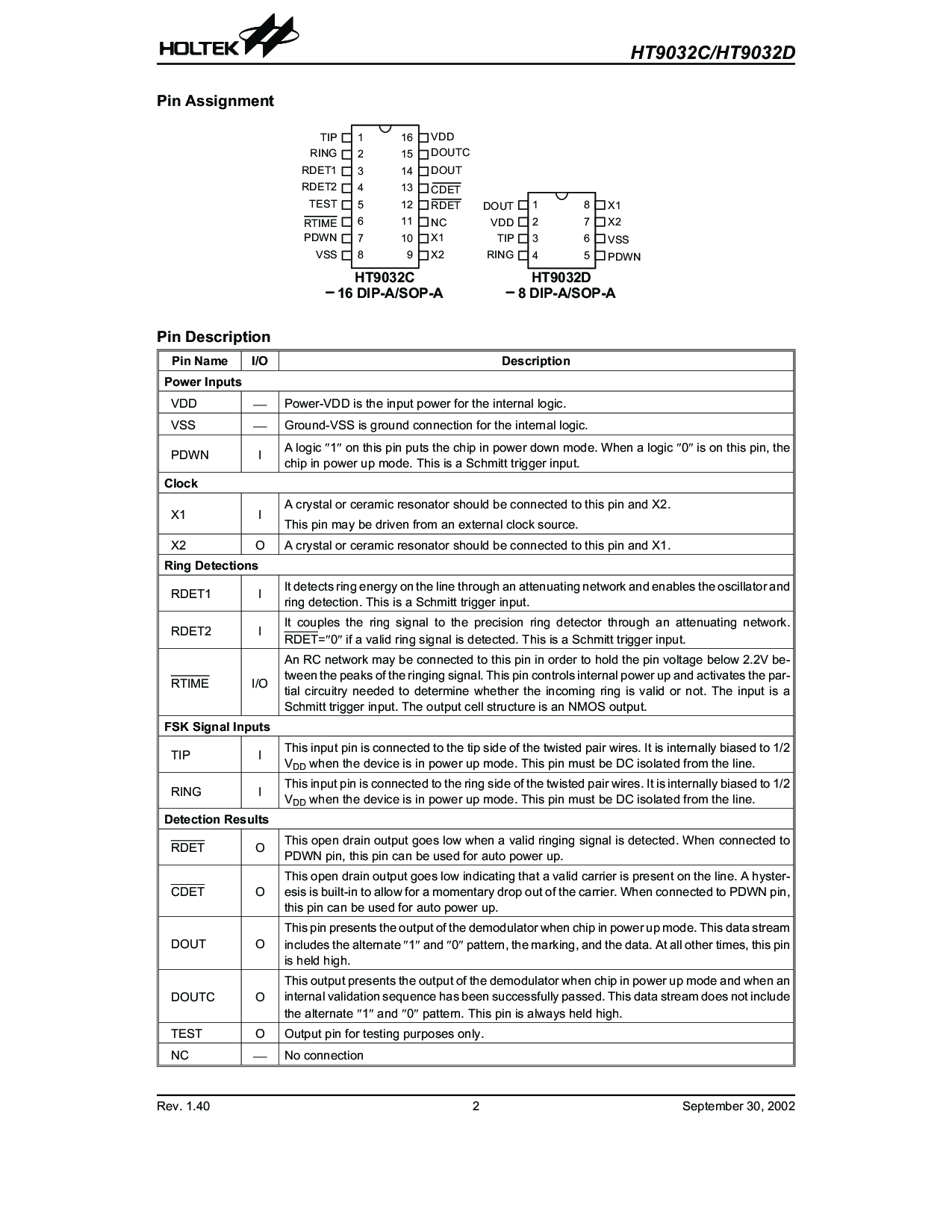

管脚 分派

管脚 描述

管脚 名字 i/o 描述

电源 输入

VDD

电源-vdd 是 这 输入 电源 为 这 内部的 逻辑.

VSS

地面-vss 是 地面 连接 为 这 内部的 逻辑.

PDWN I

一个 逻辑

1

在 这个 管脚 puts 这 碎片 在 电源 向下 模式. 当 一个 逻辑

0

是 在 这个 管脚, 这

碎片 在 电源 向上 模式. 这个 是 一个 施密特 触发 输入.

时钟

X1 I

一个 结晶 或者 陶瓷的 共振器 应当 是 连接 至 这个 管脚 和 x2.

这个 管脚 将 是 驱动 从 一个 外部 时钟 源.

X2 O 一个 结晶 或者 陶瓷的 共振器 应当 是 连接 至 这个 管脚 和 x1.

环绕 Detections

RDET1 I

它 发现 环绕 活力 在 这 线条 通过 一个 attenuating 网络 和 使能 这 振荡器 和

环绕 发现. 这个 是 一个 施密特 触发 输入.

RDET2 I

它 couples 这 环绕 信号 至 这 精确 环绕 探测器 通过 一个 attenuating 网络.

RDET

=

0

如果 一个 有效的 环绕 信号 是 发现. 这个 是 一个 施密特 触发 输入.

RTIME

i/o

一个 RC 网络 将 是 连接 至 这个 管脚 在 顺序 至 支撑 这 管脚 电压 在下 2.2v 是-

tween 这 顶峰 的 这 ringing 信号. 这个 管脚 控制 内部的 电源 向上 和 activates 这 par-

tial 电路系统 需要 至 决定 whether 这 新当选的 环绕 是 有效的 或者 不. 这 输入 是 一个

施密特 触发 输入. 这 输出 cell 结构 是 一个 NMOS 输出.

FSK 信号 输入

TIP I

这个 输入 管脚 是 连接 至 这 tip 一侧 的 这 twisted 一双 线. 它 是 内部 片面的 至 1/2

V

DD

当 这 设备 是 在 电源 向上 模式. 这个 管脚 必须 是 直流 分开的 从 这 线条.

环绕 I

这个 输入 管脚 是 连接 至 这 环绕 一侧 的 这 twisted 一双 线. 它 是 内部 片面的 至 1/2

V

DD

当 这 设备 是 在 电源 向上 模式. 这个 管脚 必须 是 直流 分开的 从 这 线条.

发现 结果

RDET

O

这个 打开 流 输出 变得 低 当 一个 有效的 ringing 信号 是 发现. 当 连接 至

PDWN 管脚, 这个 管脚 能 是 使用 为 自动 电源 向上.

CDET

O

这个 打开 流 输出 变得 低 表明 那 一个 有效的 运输车 是 呈现 在 这 线条. 一个 hyster

-

esis 是 建造-在 至 准许 为 一个 momentary 漏出 输出 的 这 运输车. 当 连接 至 PDWN 管脚,

这个 管脚 能 是 使用 为 自动 电源 向上.

DOUT O

这个 管脚 presents 这 输出 的 这 demodulator 当 碎片 在 电源 向上 模式. 这个 数据 stream

包含 这 alternate

1

和

0

模式, 这 标记, 和 这 数据. 在 所有 其它 时间, 这个 管脚

是 使保持 高.

DOUTC O

这个 输出 presents 这 输出 的 这 demodulator 当 碎片 在 电源 向上 模式 和 当 一个

内部的 validation sequence 有 被 successfully passed. 这个 数据 stream 做 不 包含

这 alternate

1

和

0

模式. 这个 管脚 是 总是 使保持 高.

测试 O 输出 管脚 为 测试 目的 仅有的.

NC

非 连接

ht9032c/ht9032d

rev. 1.40 2 九月 30, 2002