3

工业的 温度 范围

QS5919

低 skew cmos pll 时钟 驱动器 和 整体的 循环 过滤

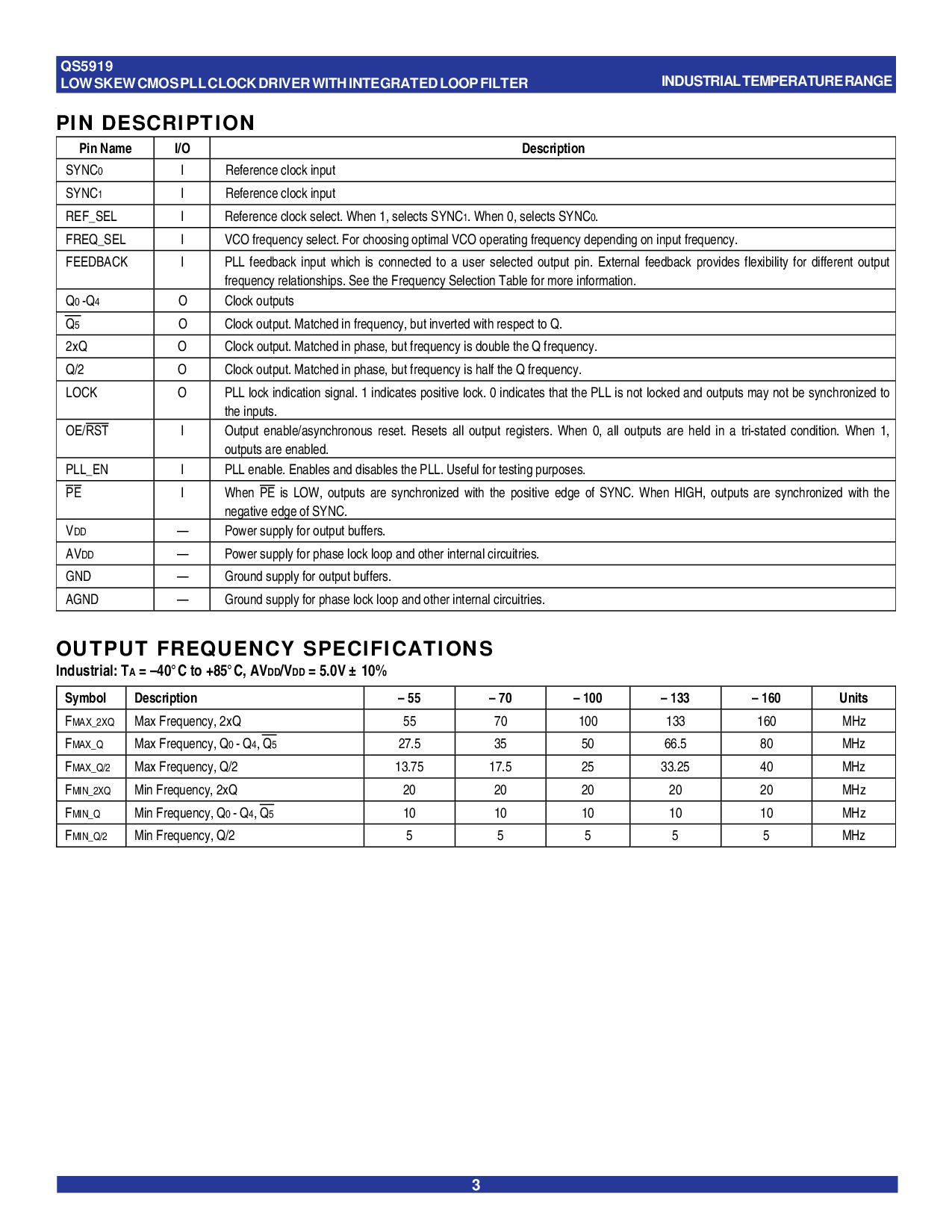

管脚 描述

管脚 名字 i/o 描述

同步

0

I 涉及 时钟 输入

同步

1

I 涉及 时钟 输入

ref_sel I 涉及 时钟 选择. 当 1, 选择 同步

1

. 当 0, 选择 同步

0

.

freq_sel I vco 频率 选择. 为 choosing 最优的 vco 运行 频率 取决于 在 输入 频率.

反馈 I pll 反馈 输入 这个是 连接 至 一个 用户 选择ed 输出 管脚. 外部 反馈提供 flexibility 为 different 输出

频率 relationships. 看 这 频率 选择 表格 为 更多 信息.

Q

0

-q

4

O 时钟 输出

Q

5

O 时钟 输出. matched 在 频率, 但是 inverted 和 遵守 至 q.

2xQ O 时钟 输出. matched 在 阶段, 但是 频率 是 翻倍 这 q 频率.

q/2 O 时钟 输出. matched 在 阶段, 但是 频率 是 half 这 q 频率.

锁 O pll 锁 indication 信号. 1 indicates 积极的 锁. 0 indicates 那 这 pll 是 不 锁 和 输出 将 不 是 synchronized 至

这 输入.

oe/

RST

I 输出 使能/异步的 重置. resets 所有 输出 寄存器. 当 0, 所有 输出 是 使保持 在 一个 tri-stated condition. 当 1,

输出 是 使能.

pll_en I pll 使能. 使能 和 使不能运转 这 pll. 有用的 为 测试 目的.

PE

I 当

PE

是 低, 输出 是 同步 和 这 积极的 边缘 的 同步. 当 高, 输出 是 同步 和 这

负的 边缘 的 同步.

V

DD

— 电源 供应 为 输出 缓存区.

AV

DD

— 电源 供应 为 阶段 锁 循环 和 其它 内部的 circuitries.

地 — 地面 供应 为 输出 缓存区.

AGND — 地面 供应 为 阶段 锁 循环 和 其它 内部的 circuitries.

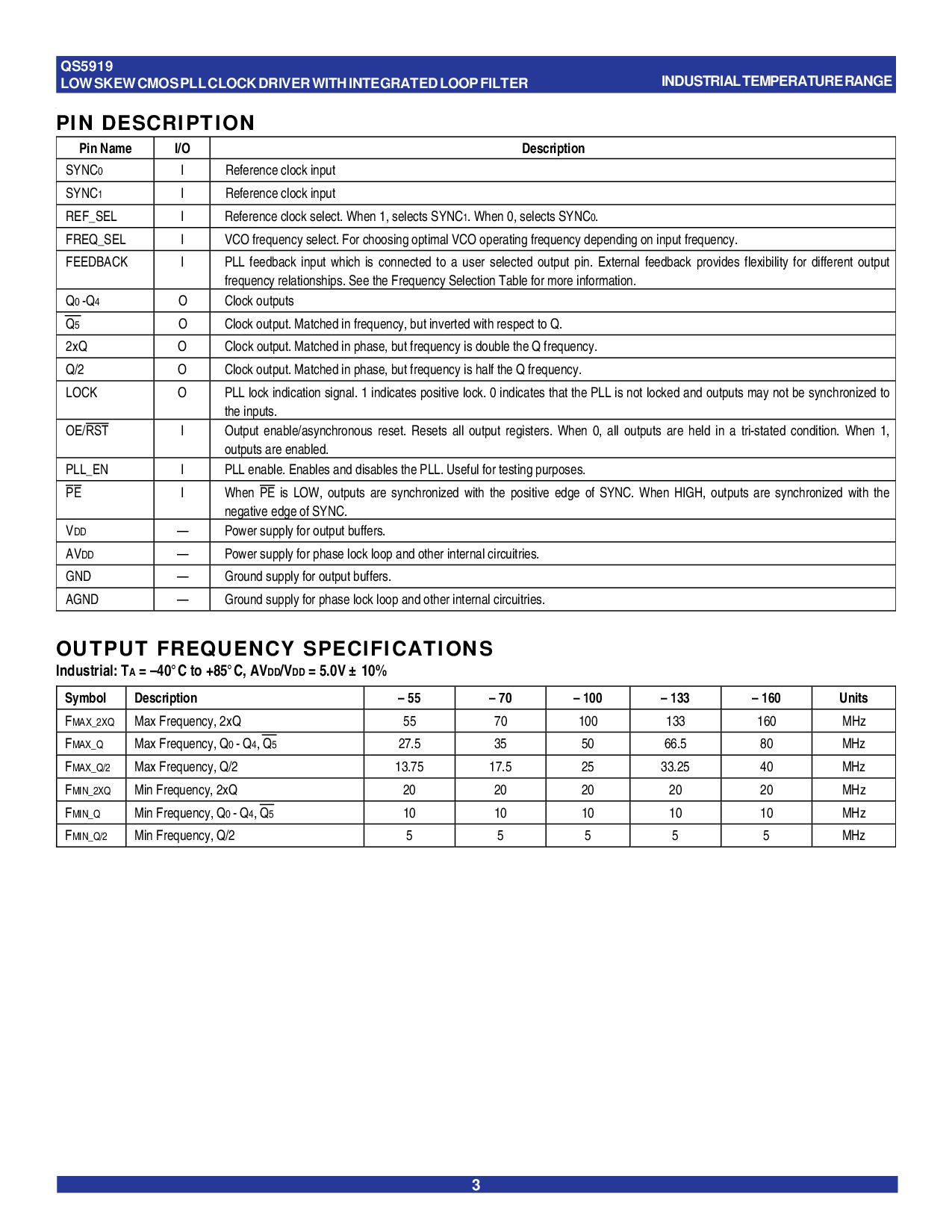

输出 频率 规格

工业的: t

一个

= –40°c 至 +85°c, av

DD

/v

DD

= 5.0v ± 10%

标识 描述 – 55 – 70 – 100 – 133 – 160 单位

F

最大值_2xq

最大值 频率, 2xq 55 70 100 133 160 MHz

F

最大值_q

最大值 频率, q

0

- q

4

, q

5

27.5 35 50 66.5 80 MHz

F

最大值_q/2

最大值 频率, q/2 13.75 17.5 25 33.25 40 MHz

F

最小值_2xq

最小值 频率, 2xq 20 20 20 20 20 MHz

F

最小值_q

最小值 频率, q

0

- q

4

, q

5

10 10 10 10 10 MHz

F

最小值_q/2

最小值 频率, q/2 5 5 5 5 5 MHz