PreliminaryW91031

发行 释放 日期: 8月 2000

-11-修订 a1

模式 0

(模式 = 低):

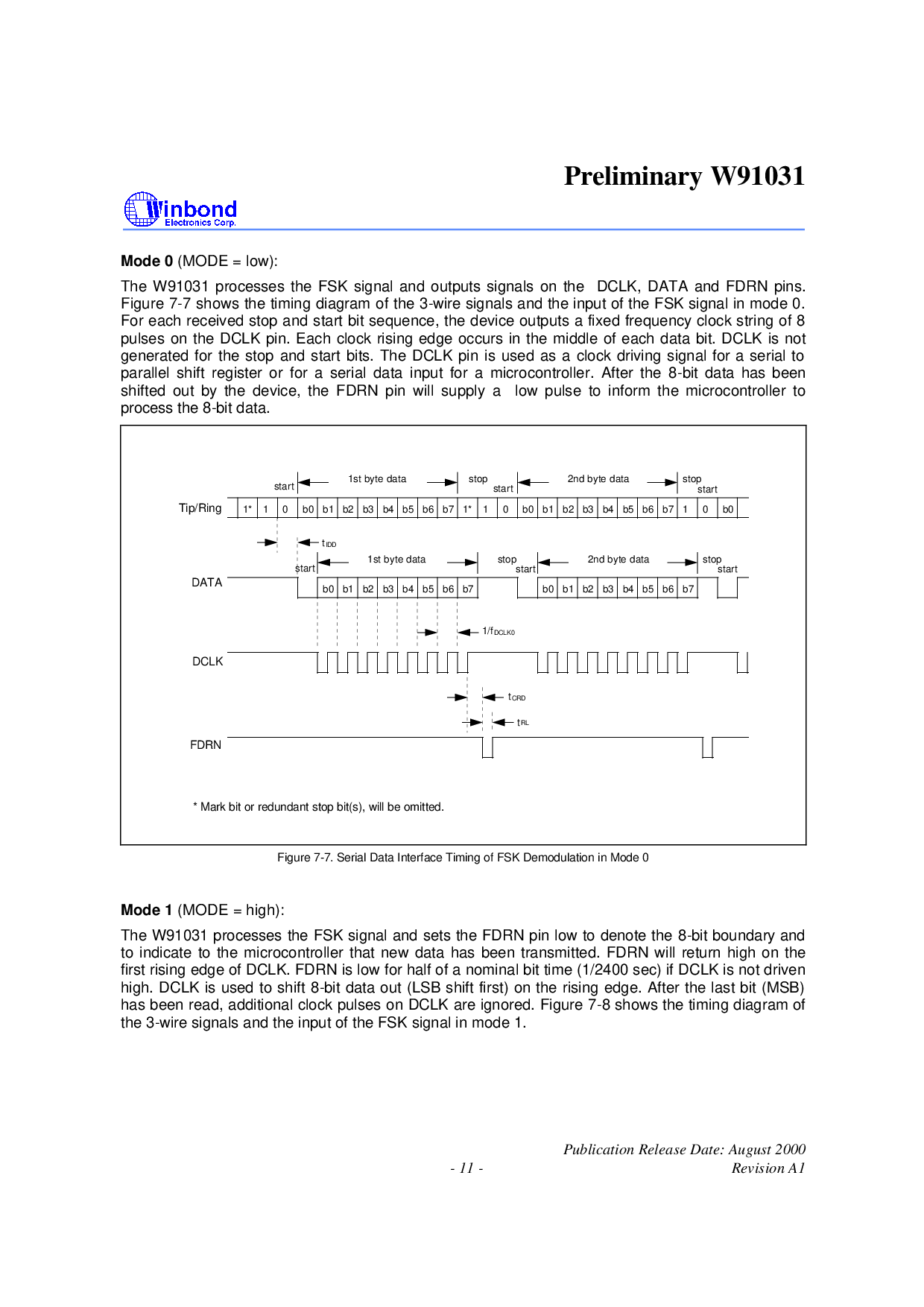

这 w91031 处理 这 fsk 信号 和 输出 信号 在 这 dclk, 数据 和 fdrn 管脚.

图示 7-7 显示 这 定时 图解 的 这 3-线 信号 和 这 输入 的 这 fsk 信号 在 模式 0.

为 各自 received 停止 和 start 位 sequence, 这 设备 输出 一个 fixed 频率 时钟 string 的 8

脉冲 在 这 dclk 管脚. 各自 时钟 rising 边缘 occurs 在 这 middle 的 各自 数据 位. dclk 是 不

发生 为 这 停止 和 开始 位. 这 dclk 管脚 是 使用 作 一个 时钟 驱动 signal 为 一个 串行 至

并行的 变换 寄存器 或者 为 一个 串行 数据 输入 为 一个 微控制器. 之后 这 8-位 数据 有 被

shifted 输出 用 这 设备, 这 fdrn 管脚 将 供应 一个 低 脉冲波 至 inform 这 微控制器 至

处理 这 8-位 数据.

tip/环绕

1* 1 0 b0 b1 b2

开始

b3 b4 b5 b6 b7 1* 0 b0 b1 b2 b3 b4 b5 b6 b7 11 0 b0

停止

开始

停止

开始

数据

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

开始

停止

开始

停止

开始

t

IDD

DCLK

FDRN

1/f

DCLK0

t

CRD

t

RL

1st 字节 数据 2nd 字节 数据

1st 字节 数据 2nd 字节 数据

* mark 位 或者 redundant 停止 位(s), 将 是 omitted.

图示 7-7. 串行 数据 接口 定时 的 fsk demodulation 在 模式 0

模式 1

(模式 = 高):

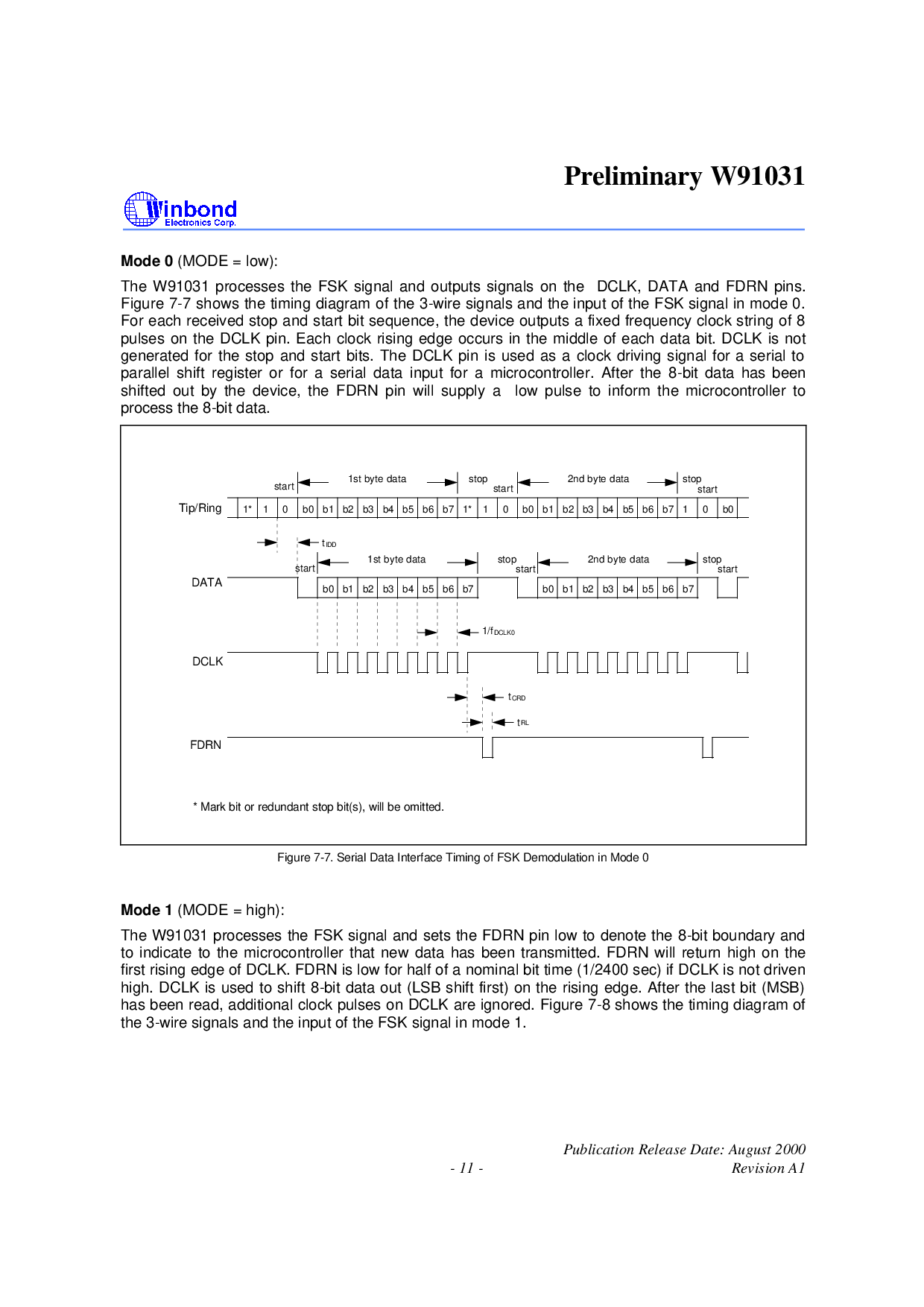

这 w91031 处理 这 fsk 信号 和 sets 这 fdrn 管脚 低 至 denote 这 8-位 boundary 和

至 表明 至 这 微控制器 那 新 数据 有 被transmitted. fdrn 将 返回 高 在 这

第一 rising 边缘 的 dclk. fdrn 是 低 为 half 的 一个 名义上的 位 时间 (1/2400 秒) 如果 dclk 是 不 驱动

高. dclk 是 使用 至 变换 8-位 数据 输出 (lsb 变换 第一) 在 这 rising 边缘. 之后 这 last 位 (msb)

has 被 读, 额外的 时钟 脉冲 在 dclk 是 ignored. 图示 7-8 显示 这 定时 图解 的

这 3-线 信号 和 这 输入 的 这 fsk 信号 在 模式 1.