CS8552

century 半导体 公司

页 6 的 23

pixel 输入/输出 定时

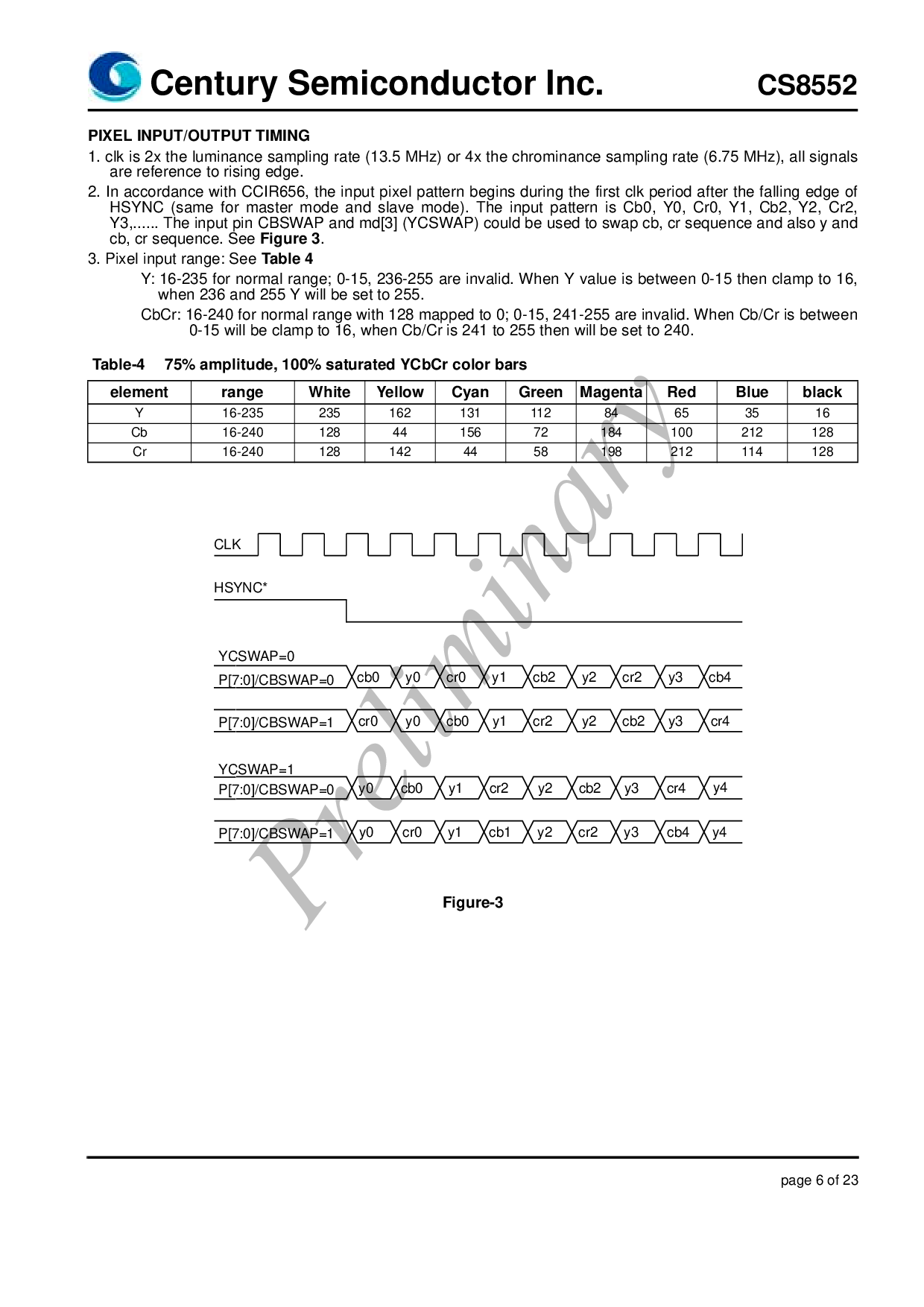

1. clk 是 2x 这 luminance 抽样 比率 (13.5 mhz) 或者 4x 这 chrominance 抽样 比率 (6.75 mhz), 所有 信号

是 涉及 至 rising 边缘.

2. 在 一致 和 ccir656, 这 输入 pixel 模式 begins 在 这 第一 clk 时期 之后 这 下落 边缘 的

hsync (一样 为 主控 模式 和 从动装置 模式). 这 输入 模式 是 cb0, y0, cr0, y1, cb2, y2, cr2,

y3,...... 这 输入 管脚 cbswap 和 md[3] (ycswap) 可以 是 使用 至 swap cb, cr sequence 和 也 y 和

cb, cr sequence. 看

图示 3

.

3. pixel 输入 范围: 看

Table 4

y: 16-235 为 正常的 范围; 0-15, 236-255 是 invalid. 当 y 值 是 在 0-15 然后 clamp 至 16,

当 236 和 255 y 将 是 设置 至 255.

cbcr: 16-240 为 正常的 范围 和 128 编排 至 0; 0-15, 241-255 是 invalid. 当 cb/cr 是 在

0-15 将 是 clamp 至 16, 当 cb/cr 是 241 至 255 然后 将 是 设置 至 240.

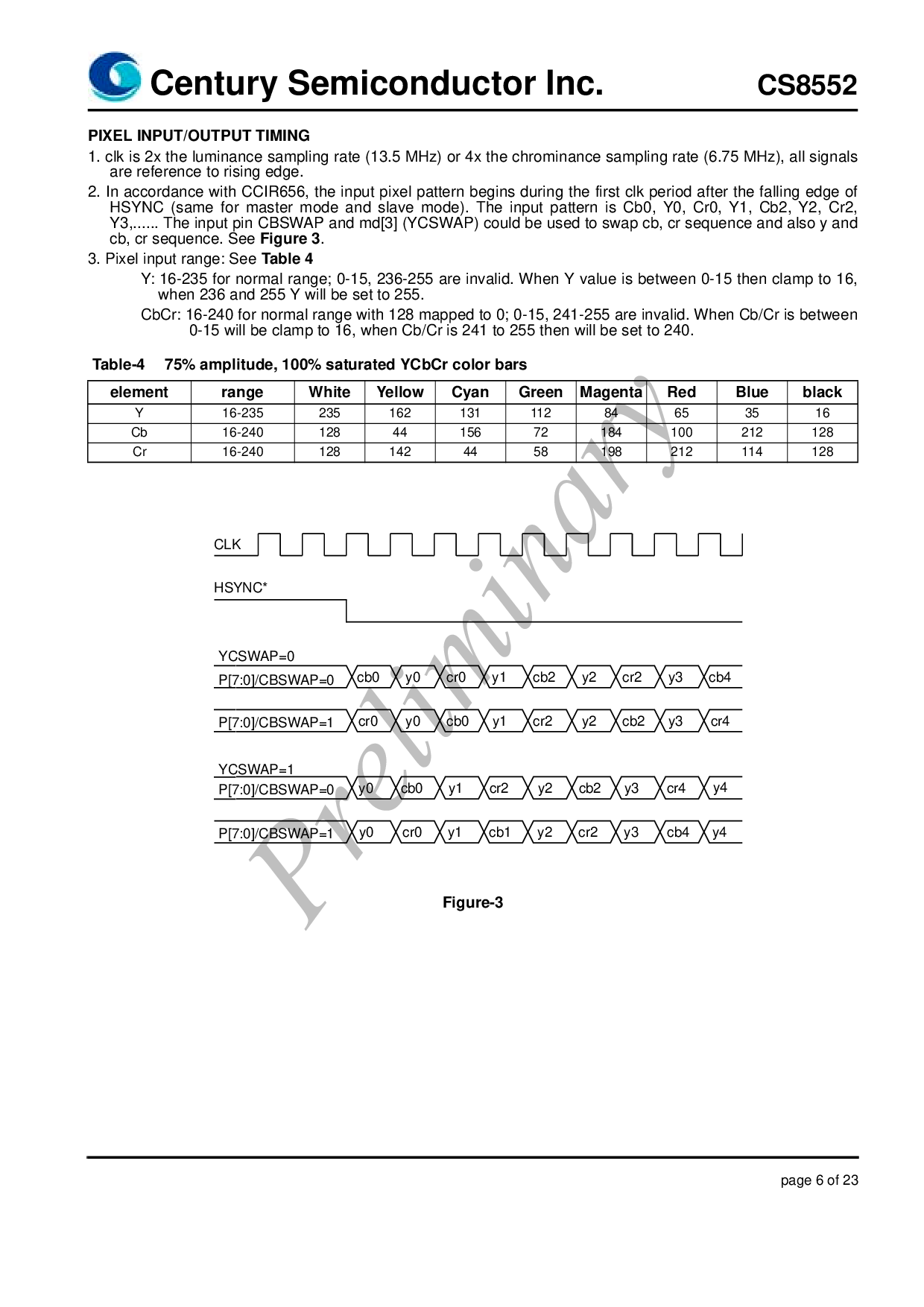

表格-4 75% 振幅, 100% saturated ycbcr 颜色 bars

图示-3

元素 范围 白 黄 Cyan 绿色 Magenta Red 蓝 黑色

Y 16-235 235 162 131 112 84 65 35 16

Cb 16-240 128 44 156 72 184 100 212 128

Cr 16-240 128 142 44 58 198 212 114 128

CLK

HSYNC*

YCSWAP=0

p[7:0]/cbswap=0

YCSWAP=1

p[7:0]/cbswap=1

p[7:0]/cbswap=0

cb0y0cr0y1cb2y2cr2y3cb4

cr0 y0 cb0 y1 cr2 y2 cb2 y3 cr4

y0 cb0 y1 cr2 y2 cb2 y3 cr4

y0 cr0 y1 cb1 y2 cr2 y3 cb4

y4

y4

p[7:0]/cbswap=1