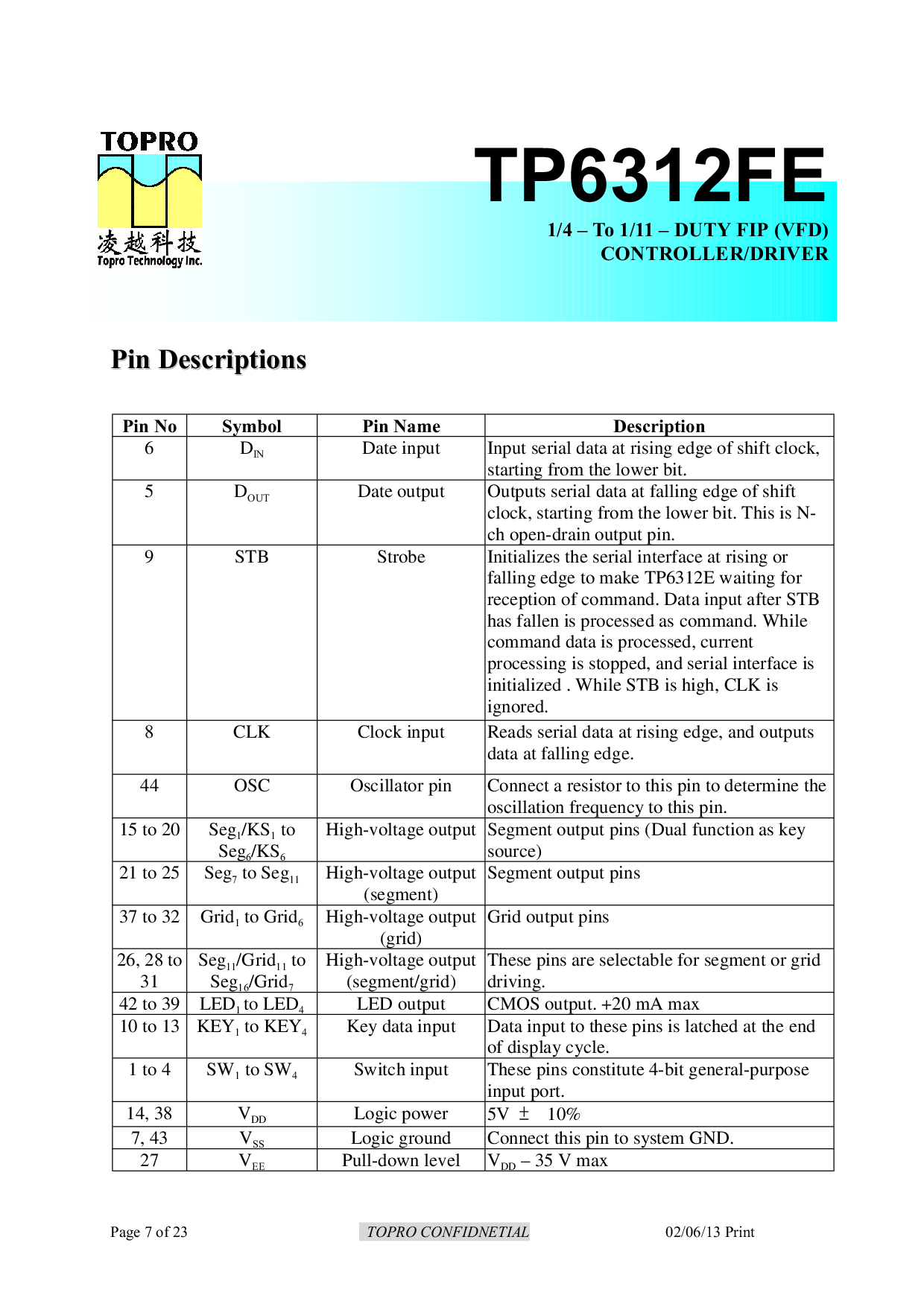

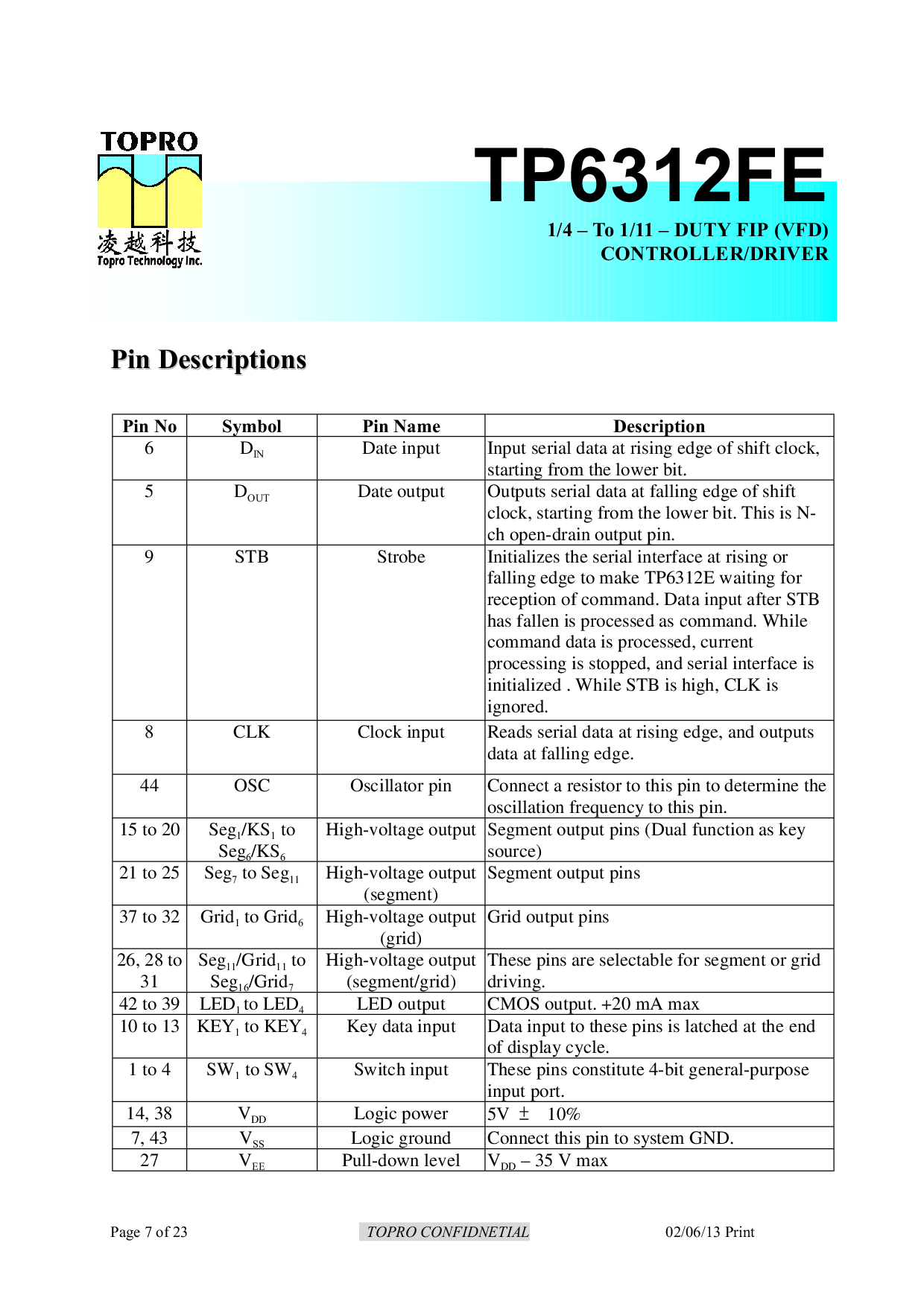

6D

日期 输入 输入 串行 数据 在 rising 边缘 的 变换 时钟,

开始 从 这 更小的 位.

5D

日期 输出 输出 串行 数据 在 下落 边缘 的 变换

时钟, 开始 从 这 更小的 位. 这个 是 n-

ch 打开-流 输出 管脚.

9 STB Strobe initializes 这 串行 接口 在 rising 或者

下落 边缘 至 制造 tp6312e waiting 为

reception 的 command. 数据 输入 之后 stb

有 fallen 是 processed 作 command. 当

command 数据 是 processed, 电流

处理 是 stopped, 和 串行 接口 是

initialized . 当 stb 是 高, clk 是

ignored.

8 CLK 时钟 输入 读 串行 数据 在 rising 边缘, 和 输出

数据 在 下落 边缘.

44 OSC 振荡器 管脚 连接 一个 电阻 至 这个 管脚 至 决定 这

振动 频率 至 这个 管脚.

15 至 20 Seg

/ks

至

Seg

/ks

高-电压 输出 段 输出 管脚 (双 函数 作 关键

源)

21 至 25 Seg

至 seg

高-电压 输出

(段)

段 输出 管脚

37 至 32 Grid

至 grid

高-电压 输出

(grid)

grid 输出 管脚

26, 28 至

31

Seg

/grid

至

Seg

/grid

高-电压 输出

(段/grid)

这些 管脚 是 可选择的 为 段 或者 grid

驱动.

42 至 39 LED

至 led

led 输出 cmos 输出. +20 毫安 最大值

10 至 13 关键

至 关键

关键 数据 输入 数据 输入 至 这些 管脚 是 latched 在 这 终止

的 显示 循环.

1 至 4 SW

至 sw

转变 输入 这些 管脚 组成 4-位 一般-目的

输入 端口.

14, 38 V

逻辑 电源

5V

10%

7, 43 V

逻辑 地面 连接 这个 管脚 至 系统 地.

27 V

拉-向下 水平的 V

– 35 v 最大值