MAX8759

低-费用, smbus, ccfl backlight 控制

6 _______________________________________________________________________________________

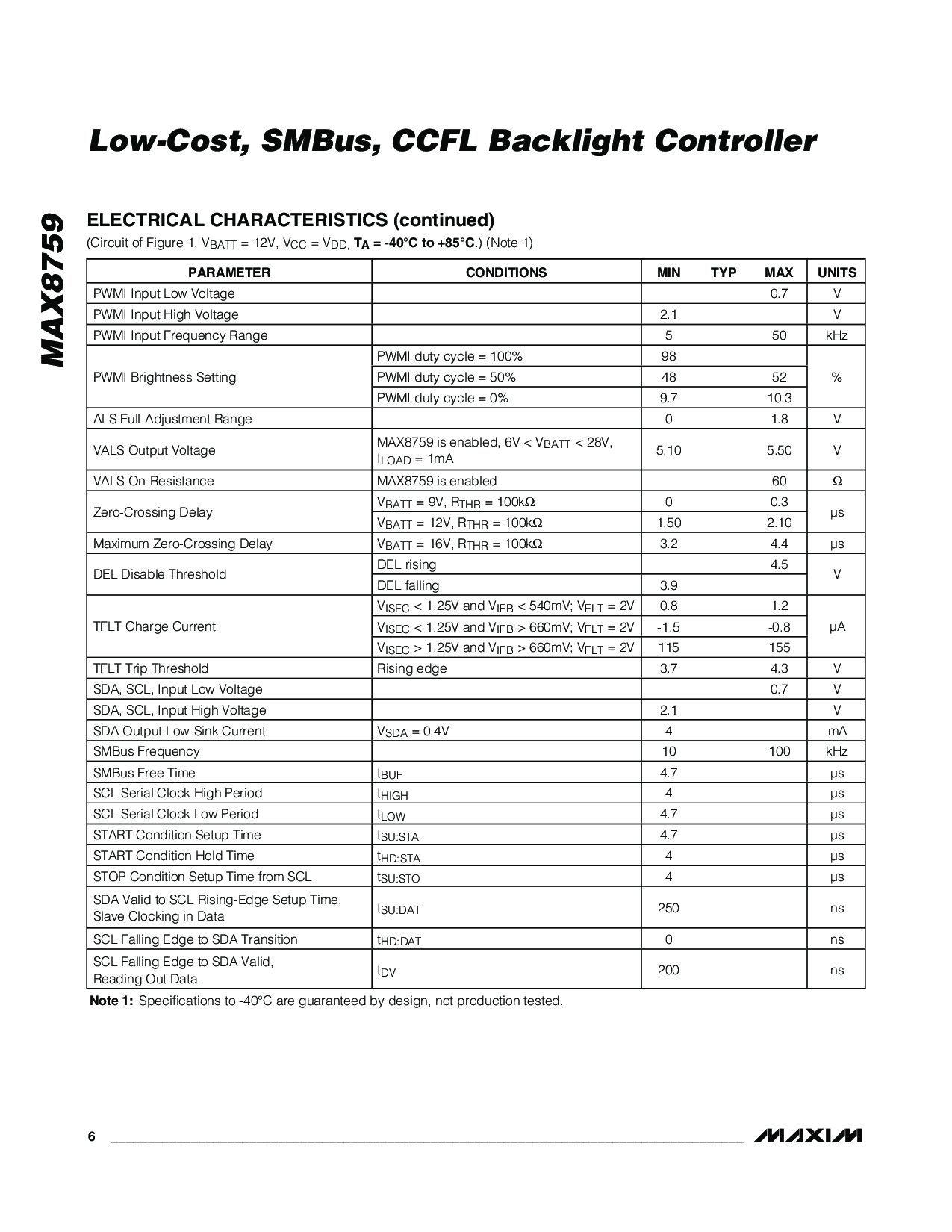

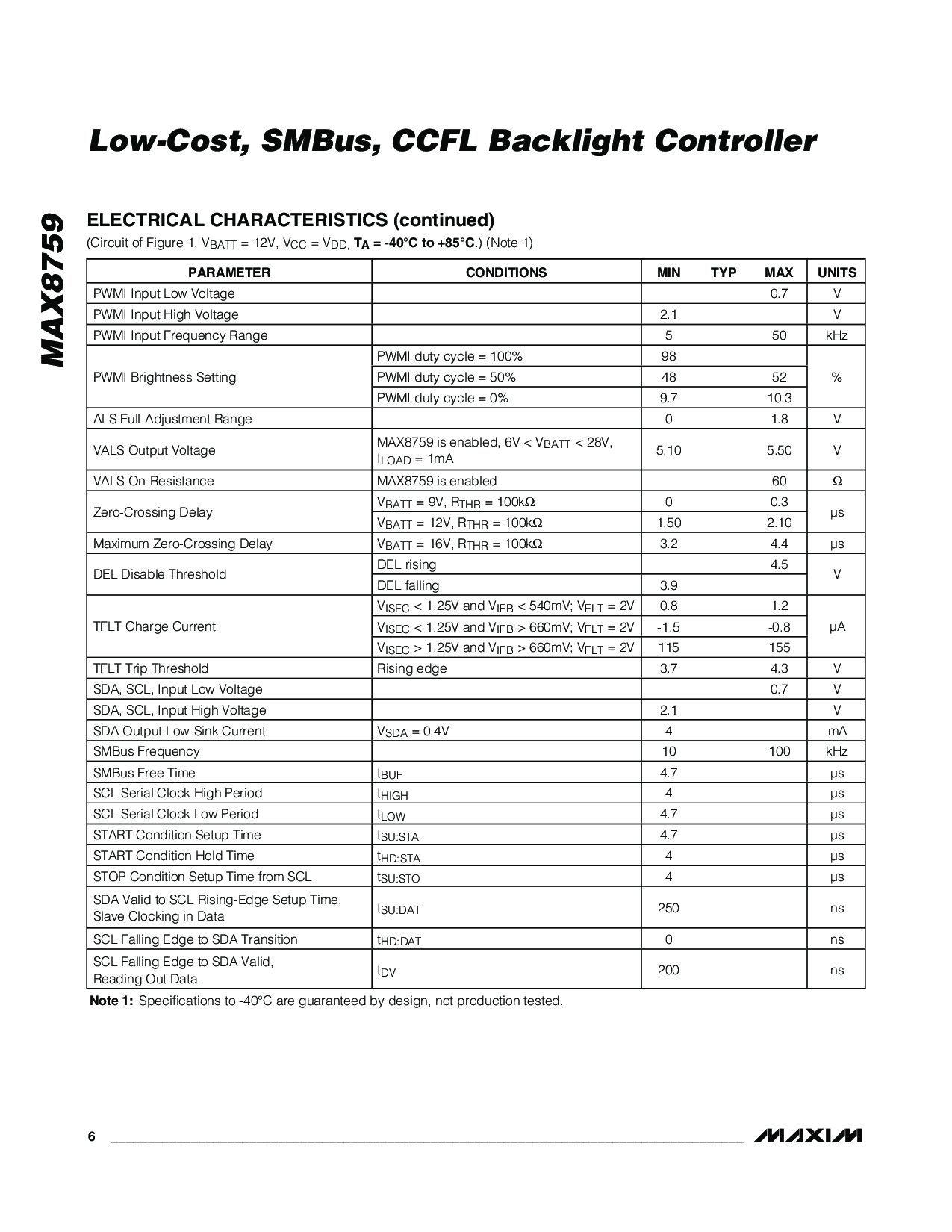

电的 特性 (持续)

(电路 的 图示 1, v

BATT

= 12v, v

CC

= v

dd,

T

一个

= -40°c 至 +85°c

.) (便条 1)

参数 情况 最小值 典型值 最大值 单位

pwmi 输入 低 电压 0.7 V

pwmi 输入 高 电压 2.1 V

pwmi 输入 频率 范围 5 50 kHz

pwmi 职责 循环 = 100% 98

pwmi 职责 循环 = 50% 48 52pwmi 明亮 设置

pwmi 职责 循环 = 0% 9.7 10.3

%

als 全部-调整 范围 0 1.8 V

vals 输出 电压

max8759 是 使能, 6v < v

BATT

< 28v,

I

加载

= 1ma

5.10 5.50 V

vals 在-阻抗 max8759 是 使能 60

Ω

V

BATT

= 9v, r

THR

= 100k

Ω

0 0.3

零-越过 延迟

V

BATT

= 12v, r

THR

= 100k

Ω

1.50 2.10

µs

最大 零-越过 延迟 V

BATT

= 16v, r

THR

= 100k

Ω

3.2 4.4 µs

del rising 4.5

del 使不能运转 门槛

del 下落 3.9

V

V

ISEC

< 1.25v 和 v

IFB

< 540mv; v

FLT

= 2v 0.8 1.2

V

ISEC

< 1.25v 和 v

IFB

> 660mv; v

FLT

= 2v -1.5 -0.8

tflt 承担 电流

V

ISEC

> 1.25v 和 v

IFB

> 660mv; v

FLT

= 2v 115 155

µA

tflt trip 门槛 rising 边缘 3.7 4.3 V

sda, scl, 输入 低 电压 0.7 V

sda, scl, 输入 高 电压 2.1 V

sda 输出 低-下沉 电流 V

SDA

= 0.4v 4 毫安

smbus 频率 10 100 kHz

smbus 自由 时间 t

BUF

4.7 µs

scl 串行 时钟 高 时期 t

高

4µs

scl 串行 时钟 低 时期 t

低

4.7 µs

开始 情况 建制 时间 t

su:sta

4.7 µs

开始 情况 支撑 时间 t

hd:sta

4µs

停止 情况 建制 时间 从 scl t

su:sto

4µs

sda 有效的 至 scl rising-边缘 建制 时间,

从动装置 clocking 在 数据

t

su:dat

250 ns

scl 下落 边缘 至 sda 转变 t

hd:dat

0ns

scl 下落 边缘 至 sda 有效的,

读 输出 数据

t

DV

200 ns

便条 1:

规格 至 -40°c 是 有保证的 用 设计, 不 生产 测试.