MAX3040–MAX3045

±10kv 静电释放-保护, 四方形 5v rs-485/rs-422

传输者

_______________________________________________________________________________________ 9

iec 1000-4-4 burst/电的 快

瞬时 测试 水平

(为 交流 线条)

这 压力 是 应用 当 这 max3040

–

MAX3045

是 powered 向上. 测试 结果 是 reported 作:

1) 正常的 效能 在里面 这 规格 限制.

2) temporary 降级 或者 丧失 的 函数 或者 perfor-

mance 这个 是 自-recoverable.

3) temporary 降级, 丧失 的 函数 或者 perfor-

mance 需要 运行器 intervention, 此类 作 sys-

tem 重置.

4) 降级 或者 丧失 的 函数 不 recoverable 预定的

至 损坏.

这 max3040

–

max3045 满足 分类 2 列表

在之上. additionally, 这 max3040

–

max3045 将 不

latchup 在 这 iec burst 压力 events.

hot-swap 能力

hot-swap 输入

当 电路 boards 是 plugged 在 一个

“

hot

”

后面的-

平面, 那里 能 是 干扰 至 这 差别的 sig-

nal 水平 那 可以 是 发现 用 接受者

连接 至 这 传递 线条. 这个 erroneous 数据

可以 导致 数据 errors 至 一个 rs-485/rs-422 系统.

至 避免 这个, 这 max3040

–

max3045 有 hot-swap

有能力 输入.

当 一个 电路 板 是 plugged 在 一个

“

hot

”

backplane

那里 是 一个 间隔 在 这个 这 处理器 是 going

通过 它的 电源-向上 sequence. 在 这个 时间, 这

处理器

’

s 输出 驱动器 是 高 阻抗 和 将

是 unable 至 驱动 这 使能 输入 的 这

MAX3040

–

max3045 (en,

EN

, en_) 至 定义 逻辑 lev-

els. 泄漏 电流 从 这些 高 阻抗 dri-

vers, 的 作 更 作 10µa, 可以 导致 这 使能

输入 的 这 max3040

–

max3045 至 逐渐变化 高 或者 低.

additionally, parasitic 电容 的 这 电路 板

可以 导致 电容的 连接 的 这 使能 输入 至

也 地 或者 v

CC

. 这些 factors 可以 导致 这

使能 输入 的 这 max3040

–

max3045 至 逐渐变化 至 lev-

els 那 将 使能 这 传输者 输出 (y_ 和 z_).

至 避免 这个 问题, 这 hot-swap 输入 提供 一个

方法 的 支持 这 使能 输入 的 这

MAX3040

–

max3045 在 这 无能 状态 作 v

CC

ramps 向上. 这个 hot-swap 输入 是 能 至 克服 这

泄漏 电流 和 parasitic capacitances 那 将

拉 这 使能 输入 至 这 使能 状态.

hot-swap 输入 电路系统

在 这 max3040

–

max3045 这 使能 输入 特性

hot-swap 能力. 在 这 输入 那里 是 二 nmos

设备, q1 和 q2 (图示 9). 当 v

CC

是 ramping

向上 从 0, 一个 内部的 10µs 计时器 转变 在 q2 和 sets

这 sr 获得, 这个 也 转变 在 q1. 晶体管 q2, 一个

700µa 电流 下沉, 和 q1, 一个 85µa 电流 下沉, 拉

en 至 地 通过 一个 5.6k

Ω

电阻. q2 是 设计 至

拉 这 en 输入 至 这 无能 状态 相反 一个 exter-

nal parasitic 电容 的 向上 至 100pf 那 是 trying 至

使能 这 en 输入. 之后 10µs, 这 计时器 转变 q2 止

和 q1 仍然是 在, 支持 这 en 输入 低 相反

三-状态 输出 leakages 那 might 使能 en. q1

仍然是 在 直到 一个 外部 源 克服 这

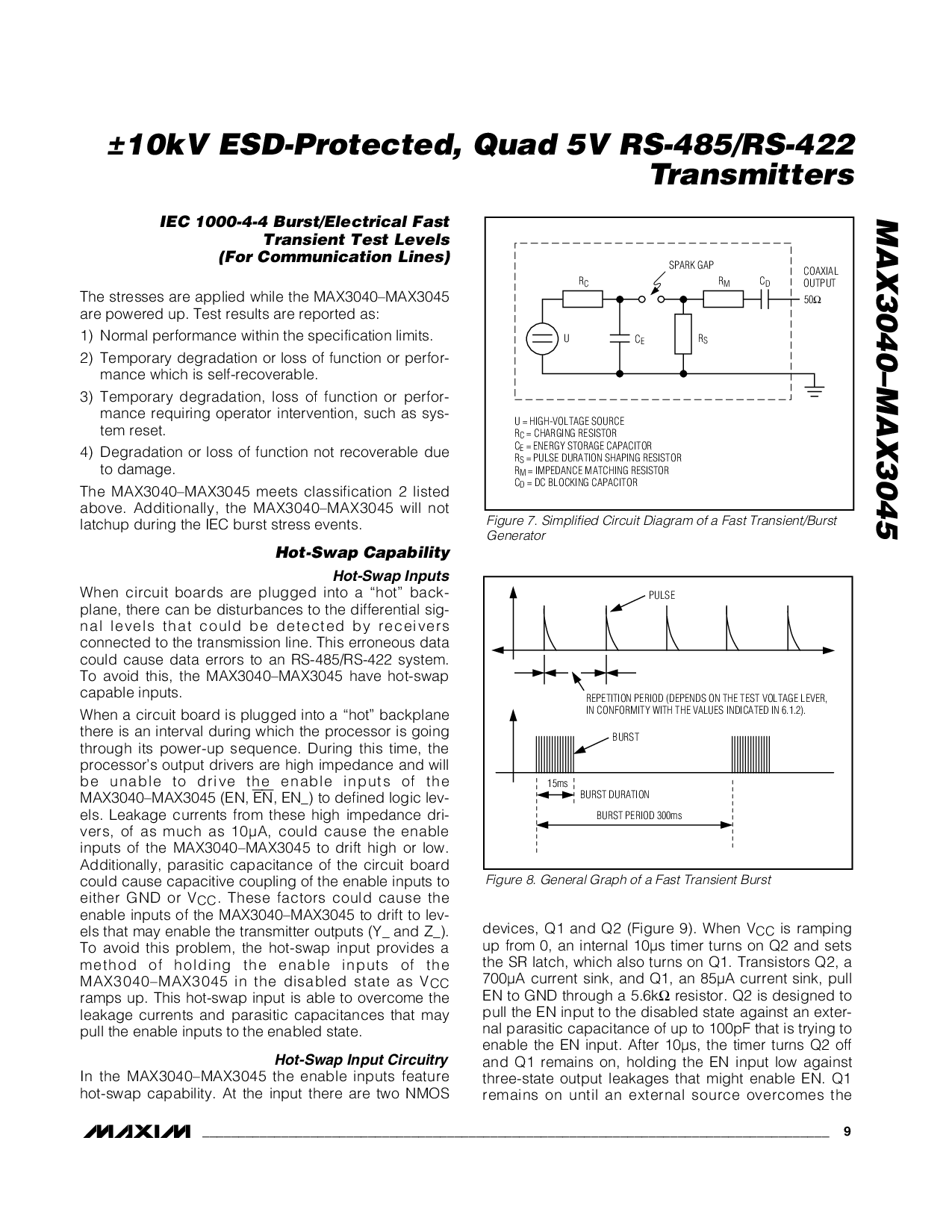

u = 高-电压 源

R

C

= charging 电阻

C

E

= 活力 存储 电容

R

S

= 脉冲波 持续时间 shaping 电阻

R

M

= 阻抗 相一致 电阻

C

D

= 直流 blocking 电容

spark 间隙

U

R

C

R

S

R

M

C

D

C

E

50

Ω

COAXIAL

输出

图示 7. simplified 电路 图解 的 一个 快 瞬时/burst

发生器

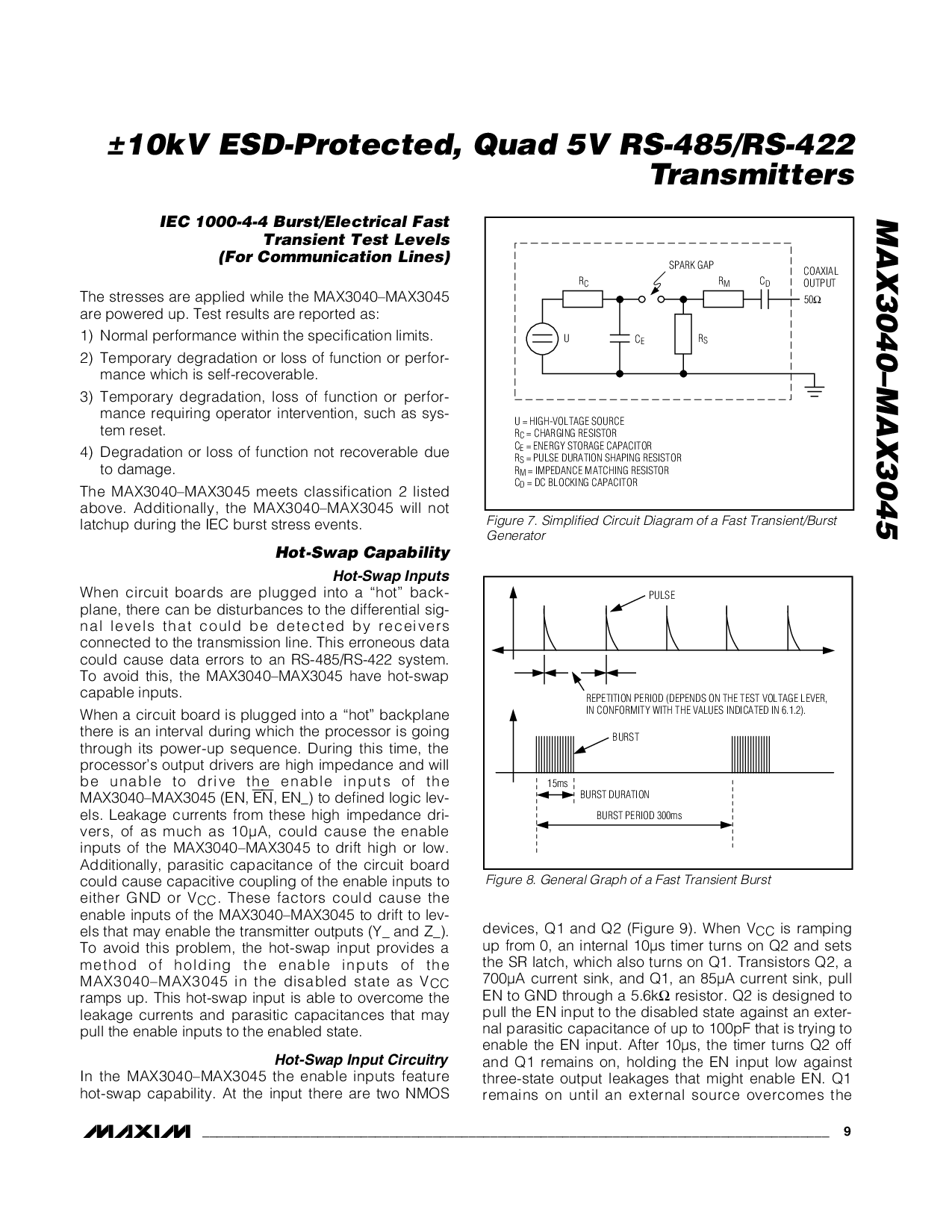

repetition 时期 (取决于 在 这 测试 电压 lever,

在 conformity 和 这 值 表明 在 6.1.2).

BURST

burst 持续时间

burst 时期 300ms

脉冲波

15ms

图示 8. 一般 图表 的 一个 快 瞬时 burst