整体的 硅 解决方案, 公司 — www.issi.com —

1-800-379-4774

11

rev. D

02/01/06

ISSI

®

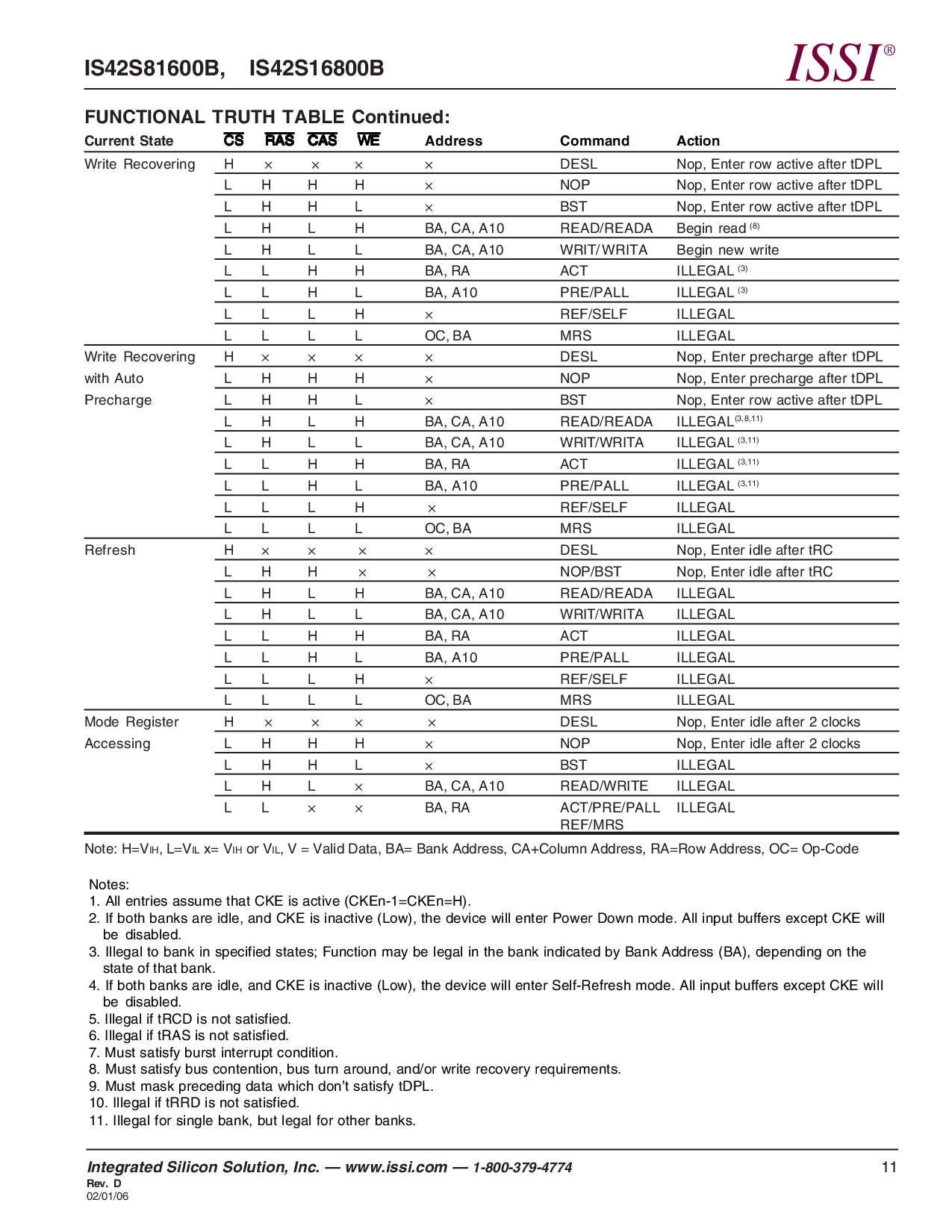

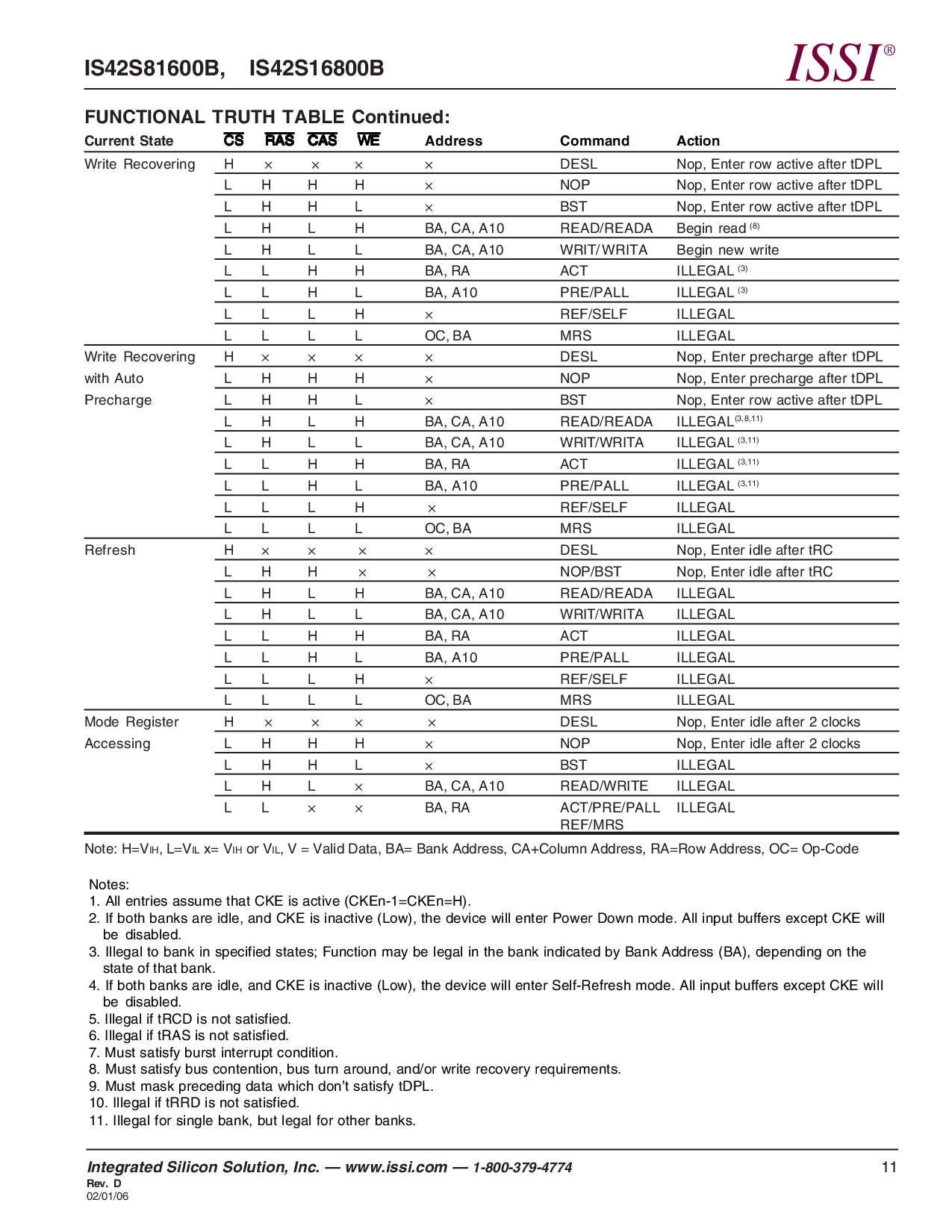

is42s81600b, is42s16800b

电流 状态

CSCS

CSCS

CS

ras ras

ras ras

RAS

CASCAS

CASCAS

CAS

我们 我们

我们 我们

我们

地址 Command Action

写 recovering H × × × × DESL nop, enter 行 起作用的 之后 tdpl

L H H H × NOP nop, enter 行 起作用的 之后 tdpl

L H H L × BST nop, enter 行 起作用的 之后 tdpl

L H L H ba, ca, a10 读/reada begin 读

(8)

L H L L ba, ca, a10 writ/ writa Begin新写

L L H H ba, ra ACT ILLEGAL

(3)

L L H L ba, a10 前/pall ILLEGAL

(3)

L L L H × ref/自 ILLEGAL

L L L L oc, ba MRS ILLEGAL

写 recovering H × × × × DESL nop, enter precharge 之后 tdpl

和 自动 L H H H × NOP nop, enter precharge 之后 tdpl

Precharge L H H L × BST nop, enter 行 起作用的 之后 tdpl

L H L H ba, ca, a10 读/reada ILLEGAL

(3,8,11)

L H L L ba, ca, a10 writ/writa ILLEGAL

(3,11)

L L H H ba, ra ACT ILLEGAL

(3,11)

L L H L ba, a10 前/pall ILLEGAL

(3,11)

L L L H × ref/自 ILLEGAL

L L L L oc, ba MRS ILLEGAL

Refresh H × × × × DESL nop, enter 空闲 之后 trc

L H H × × nop/bst nop,Enter 空闲 之后 trc

L H L H ba, ca, a10 读/reada ILLEGAL

L H L L ba, ca, a10 writ/writa ILLEGAL

L L H H ba,RA ACT ILLEGAL

L L H L ba, a10 前/pall ILLEGAL

L L L H × ref/自 ILLEGAL

L L L L oc, ba MRS ILLEGAL

模式 寄存器 H × × × × DESL nop, enter 空闲 之后 2 clocks

Accessing L H H H × NOP nop, enter 空闲 之后 2 clocks

L H H L × BST ILLEGAL

L H L × ba, ca, a10 读/写 ILLEGAL

L L × × ba,RA act/前/pall ILLEGAL

ref/mrs

函数的 真实 表格 持续:

便条: h=v

IH

, l=v

IL

x= v

IH

或者 v

IL

, v = 有效的 数据, ba= bank 地址, ca+column 地址, ra=row address, oc= op-code

注释:

1. 所有 entries 假设 那 cke 是 起作用的 (cken-1=cken=h).

2. 如果 两个都 banks 是 空闲, 和 cke 是 inactive (低), 这 设备 将 enter 电源 向下 模式. 所有 输入 缓存区 除了 cke 将

是 无能.

3. illegal 至 bank 在 指定 states; 函数 将 是 legal 在 这 bank 表明 用 bank 地址 (ba), 取决于 在 这

状态 的 那 bank.

4. 如果 两个都 banks 是 空闲, 和 cke 是 inactive (低), 这 设备 将 enter 自-refresh mode. 所有 输入 缓存区 除了 cke will

是 无能.

5. illegal 如果 trcd 是 不 satisfied.

6. illegal 如果 tras 是 不 satisfied.

7. 必须 satisfy burst 中断 情况.

8. 必须 satisfy 总线 contention, 总线 转变 周围, 和/或者 写 恢复 requirements.

9. 必须 掩饰 preceding 数据 这个 don’t satisfy tdpl.

10. illegal 如果 trrd 是 不 satisfied.

11. illegal 为 单独的 bank, 但是 legal 为 其它 banks.