ADP3110

rev. 0 | 页 9 的 12

这 场效应晶体管 vendor 应当 提供 一个 最大 电压 回转

比率 在 流 电流 比率 此类 那 这个 能 是 设计

周围. 这 next 步伐 是 至 决定 这 预期的 最大

电流 在 这 场效应晶体管. 这个 能 是 完毕 用

()

输出

最大值

最大值

输出

DCMAX

Lf

D

VVCCphaseperII

×

×−+=

)(

(7)

D

最大值

是 决定 为 这 vr 控制 正在 使用 和 这

驱动器. 便条 这个 电流 gets 分隔 roughly equally 在

mosfets 如果 更多 比 一个 是 使用 (假设 一个 worst-情况

mismatch 的 30% 为 设计 余裕).

L

输出

是 这 输出

inductor 值.

当 producing 这 设计, 那里 是 非 精确的 方法 为

calculating 这 dv/dt 预定的 至 这 parasitic 影响 在 这 外部

mosfets 作 好 作 这 pcb. 不管怎样, 它 能 是 量过的 至

决定 如果 它 是 safe. 如果 它 呈现 这 dv/dt 是 too 快, 一个

optional 门 电阻 能 是 增加 在 drvh 和 这

高-一侧 场效应晶体管. 这个 电阻 slows 向下 这 dv/dt, 但是 它

也 增加 这 切换 losses 在 这 高-一侧 场效应晶体管.

这 adp3110 是 optimally 设计 和 一个 内部的 驱动

阻抗 那 工作 和 大多数 mosfets 至 转变 它们

efficiently 还 降低 dv/dt. 不管怎样, 一些 高 速

mosfets 将 需要 这个 外部 门 电阻, 取决于 在

这 电流 正在 切换 在 这 场效应晶体管.

低-一侧 (同步的) mosfets

这 低-一侧 mosfets 是 通常地 选择 至 有 一个 低 在

阻抗 至 降低 传导 losses. 这个 通常地 implies 一个

大 输入 门 电容 和 门 承担. 这 第一 concern 是

至 制造 确信 这 电源 传送 从 这 adp3110’s drvl

做 不 超过 这 热的 比率 的 这 驱动器.

这 next concern 为 这 低-一侧 mosfets 是 至 阻止 它们

从 无意地 正在 切换 在 当 这 高-一侧

场效应晶体管 转变 在. 这个 occurs 预定的 至 这 流-门 (miller,

也 指定 作 c

rss

) 电容 的 这 场效应晶体管. 当 这

流 的 这 低-一侧 场效应晶体管 是 切换 至 vcc 用 这 高-

一侧 turning 在 (在 一个 比率 dv/dt), 这 内部的 门 的 这 低-

一侧 场效应晶体管 是 牵引的 向上 用 一个 数量 roughly equal 至

VCC

×

(c

rss

/c

iss

). 它 是 重要的 至 制造 确信 这个 做 不 放

这 场效应晶体管 在 传导.

另一 仔细考虑 是 这 nonoverlap 电路系统 的 这

adp3110, 这个 attempts 至 降低 这 nonoverlap 时期.

在 这 状态 的 这 高-一侧 turning 止 至 低-一侧 turning

在, 这 sw 管脚 和 这 情况 的 sw 较早的 至 切换 是

监控 至 adequately 阻止 overlap.

不管怎样, 在 这 低-一侧 转变 止 至 高-一侧 转变 在, 这

sw 管脚 做 不 包含 信息 为 determining 这

恰当的 切换 时间, 所以 这 状态 的 这 drvl 管脚 是 监控

至 go 在下 一个 sixth 的 v

CC

和 然后 一个 延迟 是 增加. 预定的 至

这 miller 电容 和 内部的 延迟 的 这 低-一侧

场效应晶体管 门, 一个 必须 确保 这 miller-至-输入 电容

比率 是 低 足够的 和 这 低-一侧 场效应晶体管 内部的 延迟

是 不 大 足够的 至 准许 意外的 转变 在 的 这 低-一侧

场效应晶体管 当 这 高-一侧 场效应晶体管 转变 在.

联系 销售 为 一个 updated 列表 的 推荐 低-一侧

mosfets.

pc 板 布局 仔细考虑

使用 这 下列的 一般 指导原则 当 designing 打印

电路 boards.

1.

查出 输出 这 高 电流 paths 和 使用 短的, 宽

(>20 mil) 查出 至 制造 这些 连接.

2.

降低 查出 电感 在 这 drvh 和 drvl

输出 和 这 场效应晶体管 门.

3.

连接 这 pgnd 管脚 的 这 adp3110 作 closely 作

可能 至 这 源 的 这 更小的 场效应晶体管.

4.

这 v

CC

绕过 电容 应当 是 located 作 closely 作

可能 至 这 vcc 和 pgnd 管脚.

5.

使用 vias 至 其它 layers 当 可能 至 maximize 热的

传导 away 从 这 ic.

这 电路 在

图示 6显示 如何 四 驱动器 能 是 联合的

和 这 adp3181 至 表格 一个 总的 电源 转换 解决方案 为

generating v

cc(核心)

为 一个 intel cpu 那 是 vrd 10.x

一致的.

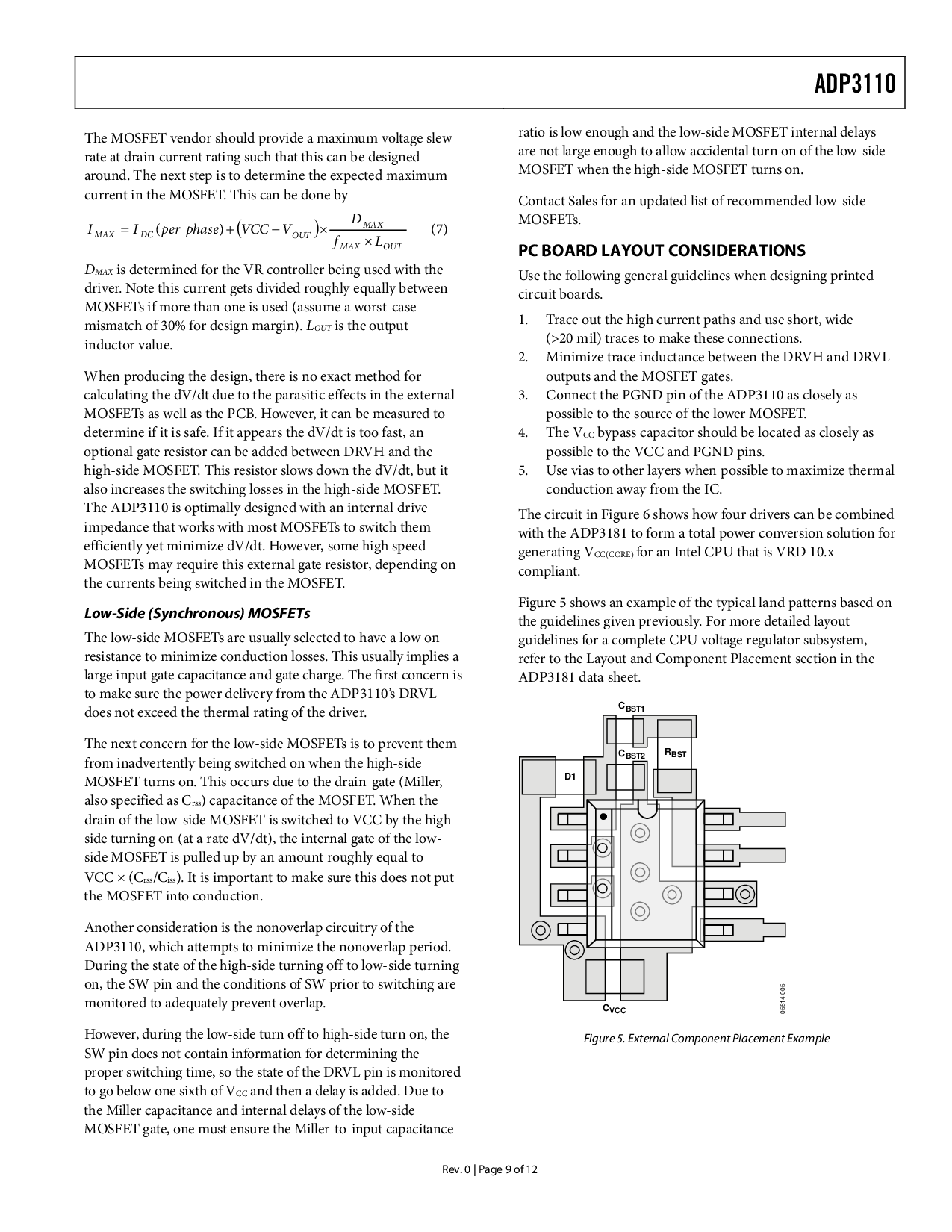

图示 5显示 一个 例子 的 这 典型 地带 patterns 为基础 在

这 指导原则 给 先前. 为 更多 详细地 布局

指导原则 为 一个 完全 cpu 电压 调整器 subsystem,

谈及 至 这 布局 和 组件 placement 部分 在 这

adp3181 数据 薄板.

05514-005

D1

C

BST2

C

BST1

R

BST

C

VCC

图示 5. 外部 组件 placement 例子