ADS8344

12

SBAS139B

标识 描述 最小值 典型值 最大值 单位

t

ACQ

acquisition 时间 1.5

µ

s

t

DS

D

在

有效的 较早的 至 dclk rising 100 ns

t

DH

D

在

支撑 之后 dclk 高 10 ns

t

做

dclk 下落 至 d

输出

有效的 200 ns

t

DV

cs 下落 至 d

输出

使能 200 ns

t

TR

cs rising 至 d

输出

无能 200 ns

t

CSS

cs 下落 至 第一 dclk rising 100 ns

t

CSH

cs rising 至 dclk ignored 0 ns

t

CH

dclk 高 200 ns

t

CL

dclk 低 200 ns

t

BD

dclk 下落 至 busy rising 200 ns

t

BDV

cs 下落 至 busy 使能 200 ns

t

BTR

cs rising 至 busy 无能 200 ns

表格 vi. 定时 规格 (+v

CC

= +2.7v 至 3.6v,

T

一个

= –40

°

c 至 +85

°

c, c

加载

= 50pf).

自从 一个 时钟 循环 的 这 串行 时钟 是 consumed 和

busy going 高 (当 这 msb decision 是 正在

制造), 16 额外的 clocks 必须 是 给 至 时钟 输出 所有 16

位 的 数据; 因此, 一个 转换 takes 一个 最小 的 25

时钟 循环 至 全部地 读 这 数据. 自从 大多数 microproces-

sors communicate 在 8-位 transfers, 这个 意思 那 一个

额外的 转移 必须 是 制造 至 俘获 这 lsb.

那里 是 二 方法 的 处理 这个 必要条件. 一个 是

在哪里 这 beginning 的 这 next 控制 字节 呈现 在 这

一样 时间 这 lsb 是 正在 clocked 输出 的 这 ads8344

(看 图示 3). 这个 方法 准许 为 最大 throughput

和 24 时钟 循环 每 转换.

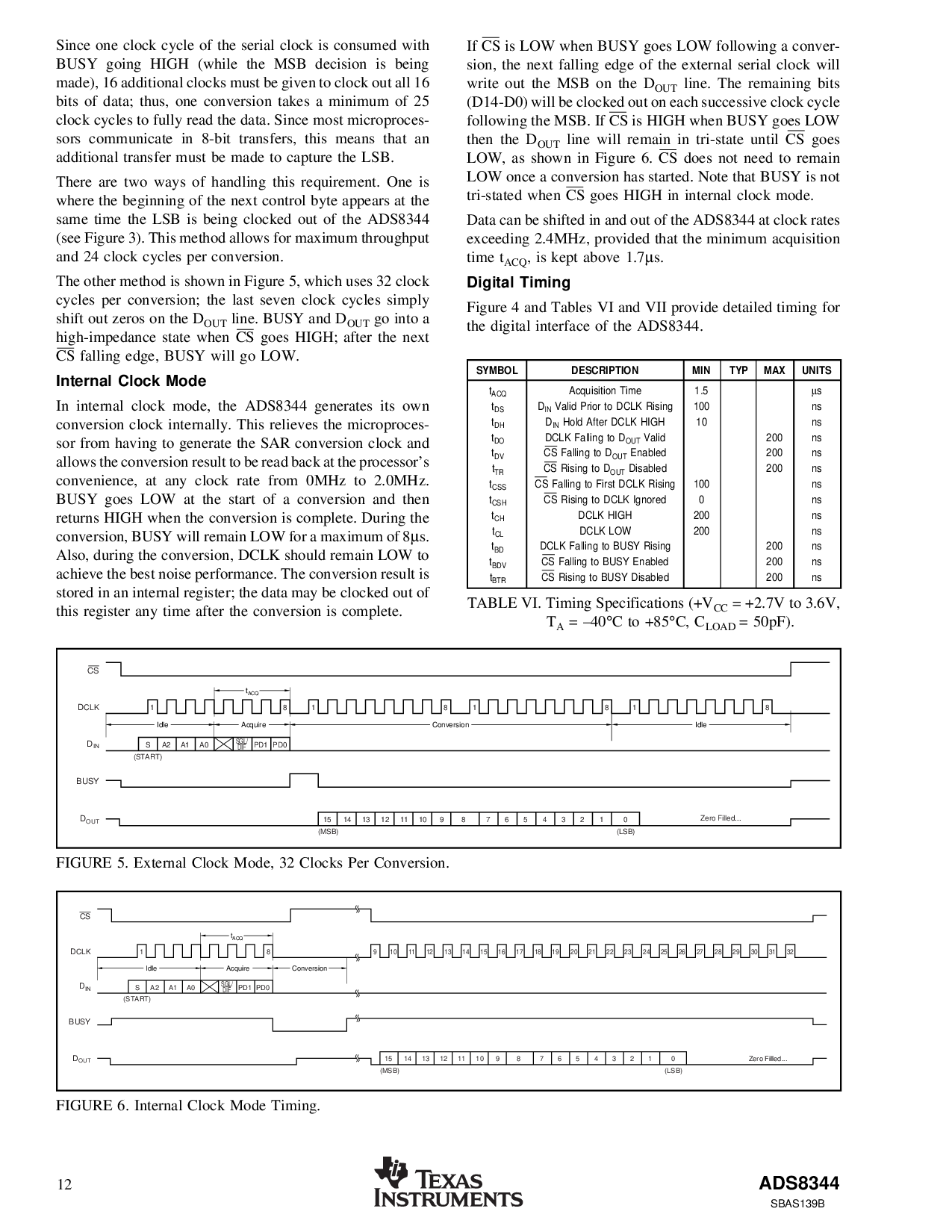

这 其它 方法 是 显示 在 图示 5, 这个 使用 32 时钟

循环 每 转换; 这 last 七 时钟 循环 simply

变换 输出 zeros 在 这 d

输出

线条. busy 和 d

输出

go 在 一个

高-阻抗 状态 当 cs 变得 高; 之后 这 next

cs 下落 边缘, busy 将 go 低.

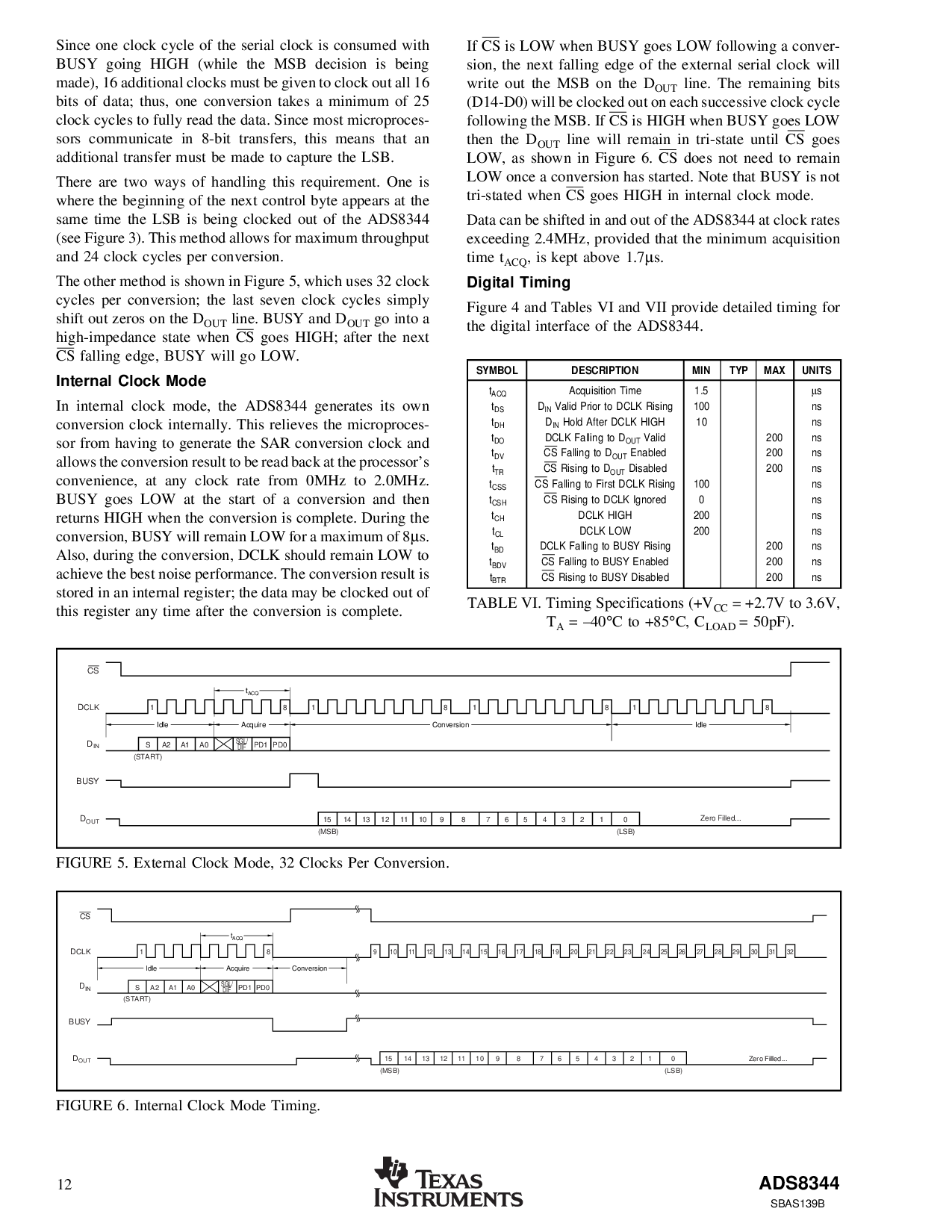

内部的 时钟 模式

在 内部的 时钟 模式, 这 ads8344 发生 它的 自己的

转换 时钟 内部. 这个 relieves 这 microproces-

sor 从 having 至 发生 这 sar 转换 时钟 和

准许 这 转换 结果 至 是 读 后面的 在 这 处理器’s

convenience, 在 任何 时钟 比率 从 0mhz 至 2.0mhz.

busy 变得 低 在 这 开始 的 一个 转换 和 然后

returns 高 当 这 转换 是 完全. 在 这

转换, busy 将 仍然是 低 为 一个 最大 的 8

µ

s.

也, 在 这 转换, dclk 应当 仍然是 低 至

达到 这 最好的 噪音 效能. 这 转换 结果 是

贮存 在 一个 内部的 寄存器; 这 数据 将 是 clocked 输出 的

这个 寄存器 任何 时间 之后 这 转换 是 完全.

t

ACQ

Acquire空闲 转换

1

D

CLK

CS

81

15

D

输出

BUSY

(msb)

(开始)

(lsb)

A2S

D

在

A1 A0

sgl/

DIF

PD1 PD0

14131211109 8 7654321 0

81 8

空闲

18

零 filled...

如果 cs 是 低 当 busy 变得 低 下列的 一个 变换器-

sion, 这 next 下落 边缘 的 这 外部 串行 时钟 将

写 输出 这 msb 在 这 d

输出

线条. 这 remaining 位

(d14-d0) 将 是 clocked 输出 在 各自 successive 时钟 循环

下列的 这 msb. 如果 cs 是 高 当 busy 变得 低

然后 这 d

输出

线条 将 仍然是 在 触发-状态 直到 cs 变得

低, 作 显示 在 图示 6. cs 做 不 需要 至 仍然是

低 once 一个 转换 有 started. 便条 那 busy 是 不

触发-陈述 当 cs 变得 高 在 内部的 时钟 模式.

数据 能 是 shifted 在 和 输出 的 这 ads8344 在 时钟 比率

exceeding 2.4mhz, 提供 那 这 最小 acquisition

时间 t

ACQ

, 是 保持 在之上 1.7

µ

s.

数字的 定时

图示 4 和 tables vi 和 vii 提供 详细地 定时 为

这 数字的 接口 的 这 ads8344.

t

ACQ

Acquire空闲 转换

1

D

CLK

CS

8

9 1011121314151617181920212223242526272829303132

15

D

输出

BUSY

(msb)

(开始)

(lsb)

A2S

D

在

A1 A0

sgl/

DIF

PD1 PD0

14131211109 8 7654321 0 零 filled...

图示 5. 外部 时钟 模式, 32 clocks 每 转换.

图示 6. 内部的 时钟 模式 定时.