9/26

¡ 半导体

msm82c55a-2rs/gs/vjs

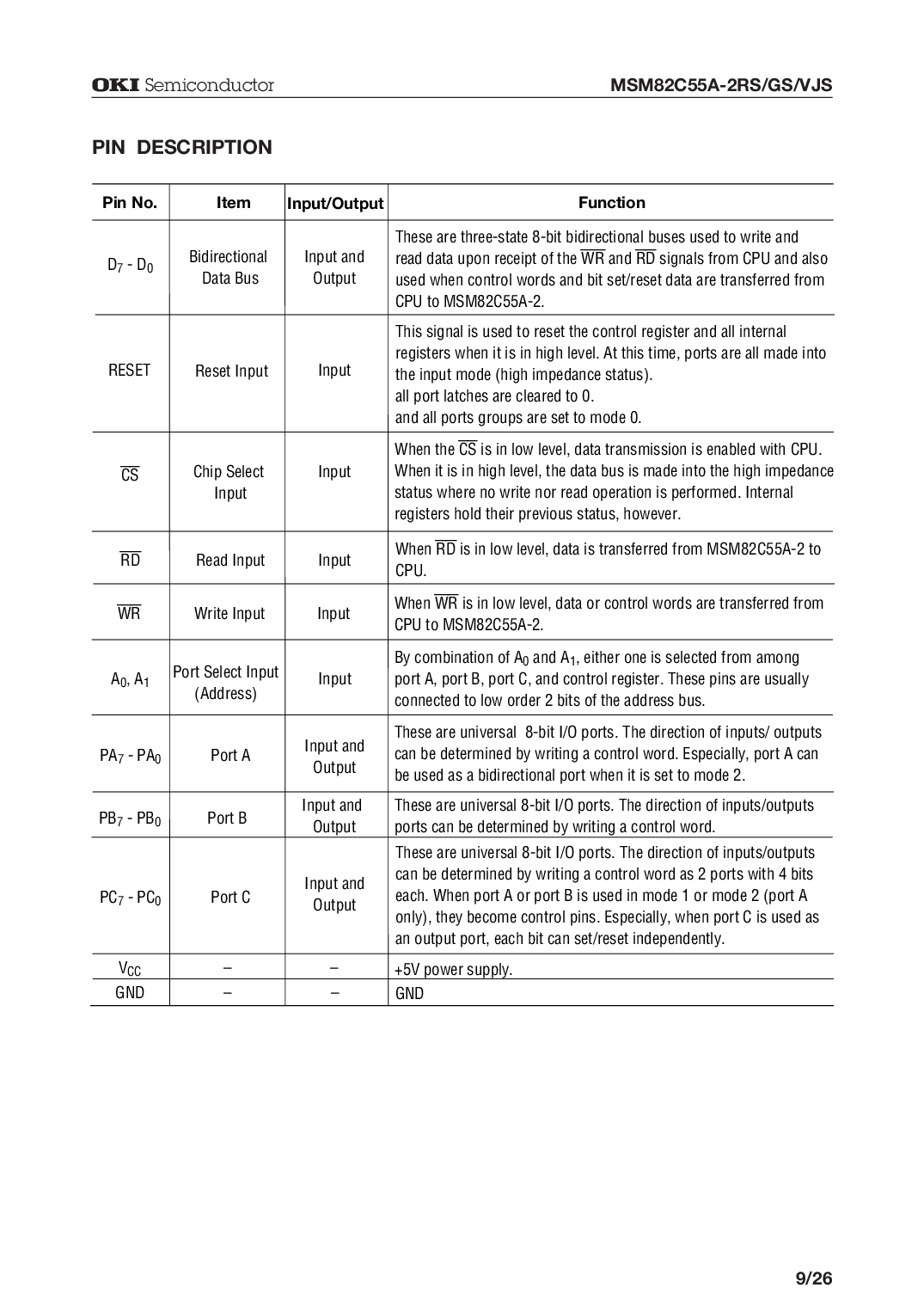

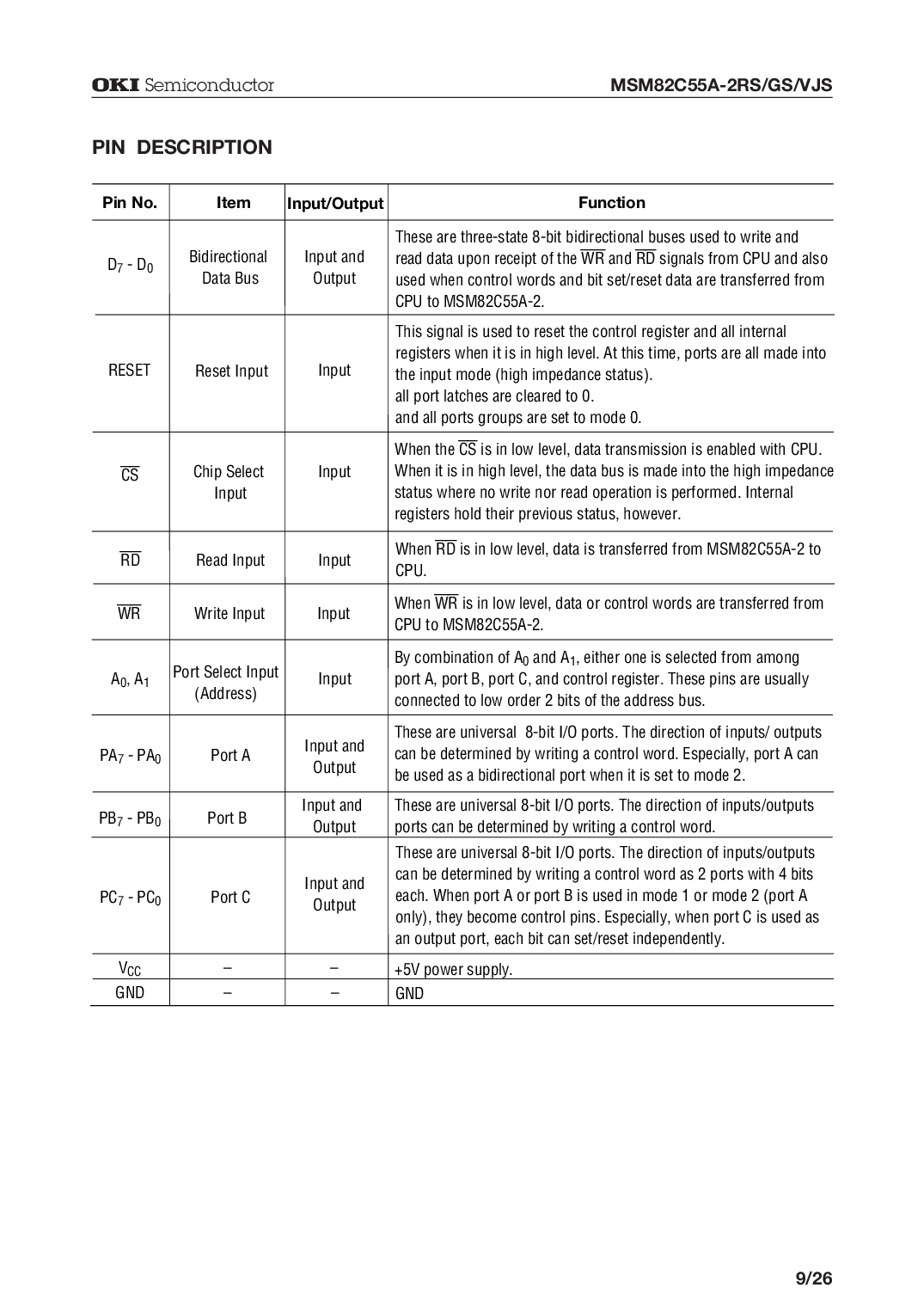

管脚 描述

D

7

- d

0

Item

双向的

数据 总线

输入 和

输出

管脚 非.

输入/输出

函数

CS

碎片 选择

输入

输入

RD

读 输入 输入

一个

0

, 一个

1

端口 选择 输入

(地址)

输入

PA

7

- pa

0

端口 一个

输入 和

输出

PC

7

- pc

0

端口 c

输入 和

输出

这些 是 三-状态 8-位 双向的 buses 使用 至 写 和

读 数据 在之上 receipt 的 这

WR

和

RD

信号 从 cpu 和 也

使用 当 控制 words 和 位 设置/重置 数据 是 transferred 从

cpu 至 msm82c55a-2.

重置

重置 输入

输入

这个 信号 是 使用 至 重置 这 控制 寄存器 和 所有 内部的

寄存器 当 它 是 在 高 水平的. 在 这个 时间, 端口 是 所有 制造 在

这 输入 模式 (高 阻抗 状态).

所有 端口 latches 是 cleared 至 0.

和 所有 端口 groups 是 设置 至 模式 0.

当 这

CS

是 在 低 水平的, 数据 传递 是 使能 和 cpu.

当 它 是 在 高 水平的, 这 数据 总线 是 制造 在 这 高 阻抗

状态 在哪里 非 写 也不 读 运作 是 执行. 内部的

寄存器 支撑 它们的 previous 状态, 不管怎样.

当

RD

是 在 低 水平的, 数据 是 transferred 从 msm82c55a-2 至

cpu.

用 结合体 的 一个

0

和 一个

1

, 也 一个 是 选择 从 among

端口 一个, 端口 b, 端口 c, 和 控制 寄存器. 这些 管脚 是 通常地

连接 至 低 顺序 2 位 的 这 地址 总线.

这些 是 普遍的 8-位 i/o 端口. 这 方向 的 输入/ 输出

能 是 决定 用 writing 一个 控制 文字. 特别, 端口 一个 能

是 使用 作 一个 双向的 端口 当 它 是 设置 至 模式 2.

这些 是 普遍的 8-位 i/o 端口. 这 方向 的 输入/输出

能 是 决定 用 writing 一个 控制 文字 作 2 端口 和 4 位

各自. 当 端口 一个 或者 端口 b 是 使用 在 模式 1 或者 模式 2 (端口 一个

仅有的), 它们 变为 控制 管脚. 特别, 当 端口 c 是 使用 作

一个 输出 端口, 各自 位 能 设置/重置 independently.

地 – –

地

WR

写 输入 输入

当

WR

是 在 低 水平的, 数据 或者 控制 words 是 transferred 从

cpu 至 msm82c55a-2.

铅

7

- 铅

0

端口 b

输入 和

输出

这些 是 普遍的 8-位 i/o 端口. 这 方向 的 输入/输出

端口 能 是 决定 用 writing 一个 控制 文字.

V

CC

––

+5v 电源 供应.