AD5171

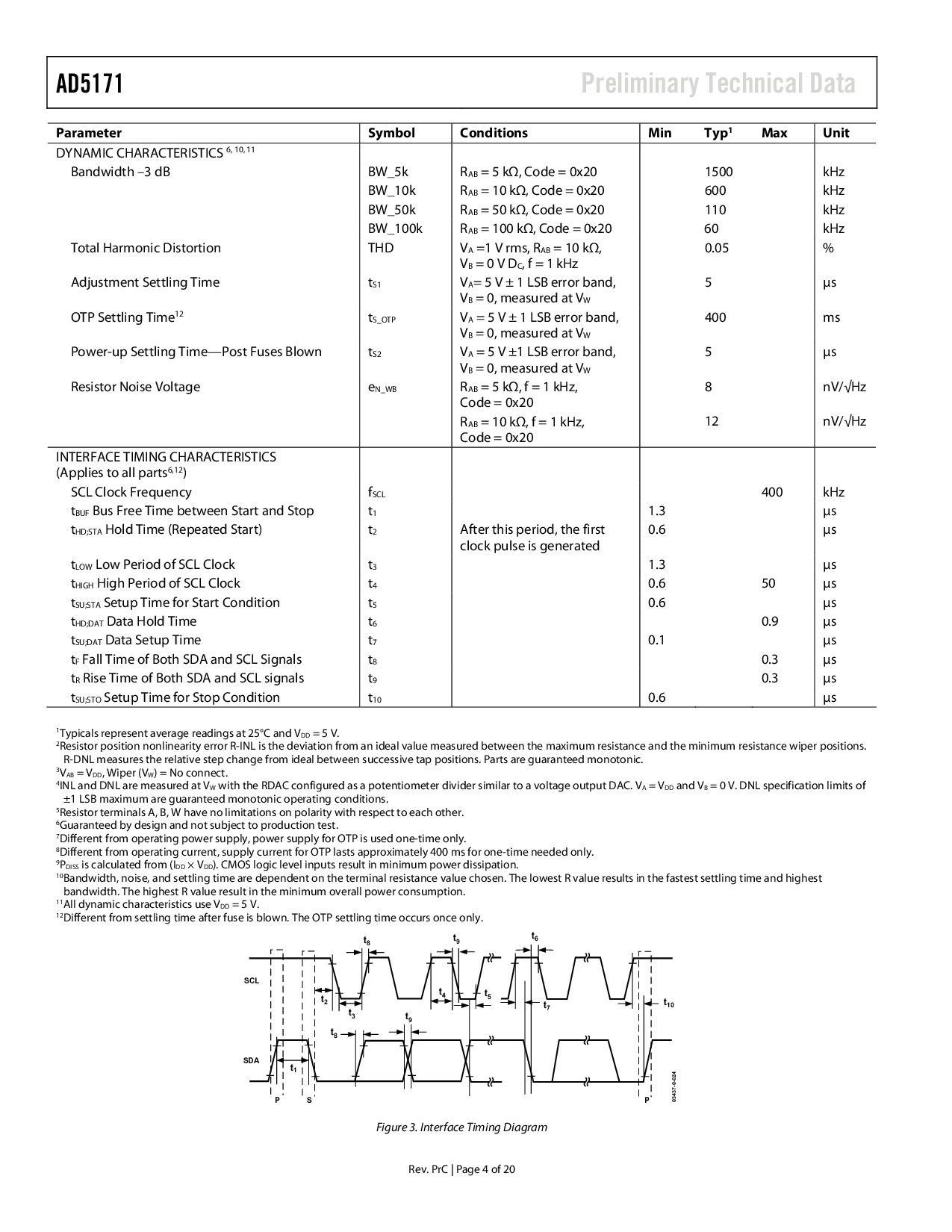

参数 标识 情况 最小值 典型值

1

最大值 单位

动态 特性

6, 10, 11

带宽 –3 db bw_5k R

AB

= 5 kΩ, 代号 = 0x20 1500 kHz

bw_10k r

AB

= 10 kΩ, 代号 = 0x20 600 kHz

bw_50k r

AB

= 50 kΩ, 代号 = 0x20 110 kHz

bw_100k r

AB

= 100 kΩ, 代号 = 0x20 60 kHz

总的 调和的 扭曲量 THD

V

一个

=1 v rms, r

AB

= 10 kΩ,

V

B

= 0 v d

C

, f = 1 khz

0.05 %

调整 安排好 时间 t

S1

V

一个

= 5 v ± 1 lsb 错误 带宽,

V

B

= 0, 量过的 在 v

W

5 µs

otp 安排好 时间

12

t

s_otp

V

一个

= 5 v ± 1 lsb 错误 带宽,

V

B

= 0, 量过的 在 v

W

400 ms

电源-向上 安排好 time—post fuses blown t

S2

V

一个

= 5 v ±1 lsb 错误 带宽,

V

B

= 0, 量过的 在 v

W

5 µs

电阻 噪音 电压 e

n_wb

R

AB

= 5 kΩ, f = 1 khz,

代号 = 0x20

8 nv/√hz

R

AB

= 10 kΩ, f = 1 khz,

代号 = 0x20

12 nv/√hz

接口 定时 特性

(应用 至 所有 部分

6,12

)

scl 时钟 频率 f

SCL

400 khz

t

BUF

总线 自由 时间 在 开始 和 停止 t

1

1.3 µs

t

hd;sta

支撑 时间 (重复的 开始) t

2

之后 这个 时期, 这 第一

时钟 脉冲波 是 发生

0.6 µs

t

低

低 时期 的 scl 时钟 t

3

1.3 µs

t

高

高 时期 的 scl 时钟 t

4

0.6 50 µs

t

su;sta

建制 时间 为 开始 情况 t

5

0.6 µs

t

hd;dat

数据 支撑 时间 t

6

0.9 µs

t

su;dat

数据 建制 时间 t

7

0.1 µs

t

F

下降 时间 的 两个都 sda 和 scl 信号 t

8

0.3 µs

t

R

上升 时间 的 两个都 sda 和 scl 信号 t

9

0.3 µs

t

su;sto

建制 时间 为 停止 情况 t

10

0.6 µs

1

typicals 代表 平均readings 在 25°c 和 v

DD

= 5 v.

2

电阻 位置 非线性 错误 r-inl 是 这 背离 from 一个 完美的 值 量过的 between 这 最大 resistance 和 这最小 阻抗 wiper positions.

r-dnl measures 这 相关的 步伐 改变 从 完美的 在 successive tap positions. 部分 是 有保证的 monotonic.

3

V

AB

= v

DD

, wiper (v

W

) = 非 连接.

4

inl 和 dnl 是 量过的 在 v

W

和 这 rdac 配置 作 一个 分压器分隔物 类似的 至 一个 电压 输出 dac. v

一个

= v

DD

和 v

B

= 0 v. dnl 规格 限制 的

±1 lsb 最大 是 有保证的monotonic 运行 情况.

5

电阻 terminals 一个, b, w have 非 限制 在 极性和 遵守 至 各自 其它.

6

有保证的 用 设计 和 不 主题 至 生产 测试.

7

不同的 从 运行 电源 供应, power 供应 为 otp 是 使用 一个-时间 仅有的.

8

不同的 从 运行 电流, 供应 电流 为 otplasts 大概 400 ms for 一个-时间 needed 仅有的.

9

P

DISS

是 计算 从 (i

DD

× v

DD

). cmos 逻辑 水平的 输入 结果在 最小 电源 消耗.

10

带宽, 噪音, 和 安排好 时间 是 依赖 在 这 终端 阻抗 值 选择. 这 最低 r 值 结果 在 这 fastest 安排好 时间 和 最高的

带宽. 这 最高的 r 值 结果在 这 最小 overall 电源 消耗量.

11

所有 动态 characteristics 使用 v

DD

= 5 v.

12

不同的 从 安排好 时间 之后 fuse 是 blown. 这 otp 安排好 时间 occurs once 仅有的.

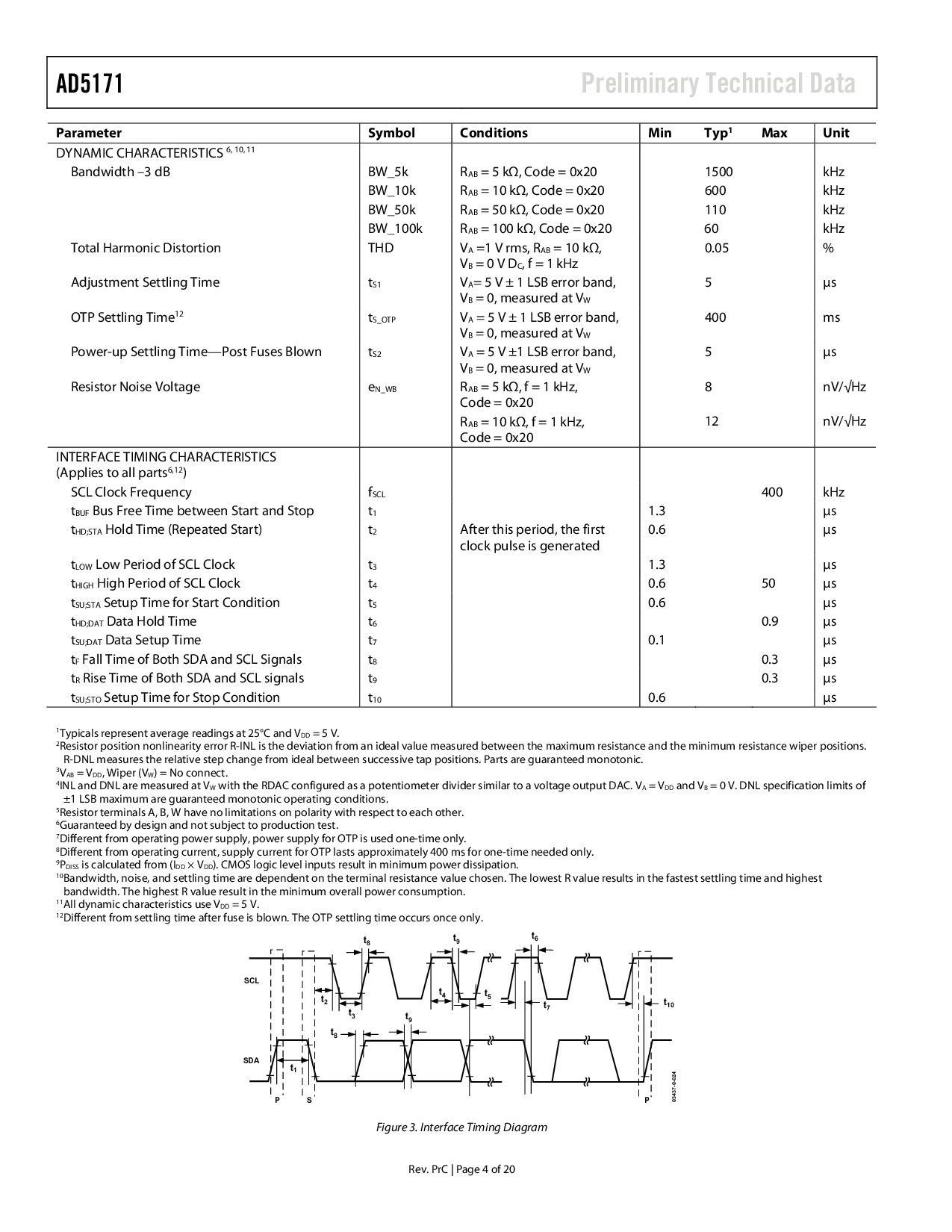

SCL

SDA

t

1

t

2

t

3

t

8

t

8

t

9

t

4

t

5

t

9

t

7

t

6

t

10

PPS

03437-0-024

图示 3. 接口 定时 图解

rev. prc | 页 4 的 20

初步的 技术的 数据