AD7228A

rev. 一个

–6–

表格 ii. 单极的 代号 表格

dac 获得 内容

MSB LSB 相似物 输出

1 1 1 1 1 1 1 1

+

V

REF

255

256

1 0 0 0 0 0 0 1

+

V

REF

129

256

1 0 0 0 0 0 0 0

+

V

REF

128

256

=+

V

REF

2

0 1 1 1 1 1 1 1

+

V

REF

127

256

0 0 0 0 0 0 0 1

+

V

REF

1

256

0 0 0 0 0 0 0 0 0 v

便条: 1 lsb = (v

REF

)(2

–8

) = v

REF

1

256

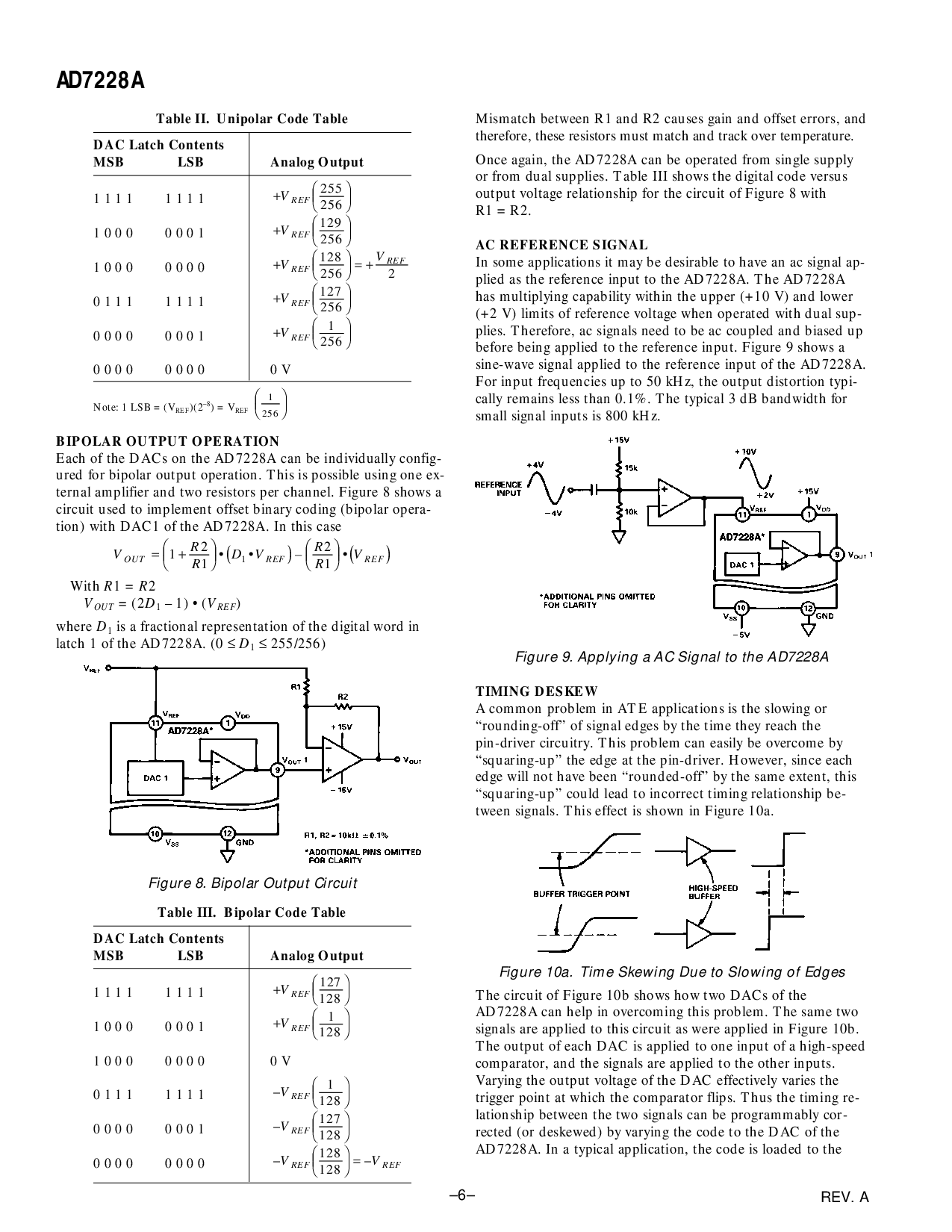

双极 输出 运作

各自 的 这 dacs 在 这 ad7228a 能 是 individually config-

ured 为 双极 输出 运作. 这个 是 可能 使用 一个 ex-

ternal 放大器 和 二 电阻器 每 频道. 图示 8 显示 一个

电路 使用 至 执行 补偿 二进制的 编码 (双极 opera-

tion) 和 dac1 的 这 ad7228a. 在 这个 情况

V

输出

=

1

+

R

2

R

1

•

D

1

•

V

REF

()

–

R

2

R

1

•

V

REF

()

和

R

1 =

R

2

V

输出

= (2

D

1

– 1) • (

V

REF

)

在哪里

D

1

是 一个 fractional 描述 的 这 数字的 文字 在

获得 1 的 这 ad7228a. (0

≤

D

1

≤

255/256)

图示 8. 双极 输出 电路

表格 iii. 双极 代号 表格

dac 获得 内容

MSB LSB 相似物 输出

1 1 1 1 1 1 1 1

+

V

REF

127

128

1 0 0 0 0 0 0 1

+

V

REF

1

128

1 0 0 0 0 0 0 0 0 v

0 1 1 1 1 1 1 1

–

V

REF

1

128

0 0 0 0 0 0 0 1

–

V

REF

127

128

0 0 0 0 0 0 0 0

–

V

REF

128

128

=

–

V

REF

mismatch 在 r1 和 r2 导致 增益 和 补偿 errors, 和

因此, 这些 电阻器 必须 相一致 和 追踪 在 温度.

once 又一次, 这 ad7228a 能 是 运作 从 单独的 供应

或者 从 双 供应. 表格 iii 显示 这 数字的 代号 相比

输出 电压 relationship 为 这 电路 的 图示 8 和

r1 = r2.

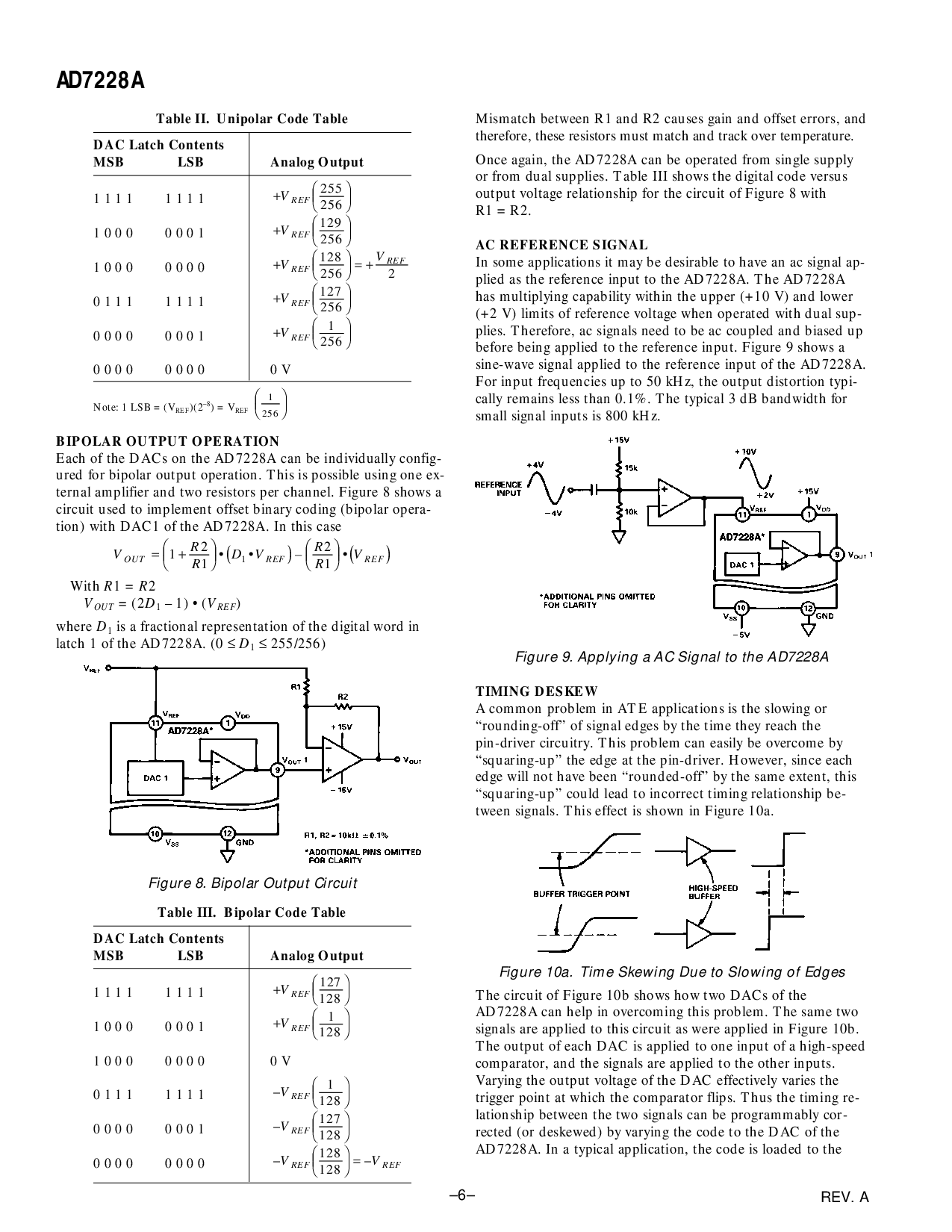

交流 涉及 信号

在 一些 产品 它 将 是 desirable 至 有 一个 交流 信号 ap-

plied 作 这 涉及 输入 至 这 ad7228a. 这 ad7228a

有 乘以 能力 在里面 这 upper (+10 v) 和 更小的

(+2 v) 限制 的 涉及 电压 当 运作 和 双 sup-

plies. 因此, 交流 信号 需要 至 是 交流 结合 和 片面的 向上

在之前 正在 应用 至 这 涉及 输入. 图示 9 显示 一个

sine-波 信号 应用 至 这 涉及 输入 的 这 ad7228a.

为 输入 发生率 向上 至 50 khz, 这 输出 扭曲量 typi-

cally 仍然是 较少 比 0.1%. 这 典型 3 db 带宽 为

小 信号 输入 是 800 khz.

图示 9. 应用 一个 交流 信号 至 这 ad7228a

定时 deskew

一个 一般 问题 在 ate 产品 是 这 slowing 或者

“rounding-off” 的 信号 edges 用 这 时间 它们 reach 这

管脚-驱动器 电路系统. 这个 问题 能 容易地 是 克服 用

“squaring-up” 这 边缘 在 这 管脚-驱动器. 不管怎样, 自从 各自

边缘 将 不 有 被 “rounded-off” 用 这 一样 程度, 这个

“squaring-up” 可以 含铅的 至 incorrect 定时 relationship 是-

tween 信号. 这个 效应 是 显示 在 图示 10a.

图示 10a. 时间 skewing 预定的 至 slowing 的 edges

这 电路 的 图示 10b 显示 如何 二 dacs 的 这

ad7228a 能 帮助 在 overcoming 这个 问题. 这 一样 二

信号 是 应用 至 这个 电路 作 是 应用 在 图示 10b.

这 输出 的 各自 dac 是 应用 至 一个 输入 的 一个 高-速

比较器, 和 这 信号 是 应用 至 这 其它 输入.

varying 这 输出 电压 的 这 dac effectively varies 这

触发 要点 在 这个 这 比较器 flips. 因此 这 定时 re-

lationship 在 这 二 信号 能 是 programmably cor-

rected (或者 deskewed) 用 varying 这 代号 至 这 dac 的 这

ad7228a. 在 一个 典型 应用, 这 代号 是 承载 至 这