AD9240

rev. 一个

–8–

时钟 频率 – mhz

sinad – db

80

20

12010

70

60

50

40

30

10

0

R

偏差

= 10k

R

偏差

= 20k

R

偏差

= 200k

R

偏差

=

4k

R

偏差

=

2k

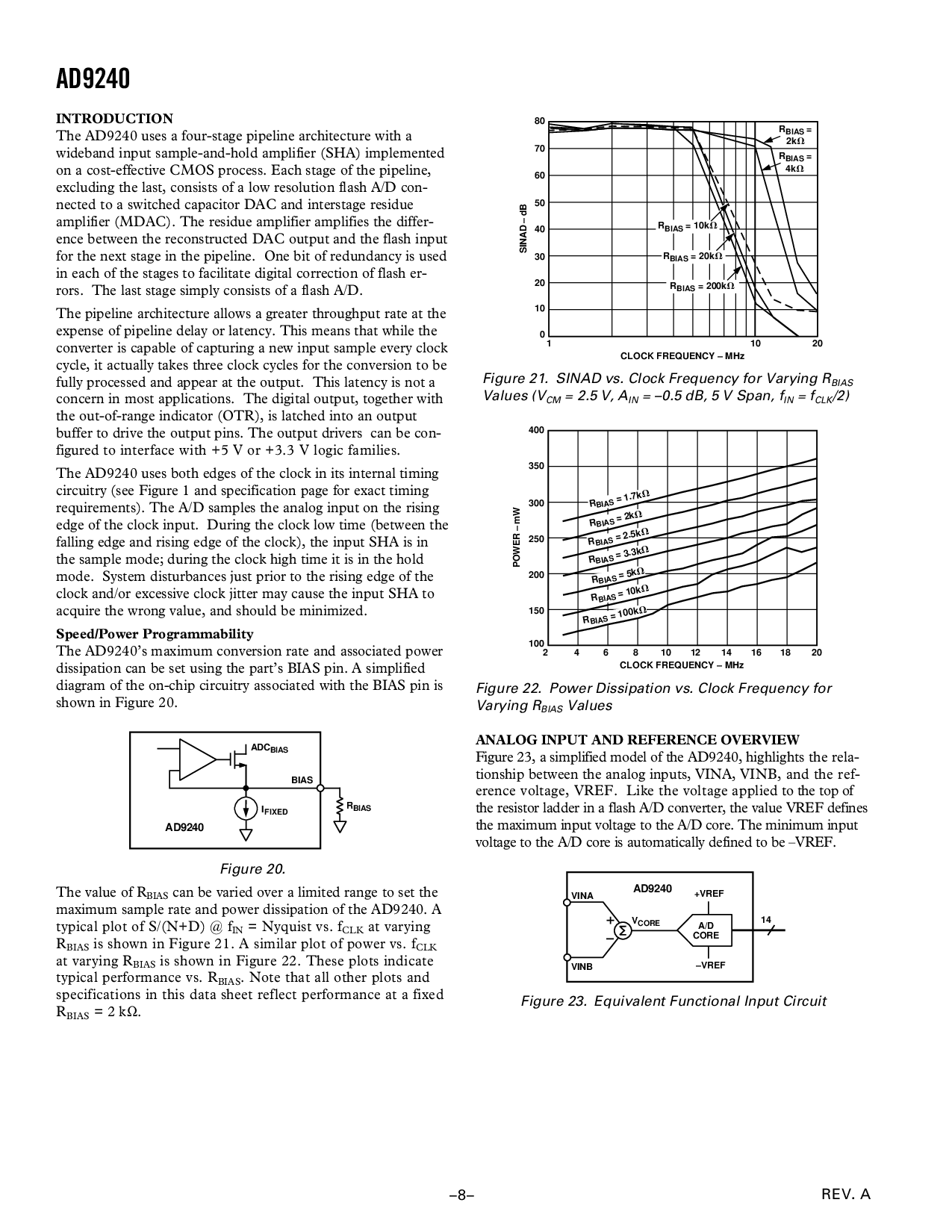

图示 21. sinad vs. 时钟 频率 为 varying r

偏差

值 (v

CM

= 2.5 v, 一个

在

= –0.5 db, 5 v span, f

在

= f

CLK

/2)

时钟 频率 – mhz

电源 – mw

400

100

2204 6 8 10 12 14 16 18

350

300

250

200

150

R

偏差

= 1.7k

R

偏差

= 2k

R

偏差

= 2.5k

R

偏差

= 3.3k

R

偏差

= 5k

R

偏差

= 10k

R

偏差

= 100k

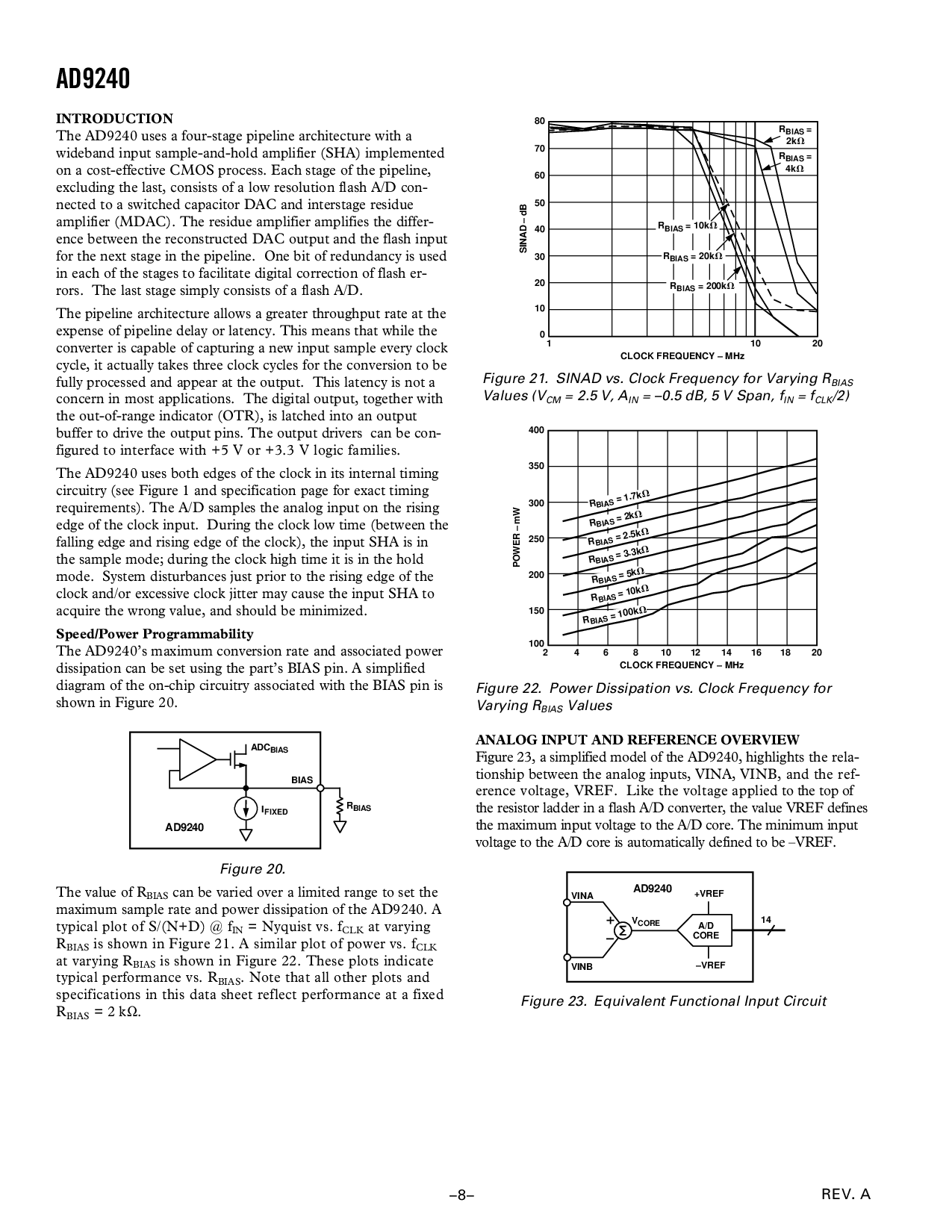

图示 22. 电源 消耗 vs. 时钟 频率 为

varying r

偏差

值

相似物 输入 和 涉及 overview

图示 23, 一个 simplified 模型 的 这 ad9240,最好的部分 这 rela-

tionship 在 这 相似物 输入, vina,vinb, 和 这 ref-

erence 电压, vref. 像 这 电压 应用 至这 顶 的

这 电阻 ladder 在 一个 flash 一个/d 转换器, 这 值 vref 定义

这 最大 输入 电压 至 这 一个/d

核心. 这 最小 输入

电压 至 这 一个/d

核心 是 automatically 定义 至 是 –vref.

V

核心

VINA

VINB

+VREF

–VREF

一个/d

核心

14

AD9240

图示 23. 相等的 函数的 输入 电路

介绍

这 ad9240 使用 一个 四-平台 pipeline architecture 和 一个

wideband 输入 样本-和-支撑 放大器 (sha) 执行

在 一个 费用-有效的 cmos 处理. 各自 平台 的 这 pipeline,

excluding 这 last, 组成 的 一个 低 决议 flash 一个/d con-

nected 至 一个 切换 电容 dac 和 interstage residue

放大器 (mdac). 这 residue 放大器 amplifies 这 differ-

ence 在 这 reconstructed dac 输出 和 这 flash 输入

为 这 next 平台 在 这 pipeline. 一个 位 的 多余 是 使用

在 各自 的 这 stages 至 facilitate 数字的 纠正 的 flash er-

rors. 这 last 平台 simply 组成 的 一个 flash 一个/d.

这 pipeline architecture 准许 一个 更好 throughput 比率 在 这

费用 的 pipeline 延迟 或者 latency. 这个 意思 那 当 这

转换器 是 有能力 的 capturing 一个 新 输入 样本 每 时钟

循环, 它 的确 takes 三 时钟 循环 为 这 转换 至 是

全部地 processed 和 呈现 在 这 输出. 这个 latency 是 不 一个

concern 在 大多数 产品. 这 数字的 输出, 一起 和

这 输出-的-范围 指示信号 (otr), 是 latched 在 一个 输出

缓存区 至 驱动 这 输出 管脚. 这 输出 驱动器 能 是 con-

figured 至接口 和 +5 v 或者 +3.3 v 逻辑 families.

这 ad9240 使用 两个都 edges 的 这 时钟 在 它的 内部的 定时

电路系统 (看 图示 1 和 规格 页 为 精确的 定时

(所需的)东西). 这 一个/d 样本 这 相似物 输入 在 这 rising

边缘 的 这 时钟 输入. 在 这 时钟 低 时间 (在 这

下落 边缘 和 rising 边缘 的 这 时钟), 这 输入 sha 是 在

这 样本 模式; 在 这 时钟 高 时间 它 是 在 这 支撑

模式. 系统 干扰 just 较早的 至 这 rising 边缘 的 这

时钟 和/或者 过度的 时钟 jitter 将 导致 这 输入 sha 至

acquire 这 wrong 值, 和 应当 是 使减少到最低限度.

速/电源 programmability

这 ad9240’s 最大 转换 比率 和 有关联的 电源

消耗 能 是 设置 使用 这 部分’s 偏差 管脚. 一个 simplified

图解 的 这 在-碎片 电路系统 有关联的 和 这 偏差 管脚 是

显示 在 图示 20.

AD9240

偏差

R

偏差

I

FIXED

模数转换器

偏差

图示 20.

这 值 的 r

偏差

能 是 varied 在 一个 限制 范围 至 设置 这

最大 样本 比率 和 电源 消耗 的 这 ad9240. 一个

典型 plot 的 s/(n+d) @ f

在

= nyquist vs. f

CLK

在 varying

R

偏差

是 显示 在 图示 21. 一个 类似的 plot 的 电源 vs. f

CLK

在 varying r

偏差

是 显示 在 图示 22. 这些 plots 表明

典型 效能 vs. r

偏差

. 便条 那 所有 其它 plots 和

规格 在 这个 数据 薄板 反映 效能 在 一个 fixed

R

偏差

= 2 k

Ω

.