8

®

AFE1104

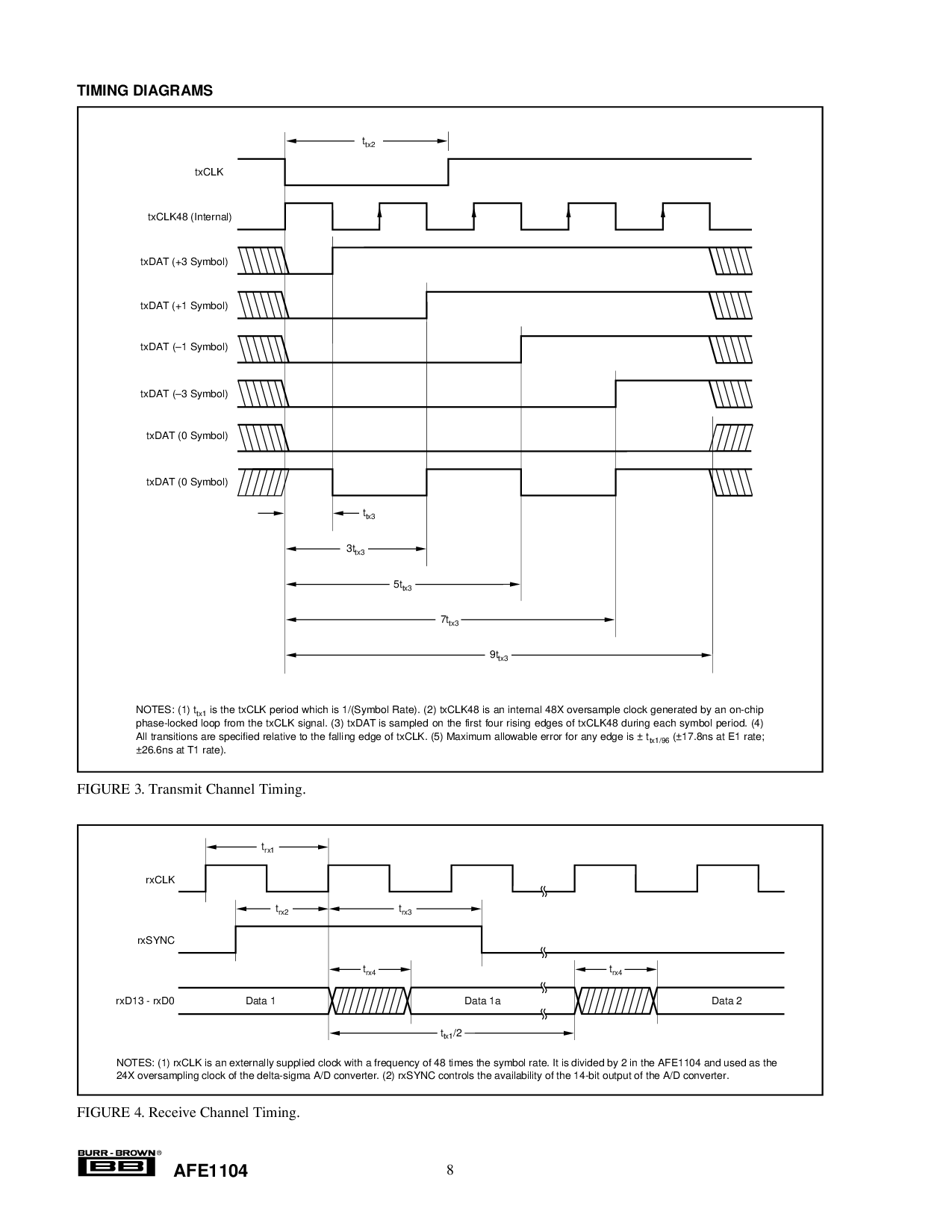

定时 图解

图示 3. transmit 频道 定时.

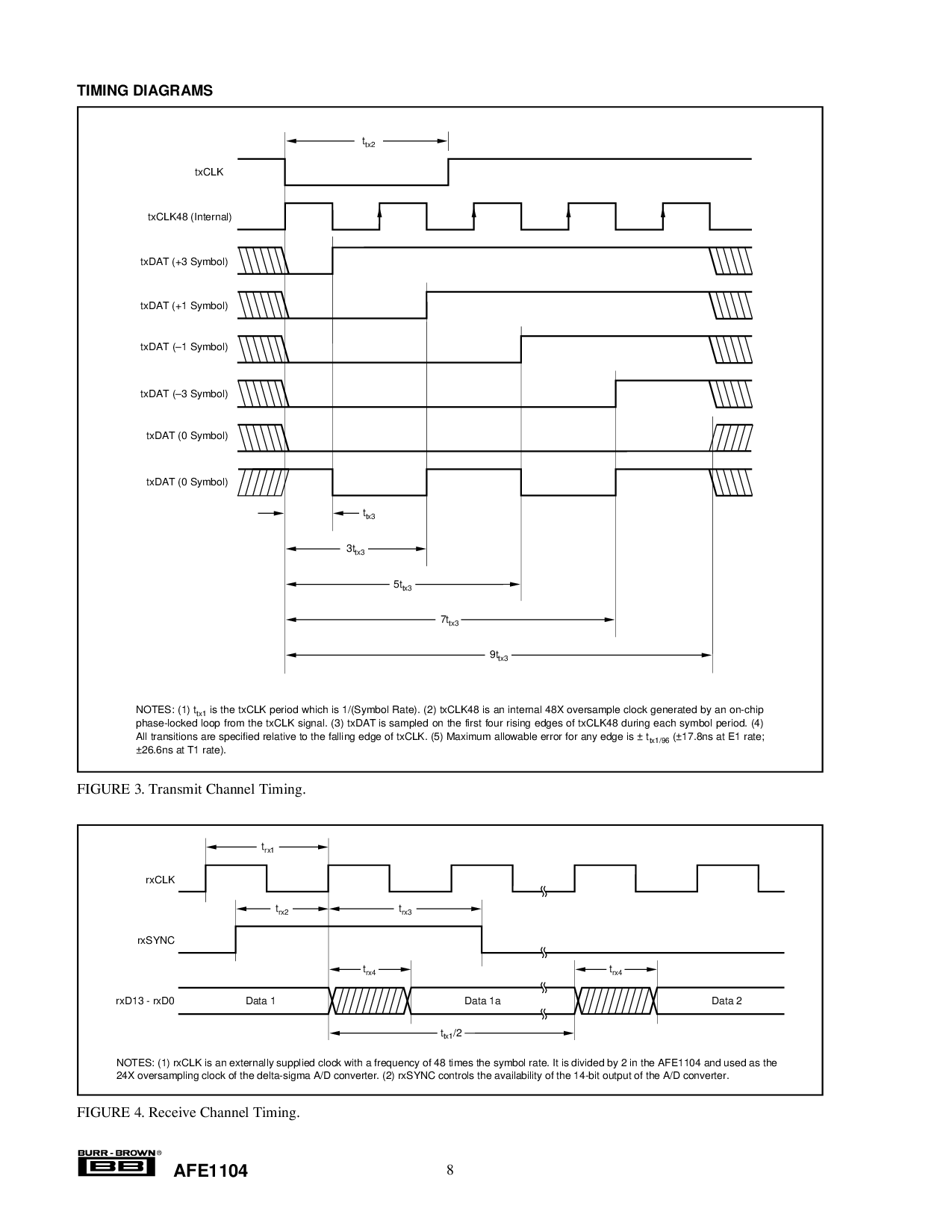

图示 4. receive 频道 定时.

t

tx2

t

tx3

3t

tx3

txCLK

txdat (+3 标识)

txdat (+1 标识)

txdat (–1 标识)

txdat (0 标识)

txclk48 (内部的)

5t

tx3

9t

tx3

txdat (–3 标识)

7t

tx3

txdat (0 标识)

注释: (1) t

tx1

是 这 txclk 时期 这个 是 1/(标识 比率). (2) txclk48 是 一个 内部的 48x oversample 时钟 发生 用 一个 在-碎片

阶段-锁 循环 从 这 txclk 信号. (3) txdat

是 抽样 在 这 第一 四 rising edges 的 txclk48 在 各自 标识 时期. (4)

所有 transitions 是 指定 相关的 至 这 下落 边缘 的 txclk. (5) 最大 容许的 错误 为 任何 边缘 是 ± t

tx1/96

(±17.8ns 在 e1 比率;

±26.6ns 在 t1 比率).

数据 1a

rxSYNC

rxd13 - rxd0 数据 1 数据 2

注释: (1) rxclk 是 一个 externally 有提供的 时钟 和 一个 频率 的 48 时间 这 标识 比率. 它 是 分隔 用 2 在 这 afe1104 和 使用 作 the

24x oversampling 时钟 的 这 delta-sigma 一个/d 转换器. (2) rxsync 控制 这 有效性 的 这 14-bit 输出 的 这 a/d converter.

rxCLK

t

rx3

t

rx4

t

rx4

t

tx1

/2

t

rx1

t

rx2