CS4341A

8 DS582PP1

3.3 系统 clocking

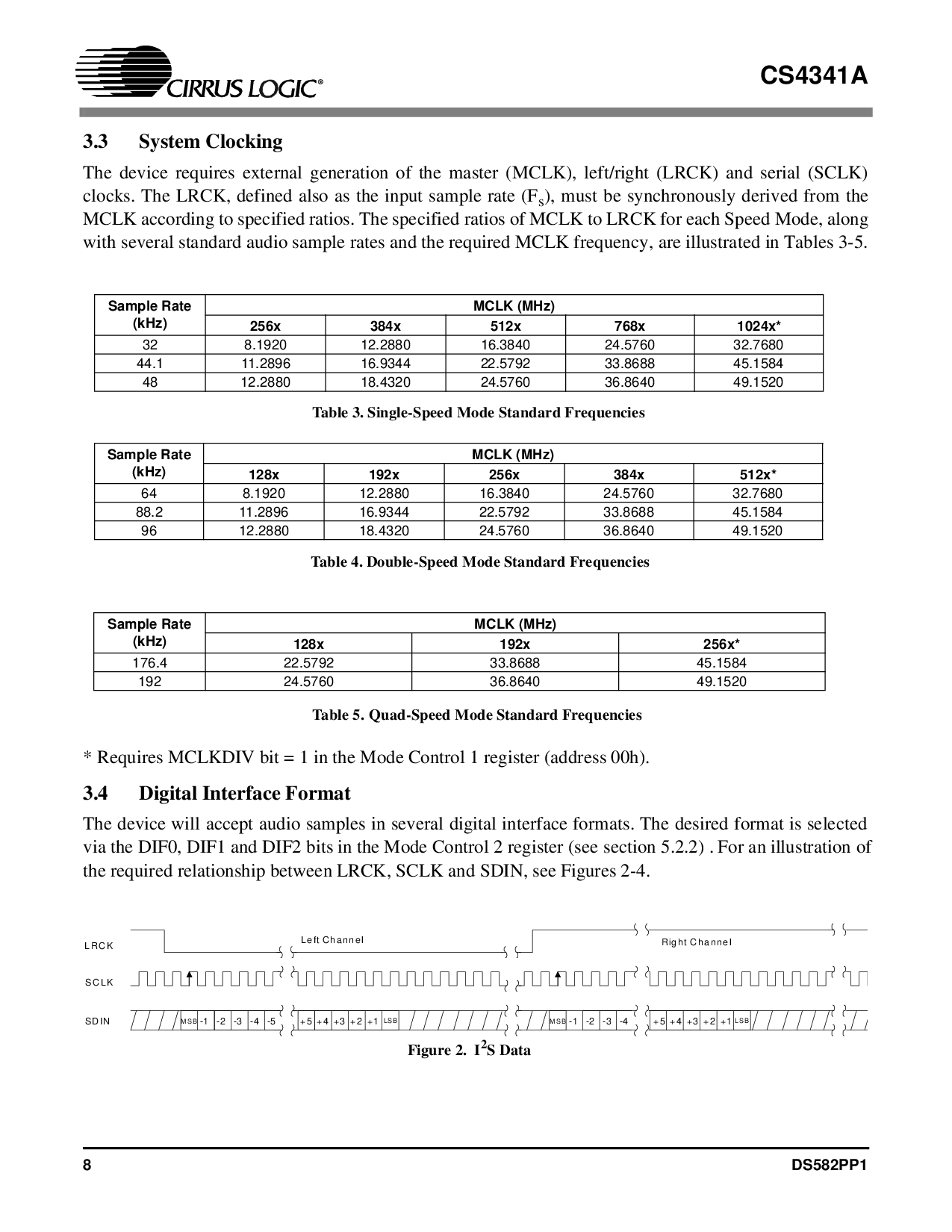

这 设备 需要 外部 一代 的 这 主控 (mclk), left/正确的 (lrck) 和 串行 (sclk)

clocks. 这 lrck, 定义 也 作 这 输入 样本 比率 (f

s

), 必须 是 synchronously 获得 从 这

mclk 符合 至 指定 ratios. 这 指定 ratios 的 mclk 至 lrck 为 各自 速 模式, along

和 一些 标准 音频的 样本 比率 和 这 必需的 mclk 频率, 是 illustrated 在 tables 3-5.

* 需要 mclkdiv 位 = 1 在 这 模式 控制 1 寄存器 (地址 00h).

3.4 数字的 接口 format

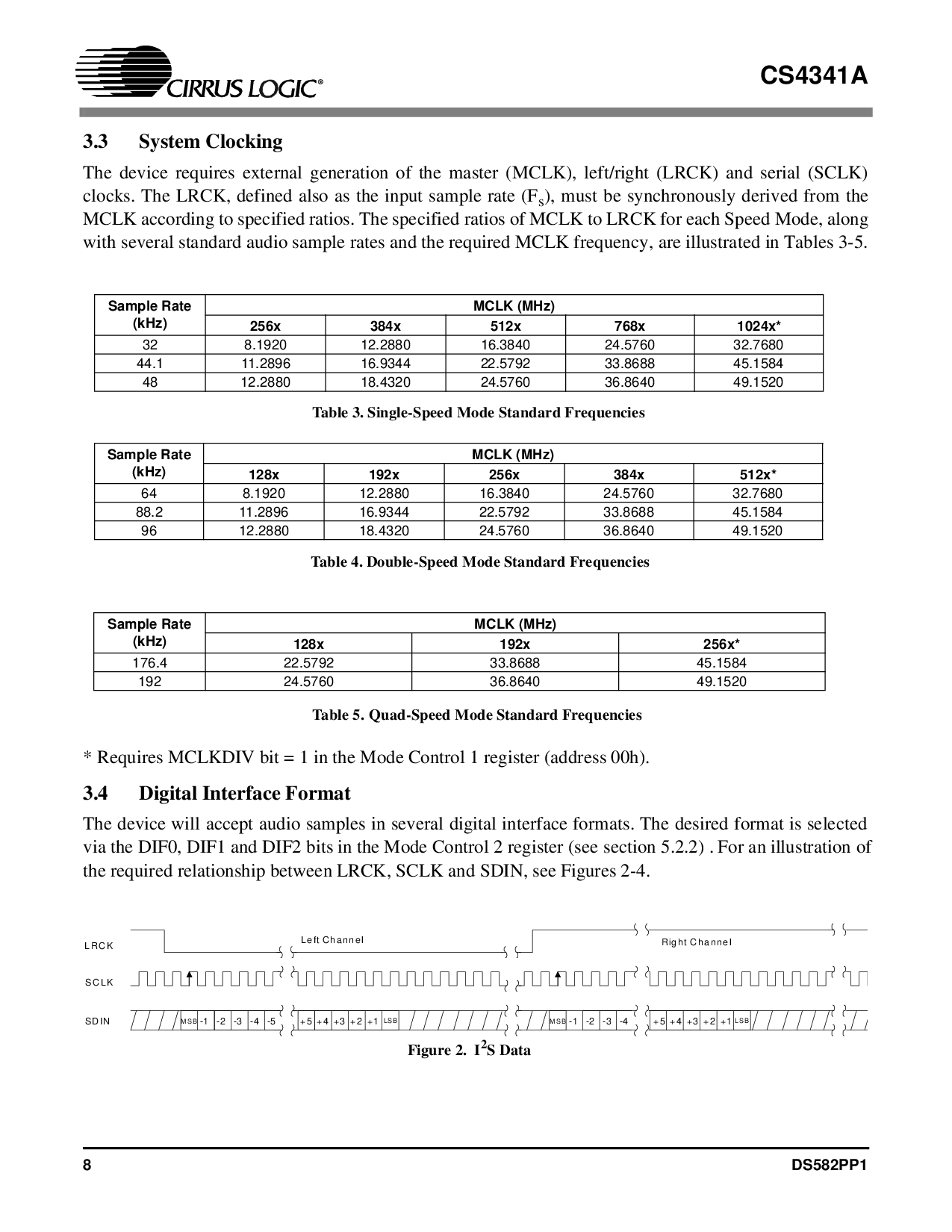

这 设备 将 接受 音频的 样本 在 一些 数字的 接口 formats. 这 desired format 是 选择

通过 这 dif0, dif1 和 dif2 位 在 这 模式 控制 2 寄存器 (看 部分 5.2.2) . 为 一个 illustration 的

这 必需的 relationship 在 lrck, sclk 和 sdin, 看 计算数量 2-4.

样本 比率

(khz)

mclk (mhz)

256x 384x 512x 768x 1024x*

32 8.1920 12.2880 16.3840 24.5760 32.7680

44.1 11.2896 16.9344 22.5792 33.8688 45.1584

48 12.2880 18.4320 24.5760 36.8640 49.1520

表格 3. 单独的-速 模式 标准 发生率

样本 比率

(khz)

mclk (mhz)

128x 192x 256x 384x 512x*

64 8.1920 12.2880 16.3840 24.5760 32.7680

88.2 11.2896 16.9344 22.5792 33.8688 45.1584

96 12.2880 18.4320 24.5760 36.8640 49.1520

表格 4. 翻倍-速 模式 标准 发生率

样本 比率

(khz)

mclk (mhz)

128x 192x 256x*

176.4 22.5792 33.8688 45.1584

192 24.5760 36.8640 49.1520

表格 5. 四方形-速 模式 标准 发生率

LRCK

SCLK

Left 频道

正确的 频道

SDIN +3 +2 +1+5 +4

MSB

-1 -2 -3 -4 -5

+3 +2 +1+5 +4

-1 -2 -3 -4

MSB

LSB

LSB

图示 2. i

2

s 数据