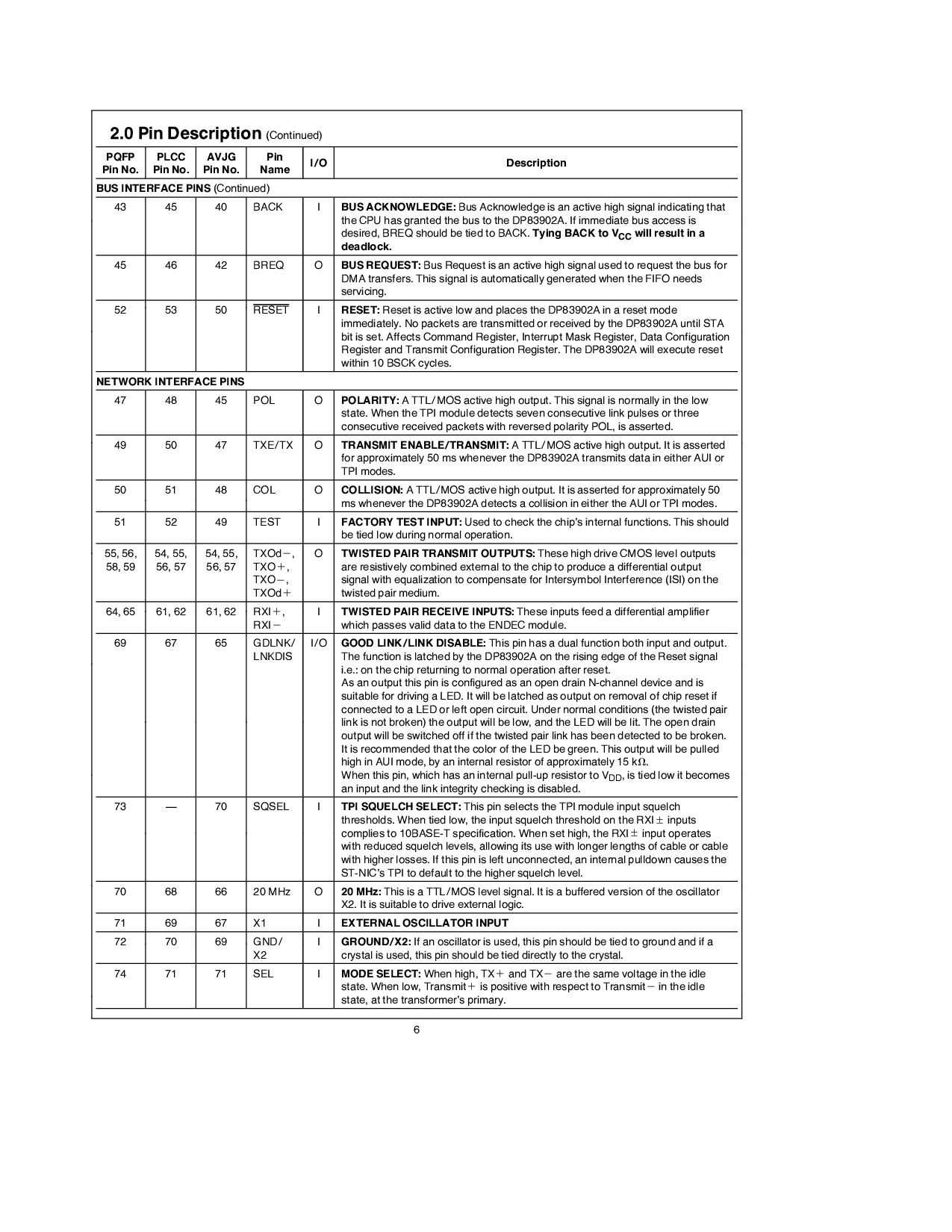

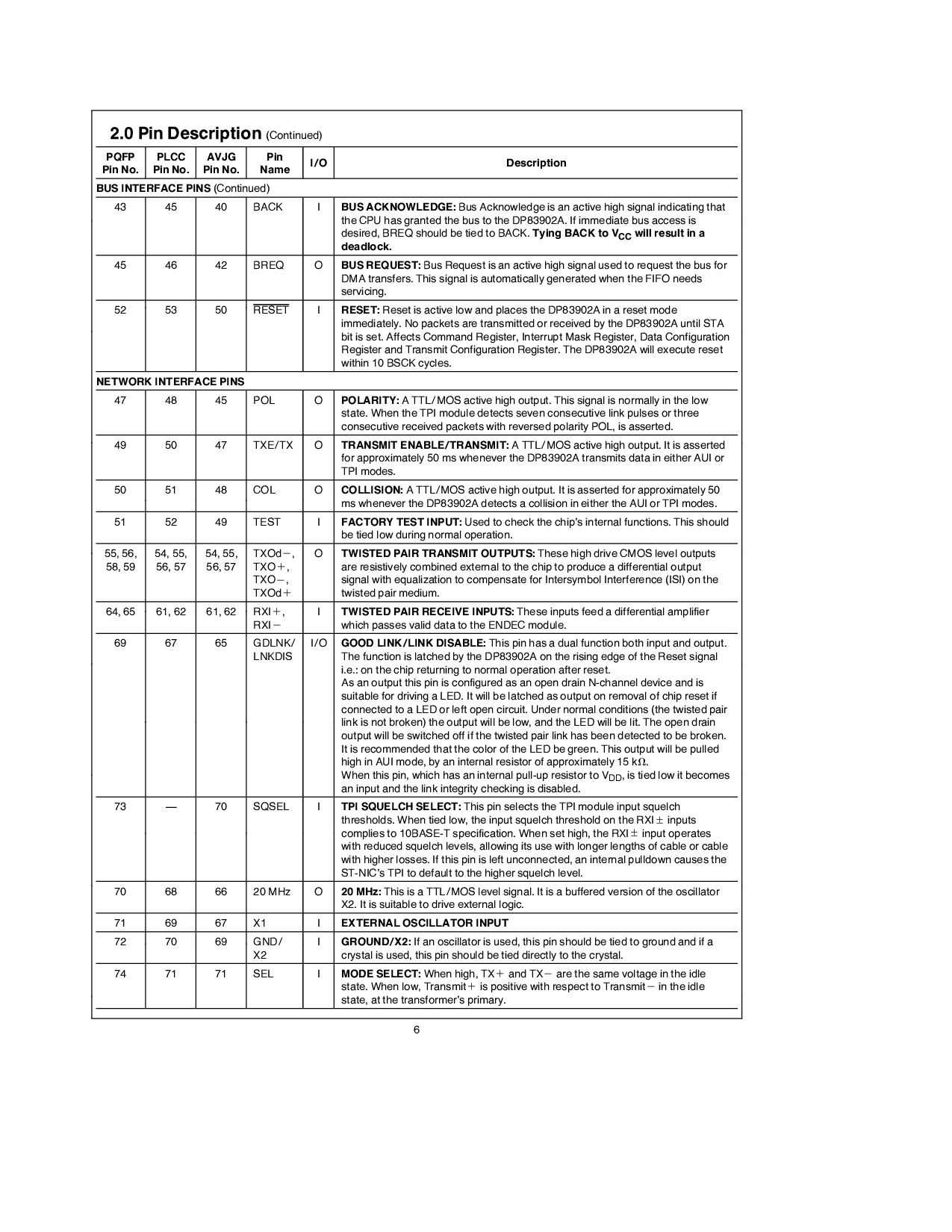

20 管脚 描述

(持续)

PQFP PLCC AVJG 管脚

IO 描述

管脚 No 管脚 No 管脚 No 名字

总线 接口 管脚

(持续)

43 45 40 后面的 I

总线 ACKNOWLEDGE

总线 Acknowledge 是 一个 起作用的 高 信号 表明 那

这 CPU 有 准予 这 总线 至 这 DP83902A 如果 立即的 总线 进入 是

desired BREQ 应当 是 系 至 BACK

Tying 后面的 至 V

CC

将 结果 在 一个

deadlock

45 46 42 BREQ O

总线 REQUEST

总线 要求 是 一个 起作用的 高 信号 使用 至 要求 这 总线 为

DMA transfers 这个 信号 是 automatically 发生 当 这 先进先出 needs

servicing

52 53 50 重置 I

RESET

重置 是 起作用的 低 和 places 这 DP83902A 在 一个 重置 模式

immediately 非 packets 是 transmitted 或者 received 用 这 DP83902A 直到 STA

位 是 set Affects Command Register 中断 掩饰 Register 数据 配置

寄存器 和 Transmit 配置 Register 这 DP83902A 将 execute 重置

在里面 10 BSCK cycles

网络 接口 管脚

47 48 45 POL O

POLARITY

一个 TTLMOS 起作用的 高 output 这个 信号 是 正常情况下 在 这 低

state 当 这 TPI 单元 发现 七 consecutive link 脉冲 或者 三

consecutive received packets 和 使反转 极性 POL 是 asserted

49 50 47 TXETX O

TRANSMIT ENABLETRANSMIT

一个 TTLMOS 起作用的 高 output 它 是 asserted

为 大概 50 ms whenever 这 DP83902A transmits 数据 在 也 AUI 或者

TPI modes

50 51 48 COL O

COLLISION

一个 TTLMOS 起作用的 高 output 它 是 asserted 为 大概 50

ms whenever 这 DP83902A 发现 一个 collision 在 也 这 AUI 或者 TPI modes

51 52 49 测试 I

工厂 测试 INPUT

使用 至 审查 这 chip’s 内部的 functions 这个 应当

是 系 低 在 正常的 operation

55 56 54 55 54 55 TXOd

b

O

TWISTED 一双 TRANSMIT OUTPUTS

这些 高 驱动 CMOS 水平的 输出

58 59 56 57 56 57 TXO

一个

是 resistively 联合的 外部 至 这 碎片 至 生产 一个 差别的 输出

TXO

b

信号 和 equalization 至 compensate 为 Intersymbol 干扰 (isi) 在 这

TXOd

一个

twisted 一双 medium

64 65 61 62 61 62 RXI

一个

I

TWISTED 一双 RECEIVE INPUTS

这些 输入 喂养 一个 差别的 放大器

RXI

b

这个 passes 有效的 数据 至 这 ENDEC module

69 67 65 GDLNK IO

好的 LINKLINK DISABLE

这个 管脚 有 一个 双 函数 两个都 输入 和 output

LNKDIS 这 函数 是 latched 用 这 DP83902A 在 这 rising 边缘 的 这 重置 信号

ie 在 这 碎片 returning 至 正常的 运作 之后 reset

作 一个 输出 这个 管脚 是 配置 作 一个 打开 流 n-频道 设备 和 是

合适的 为 驱动 一个 LED 它 将 是 latched 作 输出 在 除去 的 碎片 重置 如果

连接 至 一个 LED 或者 left 打开 circuit 下面 正常的 情况 (这 twisted 一双

link 是 不 broken) 这 输出 将 是 low 和 这 LED 将 是 lit 这 打开 流

输出 将 是 切换 止 如果 这 twisted 一双 link 有 被 发现 至 是 broken

它 是 推荐 那 这 颜色 的 这 LED 是 green 这个 输出 将 是 牵引的

高 在 AUI mode 用 一个 内部的 电阻 的 大概 15 k

X

当 这个 pin 这个 有 一个 内部的 拉-向上 电阻 至 V

DD

是 系 低 它 变为

一个 输入 和 这 link integrity checking 是 disabled

73 70 SQSEL I

TPI SQUELCH SELECT

这个 管脚 选择 这 TPI 单元 输入 squelch

thresholds 当 系 low 这 输入 squelch 门槛 在 这 RXI

g

输入

遵守 至 10base-t specification 当 设置 high 这 RXI

g

输入 运作

和 减少 squelch levels 准许 它的 使用 和 变长 长度 的 缆索 或者 缆索

和 高等级的 losses 如果 这个 管脚 是 left unconnected 一个 内部的 pulldown 导致 这

st-nic’s TPI 至 default 至 这 高等级的 squelch level

70 68 66 20 MHz O

20 MHz

这个 是 一个 TTLMOS 水平的 signal 它 是 一个 缓冲 版本 的 这 振荡器

X2 它 是 合适的 至 驱动 外部 logic

71 69 67 X1 I

外部 振荡器 输入

72 70 69 GND I

GROUNDX2

如果 一个 振荡器 是 used 这个 管脚 应当 是 系 至 地面 和 如果 一个

X2 结晶 是 used 这个 管脚 应当 是 系 直接地 至 这 crystal

74 71 71 SEL I

模式 SELECT

当 high TX

一个

和 TX

b

是 这 一样 电压 在 这 空闲

state 当 low Transmit

一个

是 积极的 和 遵守 至 Transmit

b

在 这 空闲

state 在 这 transformer’s primary

6