8442AY

www.icst.com/产品/hiperclocks.html

rev. c july 8, 2004

11

整体的

电路

系统, 公司

ICS8442

700MH

Z

, c

RYSTAL

O

SCILLATOR

-

至

-d

IFFERENTIAL

lvds f

REQUENCY

S

YNTHESIZER

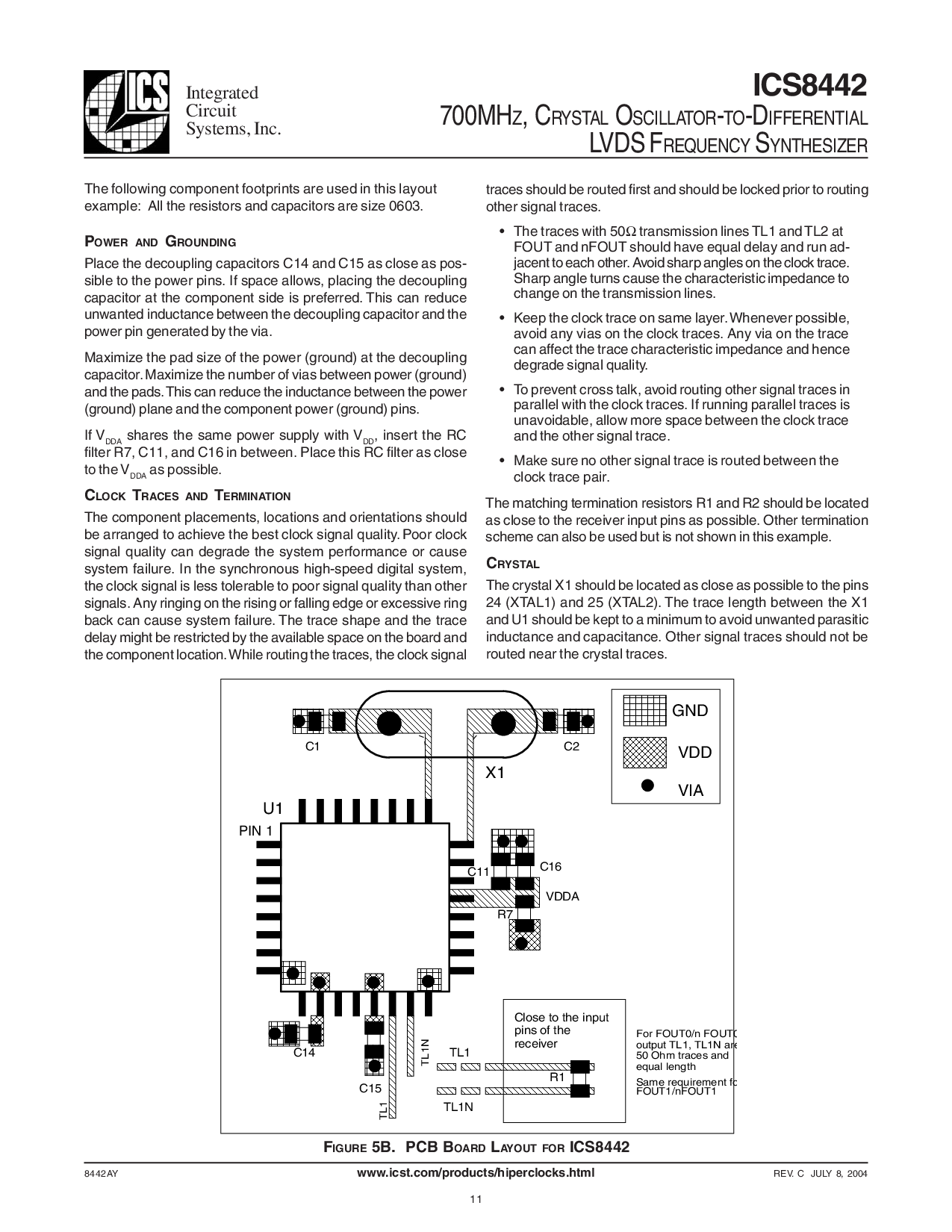

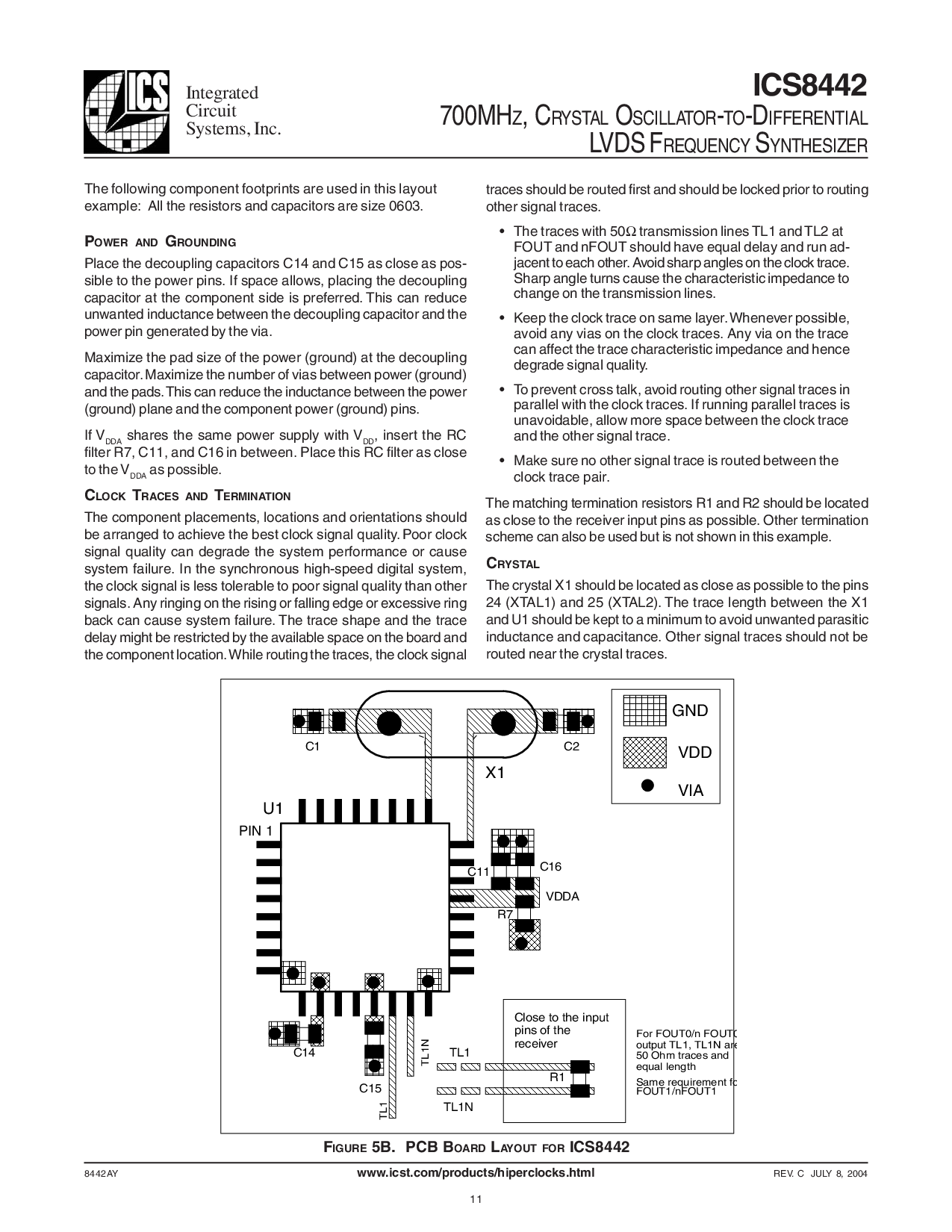

这 下列的 组件 footprints 是 使用 在 这个 布局

例子:所有 这 电阻器 和 电容 是 大小 0603.

P

OWER

和

G

ROUNDING

放置 这 解耦 电容 c14 和 c15 作 关闭 作 pos-

sible 至 这 电源 管脚. 如果 空间 准许, 放置 这 解耦

电容 在 这 组件 一侧 是 preferred. 这个 能 减少

unwanted 电感 在 这 解耦 电容 和 这

电源 管脚 发生 用 这 通过.

maximize 这 垫子 大小 的 这 电源 (地面) 在 这 解耦

电容. maximize 这 号码 的 vias 在 电源 (地面)

和 这 焊盘. 这个 能 减少 这 电感 在 这 电源

(地面) 平面 和 这 组件 电源 (地面) 管脚.

如果 v

DDA

shares 这 一样 电源 供应 和 v

DD

, insert 这 rc

过滤 r7, c11, 和 c16 在 在. 放置 这个 rc 过滤 作 关闭

至 这 v

DDA

作 可能.

C

锁

T

RACES

和

T

ERMINATION

这 组件 placements, locations 和 orientations 应当

是 arranged 至 达到 这 最好的 时钟 信号 质量. poor 时钟

信号 质量 能 降级 这 系统 效能 或者 导致

系统 失败. 在 这 同步的 高-速 数字的 系统,

这 时钟 信号 是 较少 tolerable 至 poor 信号 质量 比 其它

信号. 任何 ringing 在 这 rising 或者 下落 边缘 或者 过度的 环绕

后面的 能 导致 系统 失败. 这 查出 shape 和 这 查出

延迟 might 是 restricted 用 这 有 空间 在 这 板 和

这 组件 location. 当 routing 这 查出, 这 时钟 信号

查出 应当 是 routed 第一 和 应当 是 锁 较早的 至 routing

其它 信号 查出.

• 这 查出 和 50

Ω

传递 线条 tl1 和 tl2 在

fout 和 nfout 应当 有 equal 延迟 和 run ad-

jacent 至 各自 其它. 避免 sharp angles 在 这 时钟 查出.

sharp 角度 转变 导致 这 典型的 阻抗 至

改变 在 这 传递 线条.

• 保持 这 时钟 查出 在 一样 layer. whenever 可能,

避免 任何 vias 在 这 时钟 查出. 任何 通过 在 这 查出

能 影响 这 查出 典型的 阻抗 和 hence

降级 信号 质量.

• 至 阻止 交叉 表达, 避免 routing 其它 信号 查出 在

并行的 和 这 时钟 查出. 如果 运动 并行的 查出 是

unavoidable, 准许 更多 空间 在 这 时钟 查出

和 这 其它 信号 查出.

• 制造 确信 非 其它 信号 查出 是 routed 在 这

时钟 查出 一双.

这 相一致 末端 电阻器 r1 和 r2 应当 是 located

作 关闭 至 这 接受者 输入 管脚 作 可能. 其它 末端

scheme 能 也 是 使用 但是 是 不 显示 在 这个 例子.

C

RYSTAL

这 结晶 x1 应当 是 located 作 关闭 作 可能 至 这 管脚

24 (xtal1) 和 25 (xtal2). 这 查出 长度 在 这 x1

和 u1 应当 是 保持 至 一个 最小 至 避免 unwanted parasitic

电感 和 电容. 其它 信号 查出 应当 不 是

routed near 这 结晶 查出.

F

IGURE

5b. pcb b

OARD

L

AYOUT

为

ICS8442

VDD

TL1

C15

C14

R1

一样 必要条件 fo

fout1/nfout1

VDDA

关闭 至 这 输入

管脚 的 这

接受者

R7

X1

C2

为 fout0/n fout0

输出 tl1, tl1n are

50 ohm 查出 和

equal 长度

通过

地

TL1N

TL1

管脚 1

U1

C1

TL1N

C11

C16