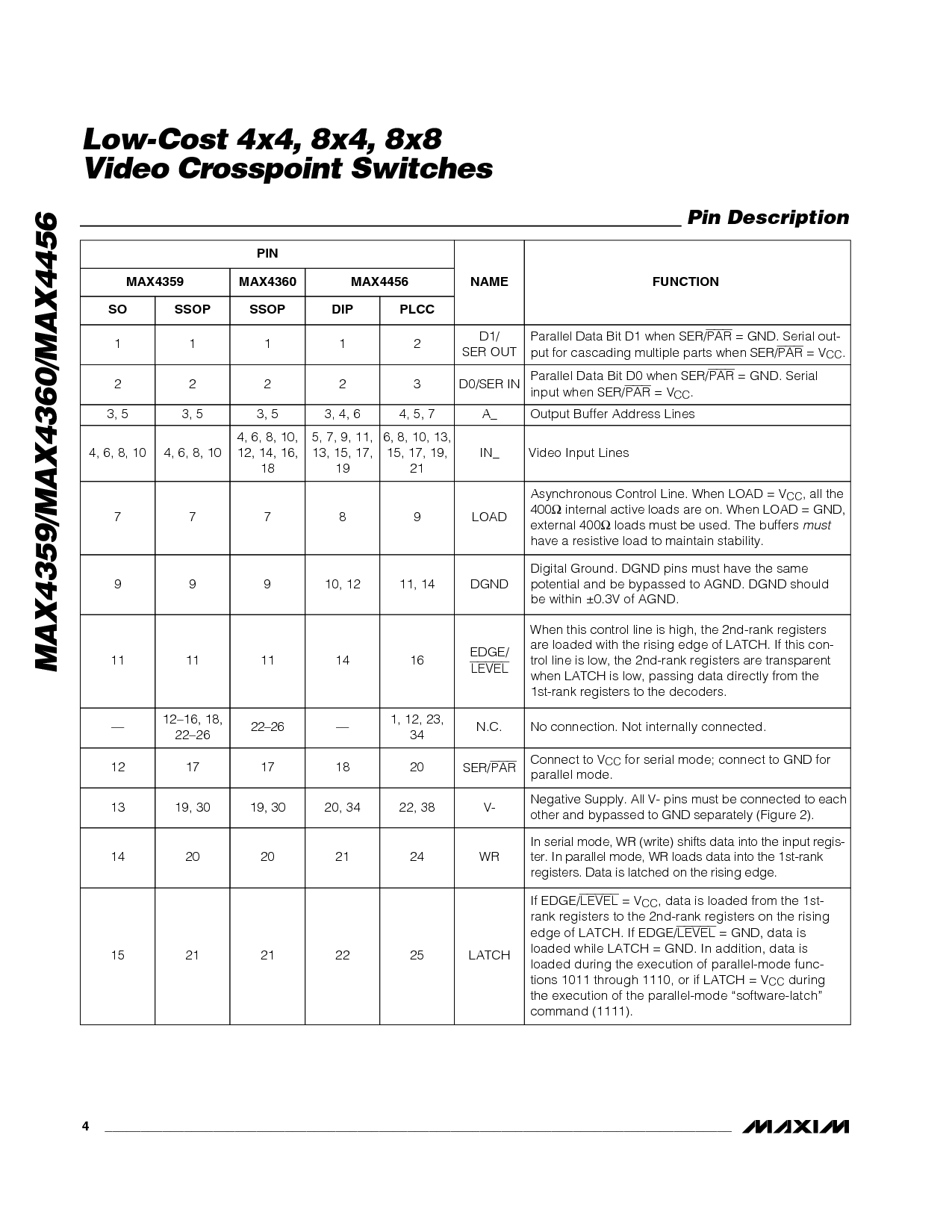

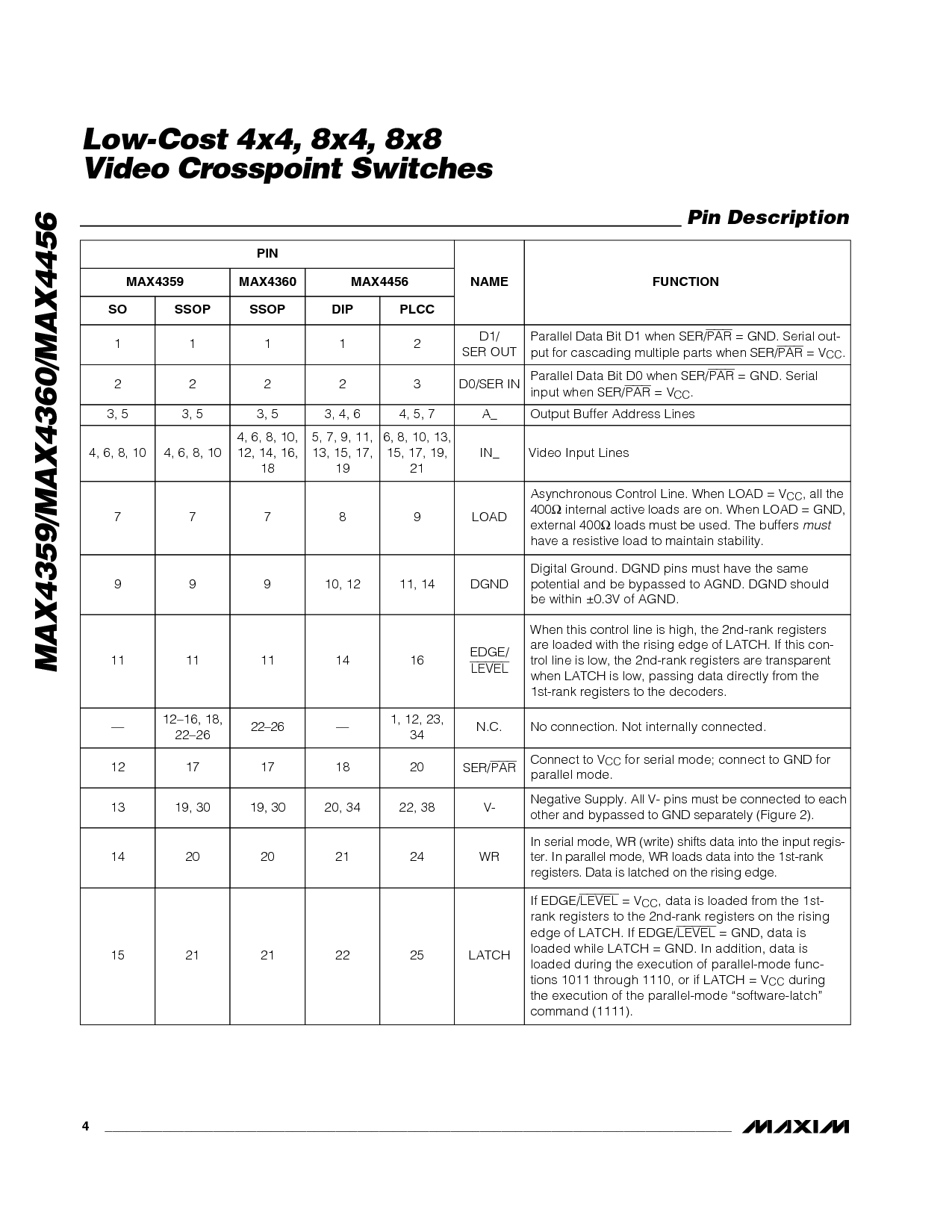

max4359/max4360/max4456

低-费用 4x4, 8x4, 8x8

video crosspoint switches

4 _______________________________________________________________________________________

管脚 描述

2 2 2

并行的 数据 位 d0 当 ser/

PAR

= 地. 串行

输入 当 ser/

PAR

= v

CC

.

3, 5 3, 5 3, 5 输出 缓存区 地址 线条

4, 6, 8, 10 4, 6, 8, 10

4, 6, 8, 10,

12, 14, 16,

18

video 输入 线条

7 7 7

异步的 控制 线条. 当 加载 = v

CC

, 所有 这

400

Ω

内部的 起作用的 负载 是 在. 当 加载 = 地,

外部 400

Ω

负载 必须 是 使用. 这 缓存区

必须

有 一个 resistive 加载 至 维持 稳固.

9 9 9

数字的 地面. dgnd 管脚 必须 有 这 一样

潜在的 和 是 绕过 至 agnd. dgnd 应当

是 在里面 ±0.3v 的 agnd.

11 11 11

当 这个 控制 线条 是 高, 这 2nd-分级 寄存器

是 承载 和 这 rising 边缘 的 获得. 如果 这个 con-

trol 线条 是 低, 这 2nd-分级 寄存器 是 transparent

当 获得 是 低, passing 数据 直接地 从 这

1st-分级 寄存器 至 这 decoders.

—

12–16, 18,

22–26

22–26 非 连接. 不 内部 连接.

12 17 17

连接 至 v

CC

为 串行 模式; 连接 至 地 为

并行的 模式.

13 19, 30 19, 30

负的 供应. 所有 v- 管脚 必须 是 连接 至 各自

其它 和 绕过 至 地 separately (图示 2).

14 20 20

在 串行 模式, wr (写) shifts 数据 在 这 输入 regis-

ter. 在 并行的 模式, wr 负载 数据 在 这 1st-分级

寄存器. 数据 是 latched 在 这 rising 边缘.

1 21 1 1

并行的 数据 位 d1 当 ser/

PAR

= 地. 串行 输出-

放 为 cascading 多样的 部分 当 ser/

PAR

= v

CC

.

d1/

ser 输出

2 3

3, 4, 6 4, 5, 7

5, 7, 9, 11,

13, 15, 17,

19

6, 8, 10, 13,

15, 17, 19,

21

8 9

10, 12 11, 14

14 16

—

1, 12, 23,

34

18 20

20, 34 22, 38

21 24

d0/ser 在

一个_

在_

加载

DGND

边缘/

水平的

n.c.

ser/

PAR

v-

WR

MAX4360 MAX4456MAX4359

插件 PLCC所以 SSOP SSOP

FUNCTIONNAME

管脚

15 21 21

如果 边缘/

水平的

= v

CC

, 数据 是 承载 从 这 1st-

分级 寄存器 至 这 2nd-分级 寄存器 在 这 rising

边缘 的 获得. 如果 边缘/

水平的

= 地, 数据 是

承载 当 获得 = 地. 在 增加, 数据 是

承载 在 这 执行 的 并行的-模式 func-

tions 1011 通过 1110, 或者 如果 获得 = v

CC

在

这 执行 的 这 并行的-模式 “software-latch”

command (1111).

22 25 获得