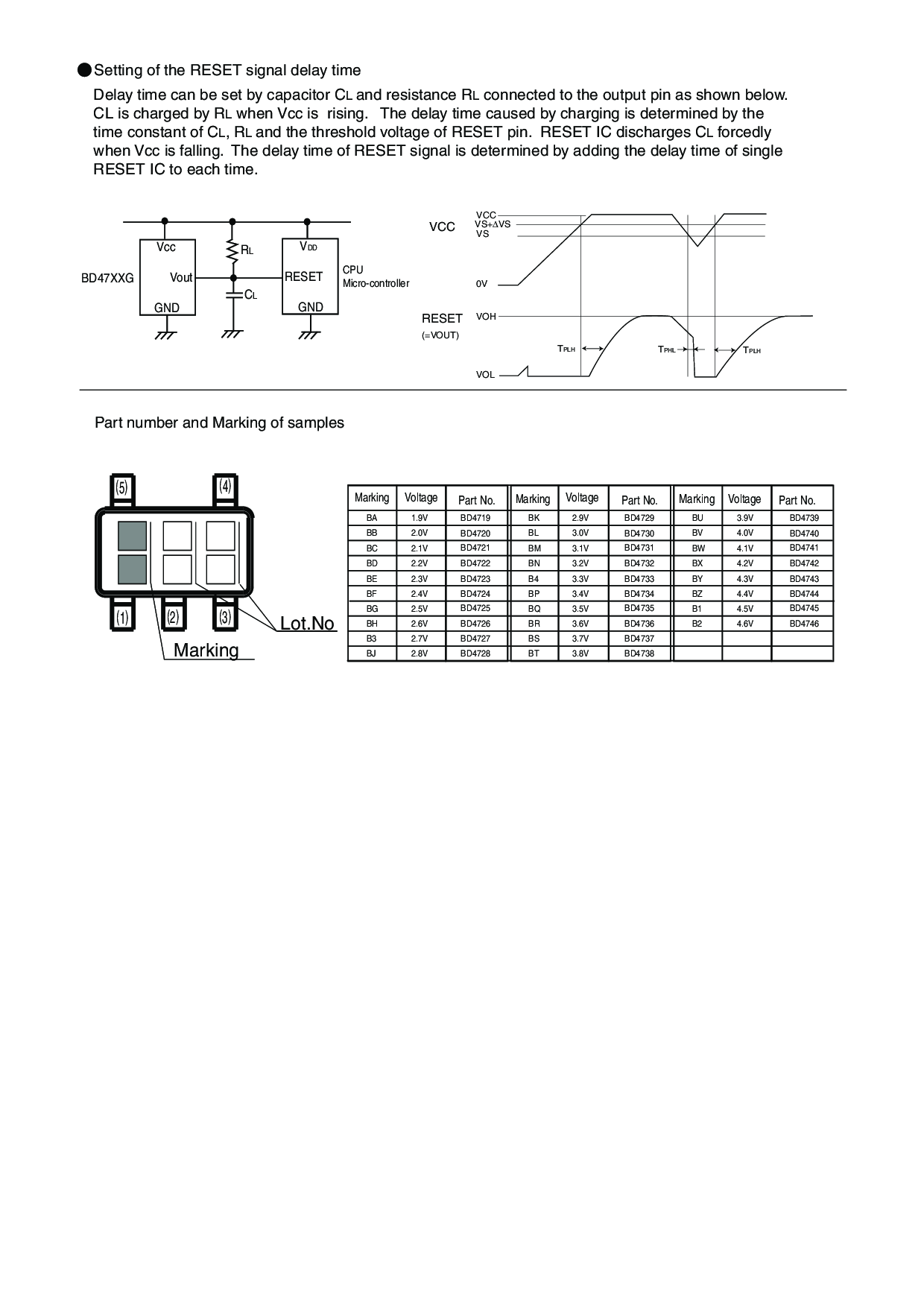

设置 的 这 重置 信号 延迟 时间

延迟 时间 能 是 设置 用 电容 c

L

和 阻抗 r

L

连接 至 这 输出 管脚 作 显示 在下.

cl 是 charged 用 r

L

当 vcc 是 rising. 这 延迟 时间 造成 用 charging 是 决定 用 这

时间 常量 的 c

L

, r

L

和 这 门槛 电压 的 重置 管脚. 重置 ic discharges c

L

forcedly

当 vcc 是 下落. 这 延迟 时间 的 重置 信号 是 决定 用 adding 这 延迟 时间 的 单独的

重置 ic 至 各自 时间.

地

地

Vcc

V

DD

C

L

Vout

重置

BD47XXG

CPU

微观的-控制

R

L

VCC

VCC

重置

(=vout)

VS

0V

VOH

T

PLH

T

PLH

VOL

VS+

∆

VS

T

PHL

标记

电压

部分 非. 部分 非. 部分 非.

标记

标记

电压

电压

BD4719BA

BB

BC

BD

是

BF

BG

BH

B3

BJ

1.9v

2.0v

2.1v

2.2v

2.3v

2.4v

2.5v

2.6v

2.7v

2.8v

BK

BL

BM

BN

B4

BP

BQ

BR

BS

BT

2.9v

3.0v

3.1v

3.2v

3.3v

3.4v

3.5v

3.6v

3.7v

3.8v

BU

BV

BW

BX

用

BZ

B1

B2

3.9v

4.0v

4.1v

4.2v

4.3v

4.4v

4.5v

4.6v

BD4729

BD4720

BD4721

BD4722

BD4723

BD4724

BD4725

BD4726

BD4727

BD4728

BD4730

BD4731

BD4732

BD4733

BD4734

BD4735

BD4736

BD4737

BD4738

BD4739

BD4740

BD4741

BD4742

BD4743

BD4744

BD4745

BD4746

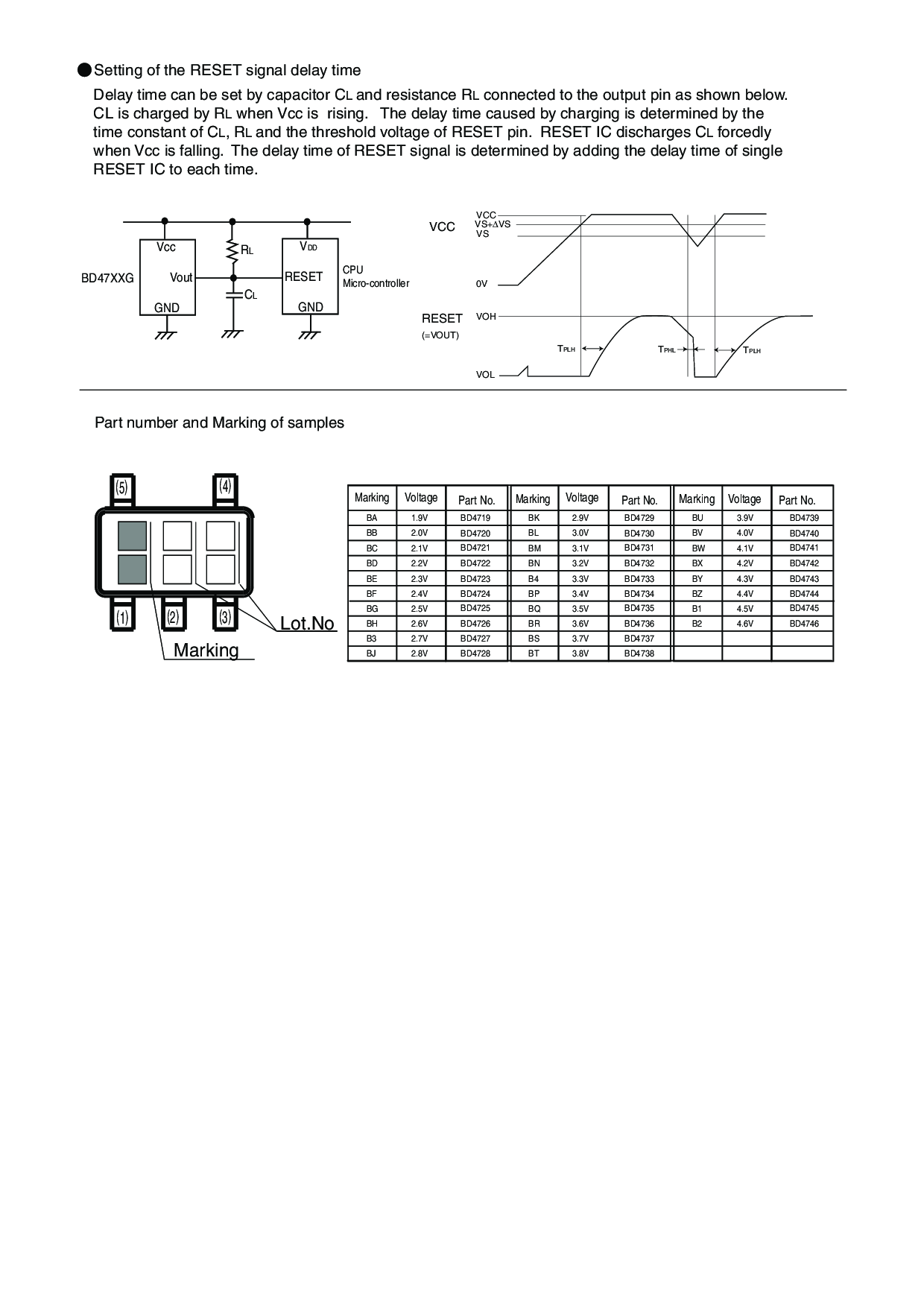

部分 号码 和 标记 的 样本

(

5

)

(

4

)

(

3

)

(

2

)

(

1

)

标记

lot.非