br24c08 / br24c08f / br24c08fj / br24c08fv / br24c16/ br24c16f /

记忆 ics

br24c16fj /

br24c16fv / br24e16 / br24e16f / br24e16fj / br24e16fv

z

zz

z

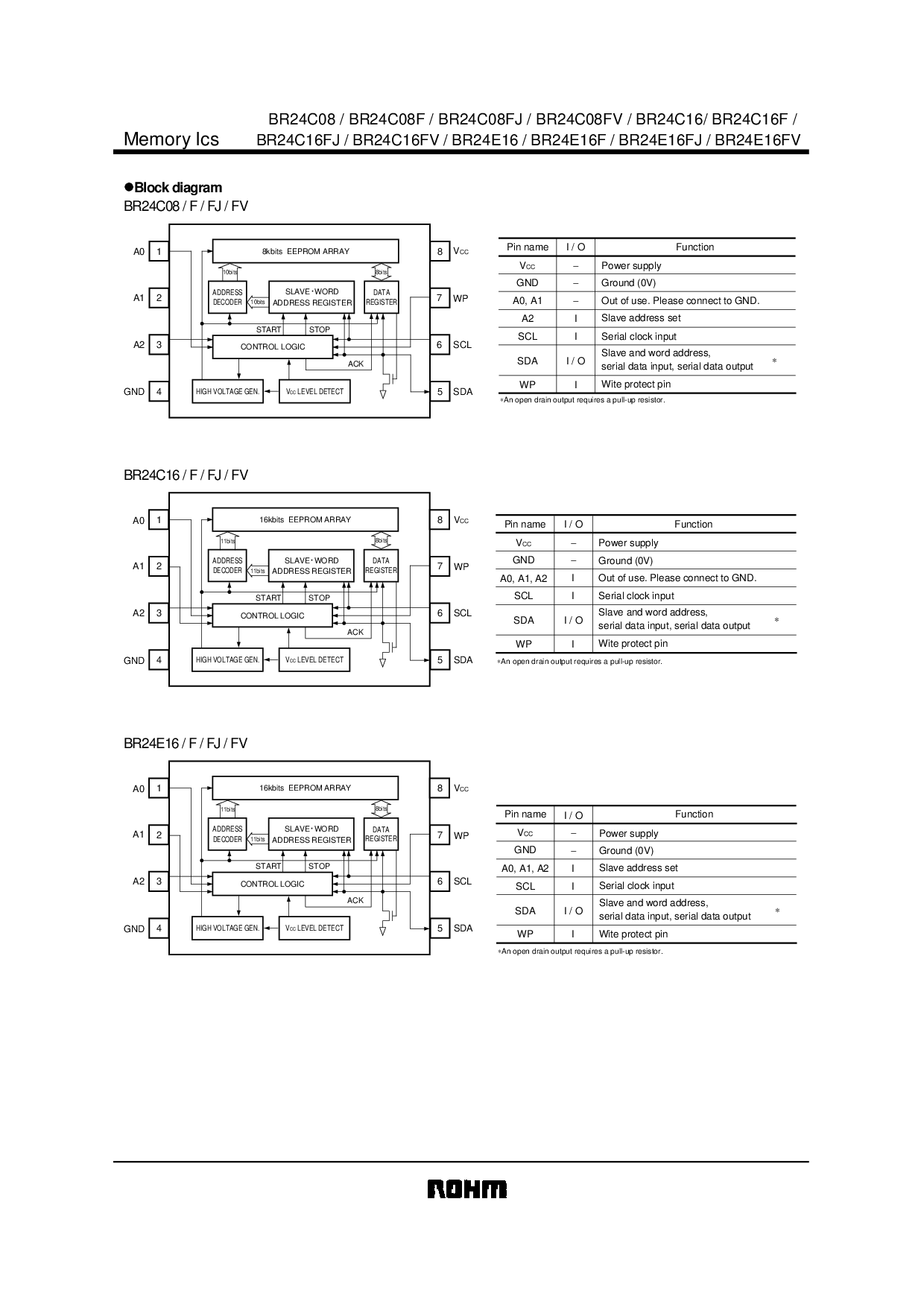

块 图解

br24c08 / f / fj / fv

8kbits 可擦可编程只读存储器 排列

控制 逻辑

高 电压 gen.

ACK

开始 停止

10bits

10bits

8bits

数据

寄存器

地址

解码器

A0

A1

A2

1

2

3

4

地

WP

SCL

SDA

8

7

6

5

V

CC

V

CC

水平的 发现

地址 寄存器

从动装置 文字

·

函数

从动装置 地址 设置

串行 时钟 输入

串行 数据 输入, 串行 数据 输出

wite 保护 管脚

电源 供应

管脚 名字

a0, a1

A2

SCL

SDA

WP

V

CC

地

i / o

i / o

−

−

−

I

I

I

地面 (0v)

输出 的 使用. 请 连接 至 地.

从动装置 和 文字 地址,

∗

一个 打开 流 输出 需要 一个 拉-向上 电阻.

∗

br24c16 / f / fj / fv

16kbits 可擦可编程只读存储器 排列

控制 逻辑

高 电压 gen.

ACK

开始 停止

11bits

8bits

数据

寄存器

地址

解码器

A0

A1

A2

1

2

3

4

地

WP

SCL

SDA

8

7

6

5

V

CC

V

CC

水平的 发现

地址 寄存器

从动装置 文字

·

11bits

a0, a1, a2

SCL

SDA

WP

V

CC

地

i / o

i / o

−

−

I

I

I

functionpin 名字

∗

一个 打开 流 输出 需要 一个 拉-向上 电阻.

串行 时钟 输入

串行 数据 输入, 串行 数据 输出

wite 保护 管脚

电源 供应

地面 (0v)

输出 的 使用. 请 连接 至 地.

从动装置 和 文字 地址,

∗

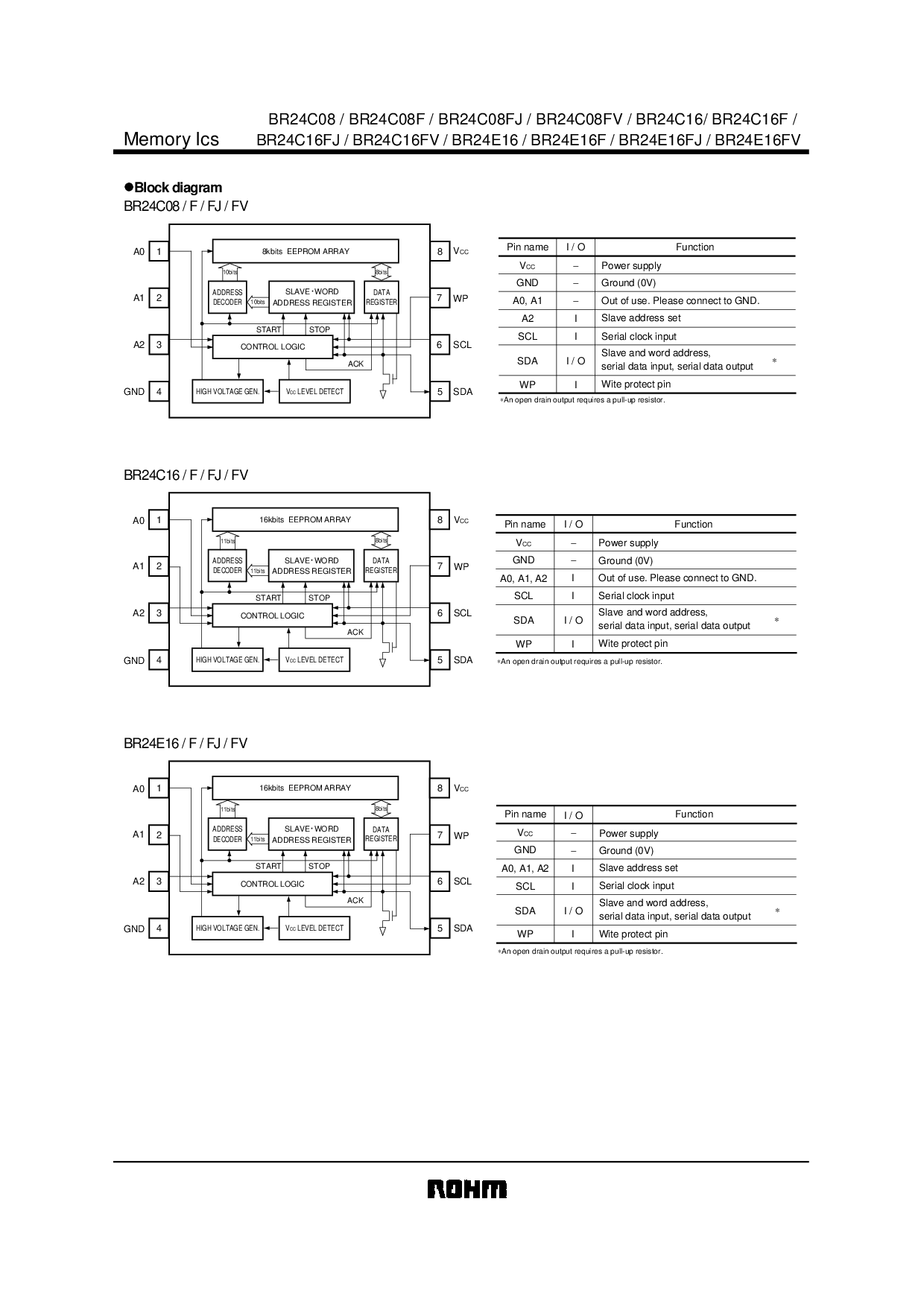

br24e16 / f / fj / fv

16kbits 可擦可编程只读存储器 排列

控制 逻辑

高 电压 gen.

ACK

开始 停止

11bits

8bits

数据

寄存器

地址

解码器

A0

A1

A2

1

2

3

4

地

WP

SCL

SDA

8

7

6

5

V

CC

V

CC

水平的 发现

地址 寄存器

从动装置 文字

·

11bits

a0, a1, a2

SCL

SDA

WP

V

CC

地

i / o

i / o

−

−

I

I

I

functionpin 名字

∗

一个 打开 流 输出 需要 一个 拉-向上 电阻.

串行 时钟 输入

串行 数据 输入, 串行 数据 输出

wite 保护 管脚

电源 供应

地面 (0v)

从动装置 和 文字 地址,

∗

从动装置 地址 设置