512k x 36 / 1 mb x 18 pipelined sram

CY7C1380BV25

CY7C1382BV25

初步的

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

july 5, 2001

1CY7C1380BV25

特性

• 快 时钟 速: 200,166, 150, 133 mhz

• 提供 高-效能 3-1-1-1 进入 比率

•fast oe

进入 时间: 3.0,3.2, 3.4, 3.8, 4.2 ns

• 最优的 为 depth expansion

• 2.5v (±5%) 运作

• 一般 数据 输入 和 数据 输出

• 字节 写 使能 和 global 写 控制

• 碎片 使能 为 地址 pipeline

• 地址, 数据, 和 控制 寄存器

• 内部 自-安排时间 写 循环

• burst 控制 管脚 (interleaved 或者 直线的 burst se-

quence)

• 自动 电源-向下 为 可携带的 产品

• 高-密度, 高-速 包装

• jtag boundary scan 为 bga 包装 版本

函数的 描述

这 cypress 同步的 burst sram 家族 雇用

高-速, 低-电源 cmos 设计 使用 先进的 sin-

gle-layer polysilicon, triple-layer metal 技术. 各自 mem-

ory cell 组成 的 六 晶体管.

这 cy7c1382bv25 和 cy7c1380bv25 srams 合并

1,048,576x18 和 524,288x36 sram cells 和 先进的

同步的 附带的 电路系统 和 一个 2-位 计数器 为 inter-

nal burst 运作. 所有 同步的 输入 是 gated 用 reg-

isters 控制 用 一个 积极的-边缘-triggered 时钟 输入

(clk). 这 同步的 输入 包含 所有 地址, 所有 数据

输入, 地址-pipelining 碎片 使能 (ce

), burst 控制 在-

puts (adsc, adsp, 和 adv), 写 使能 (bw一个, bwb,

BW

c, bwd 和 bwe), 和 global 写 (gw).

异步的 输入 包含 这 输出 使能 (oe) 和 burst

模式 控制 (模式). 这 数据 (dq

一个,b,c,d

) 和 这 数据 par-

ity (dqp

一个,b,c,d

) 输出, 使能 用 oe, 是 也 asynchro-

nous.

DQ

一个,b,c,d

和 dqp

一个,b,c,d

应用 至 cy7c1380bv25 和 dq

一个,b

和 dqp

一个,b

应用 至 cy7c1382bv25. 一个, b, c, d 各自 是 的 8

位 宽 在 这 情况 的 dq 和 1 位 宽 在 这 情况 的 dp.

地址 和 碎片 使能 是 注册 和 也 ad-

dress 状态 处理器 (adsp

) 或者 地址 状态 控制

(adsc

) 输入 管脚. subsequent burst 地址 能 是 inter-

nally 发生 作 控制 用 这 burst 进步 管脚 (adv).

地址, 数据 输入, 和 写 控制 是 注册 在-碎片

至 initiate 自-安排时间 写 循环. 写 循环 能 是 一个

至 四 字节 宽 作 控制 用 这 写 控制 输入.

单独的 字节 写 准许 单独的 字节 至 是 写. bw

一个

控制 dqa 和 dqpa. bwb 控制 dqb 和 dqpb. bwc

控制 dqc 和 dqpd. bw

d 控制 dqd-dqd 和 dqpd.

BW

一个, bwb bwc, 和 bwd 能 是 起作用的 仅有的 和 bwe正在

低. gw正在 低 导致 所有 字节 至 是 写. 写

通过-通过 能力 准许 写 数据 有 在 这 输出-

放 为 这 立即 next 读 循环. 这个 设备 也 在-

corporates pipelined 使能 电路 为 容易 depth expansion

没有 penalizing 系统 效能.

所有 输入 和 输出 的 这 cy7c1380bv25 和 这

cy7c1382bv25 是 电子元件工业联合会 标准 jesd8-5 兼容.

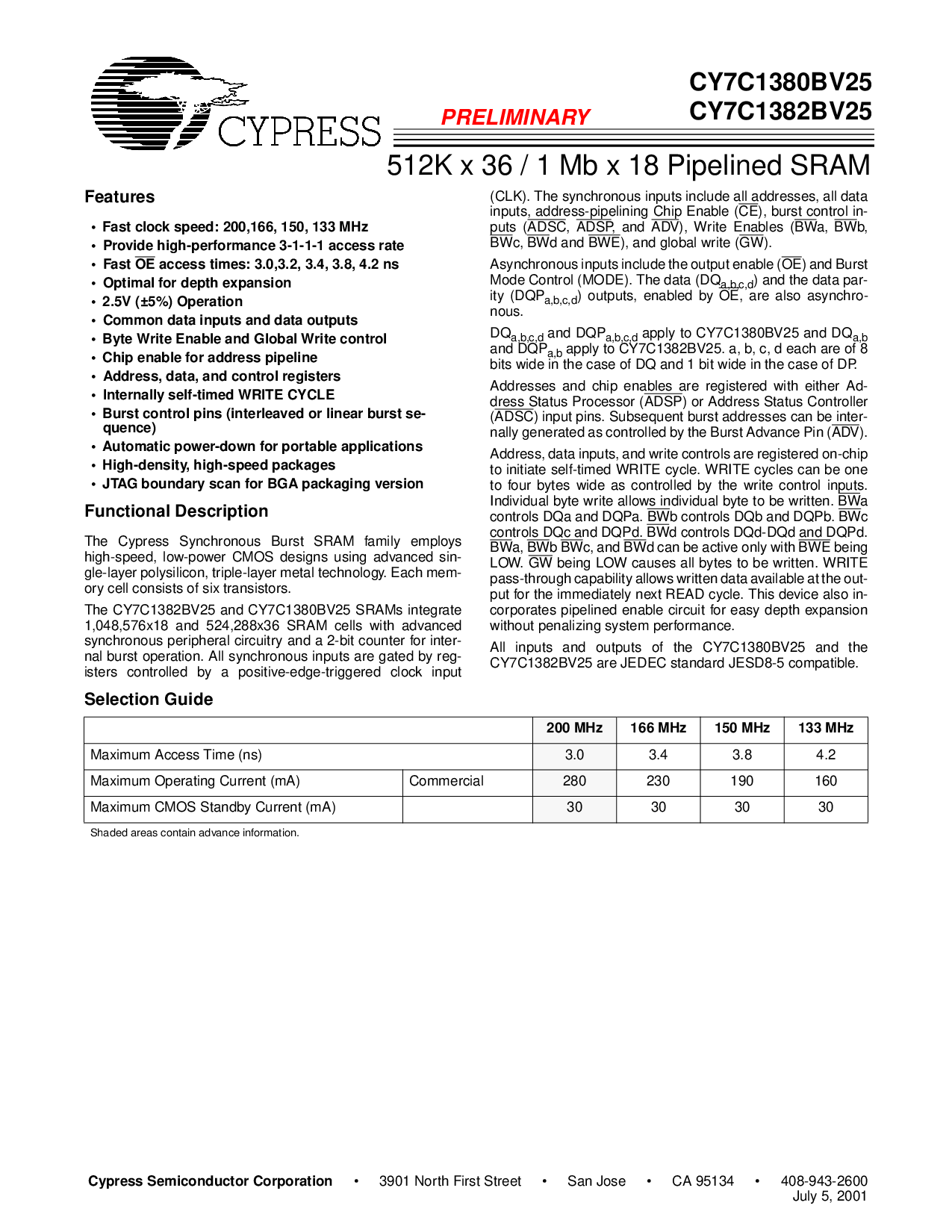

选择 手册

200 mhz 166 mhz 150 mhz 133 mhz

最大 进入 时间 (ns) 3.0 3.4 3.8 4.2

最大 运行 电流 (毫安) 商业的 280 230 190 160

最大 cmos 备用物品 电流 (毫安) 30 30 30 30

shaded areas 包含 进步 信息.