飞利浦 半导体 产品 规格

CBTD16210

20-位 水平的 shifting 总线 转变

和 10-位 输出 使能

2000 oct 12

5

交流 特性

地 = 0 v; t

r;

C

L

= 50 pf

标识

参数 描述

限制

–40

°

c 至 +85

°

c v

CC

= 5 v

±

0.5 v

单位

最小值 意思 最大值

t

pd

传播 延迟

1

250 ps

t

PZH

输出 使能 时间 至 高 水平的 1.5 5.0 7.5 ns

t

PHZ

输出 使不能运转 时间 从 高 水平的 1.0 2.5 4.5 ns

t

PZL

输出 使能 时间 至 低 水平的 1.5 6.0 9.0 ns

t

PLZ

输出 使不能运转 时间 从 低 水平的 1.5 3.5 6.0 ns

注释:

1. 这个 参数 是 warranted 但是 不 生产 测试. 这 传播 延迟 是 为基础 在 这 rc 时间 常量 的 这 典型 在-状态

阻抗 的 这 转变 和 一个 加载 电容 的 50 pf, 当 驱动 用 一个 完美的 电压 源 (零 输出 阻抗).

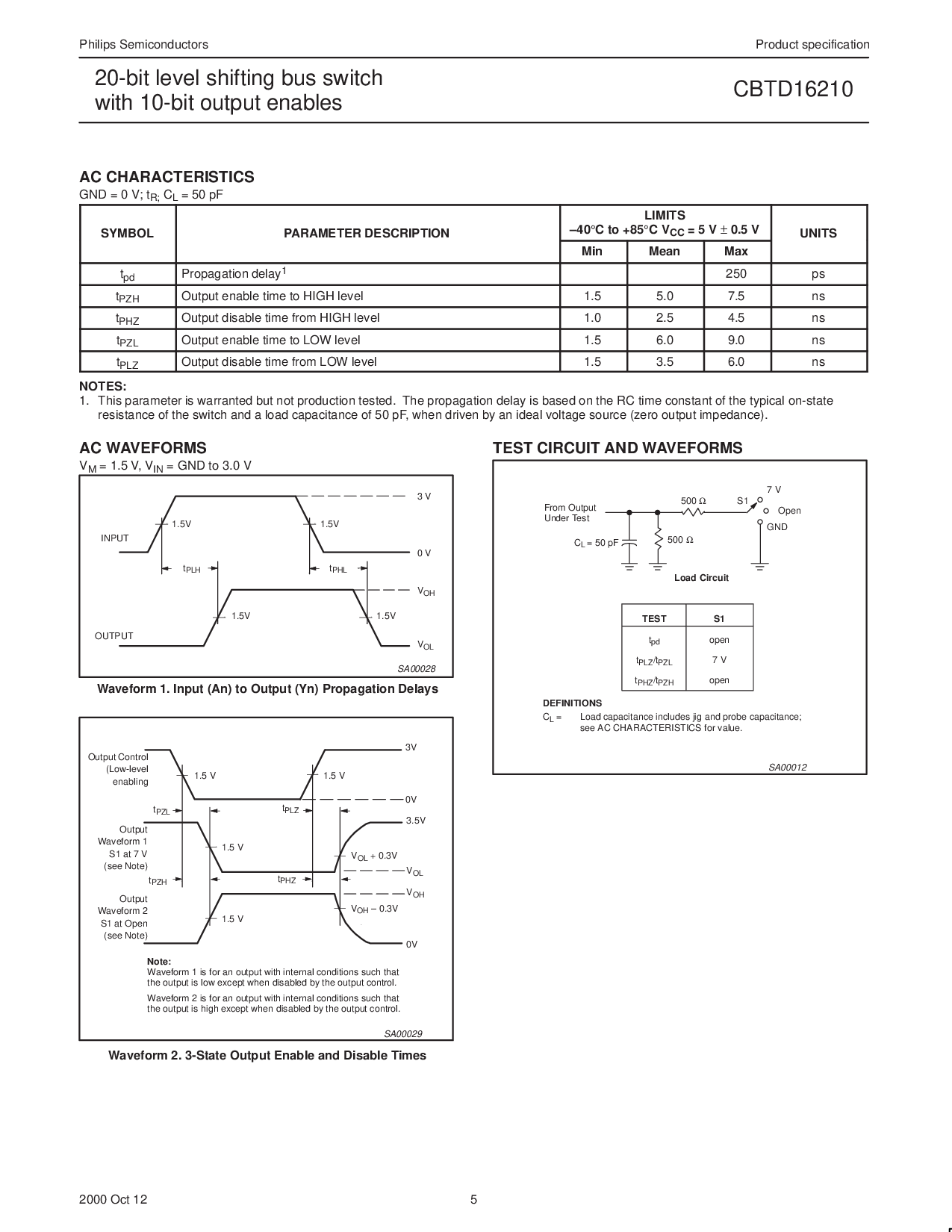

交流 波形

V

M

= 1.5 v, v

在

= 地 至 3.0 v

输入

1.5v

输出

t

PLH

t

PHL

SA00028

1.5v

1.5v 1.5v

3 v

0 v

V

OH

V

OL

波形 1. 输入 (一个) 至 输出 (yn) 传播 延迟

输出 控制

(低-水平的

enabling

1.5 v

t

PZH

t

PHZ

V

OH

V

OL

t

PZL

t

PLZ

3.5v

0V

V

OL

+ 0.3v

V

OH

– 0.3v

SA00029

1.5 v

1.5 v 1.5 v

0V

3V

输出

波形 1

s1 在 7 v

(看 便条)

便条:

波形 1 是 为 一个 输出 和 内部的 情况 此类 那

这 输出 是 低 除了 当 无能 用 这 输出 控制.

波形 2 是 为 一个 输出 和 内部的 情况 此类 那

这 输出 是 高 除了 当 无能 用 这 输出 控制.

输出

波形 2

s1 在 打开

(看 便条)

波形 2. 3-状态 输出 使能 和 使不能运转 时间

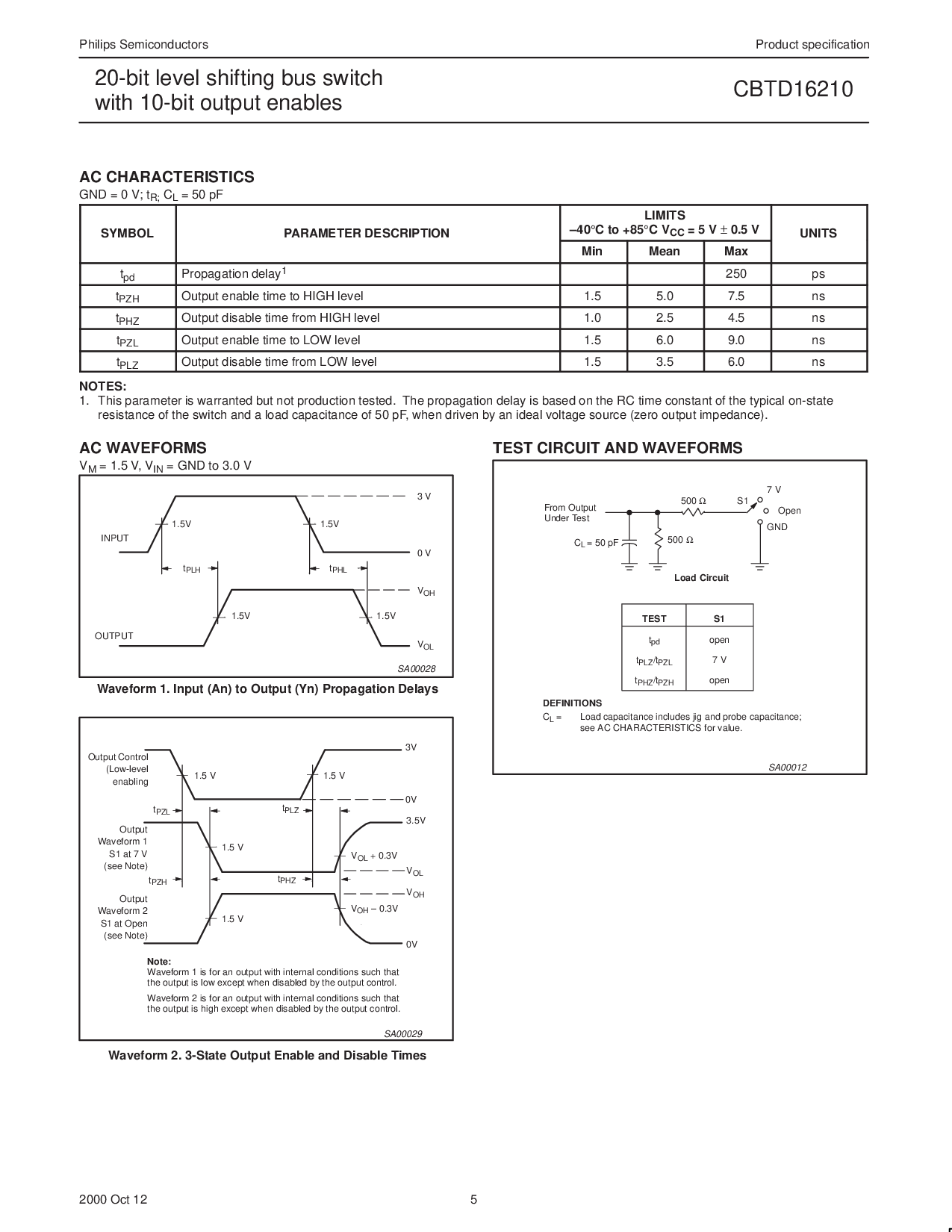

测试 电路 和 波形

C

L

= 50 pf

500

Ω

加载 电路

定义

C

L

= 加载 电容 包含 jig 和 探查 电容;

看 交流 特性 为 值.

测试 S1

t

pd

打开

t

PLZ

/t

PZL

7 v

t

PHZ

/t

PZH

打开

SA00012

500

Ω

从 输出

下面 测试

S1

7 v

打开

地