6

详细地 描述

相似物 部分

图示 2 显示 这 相等的 电路 的 这 相似物 部分

的 两个都 这 icl71c03/8052a 和 这 icl71c03/8068a 在

这 3 不同的 阶段 的 运作. 如果 这 run/支撑

管脚 是

left 打开 或者 系 至 v+, 这 系统 将 执行 conversions

在 一个 比率 决定 用 这 时钟 频率: 40,0002 在 4

1

/

2

数字 和 4002 在 3

1

/

2

数字 时钟 时期 每 循环 (看

图示 3 为 详细信息 的 转换 定时).

自动-零 阶段 I

(图示 2a)

在 这 自动-零, 这 输入 的 这 缓存区 是 连接 至

V

REF

通过 转变 2, 和 转变 3 closes 一个 循环 周围

这 积分器 和 比较器, 这 目的 的 这个 是 至

承担 这 自动-零 电容 直到 这 积分器 输出

做 不 改变 和 时间. 也, switches 1 和 2 recharge

这 涉及 电容 至 V

REF

.

输入 合并 阶段 II

(图示 2b)

在 输入 合并 这 自动-零 循环 是 opened 和 这

相似物 输入 是 连接 至 这 缓存区 输入

通过 转变 4 和 C

REF

. 如果 这 输入 信号 是 零, 这

缓存区, 积分器 和 比较器 将 看 这 一样 电压

那 existed 在 这 previous 状态 (自动-零). 因此, 这

积分器 输出 将 不 改变 但是 将 仍然是 stationary

在 这 全部 输入 合并 循环. 如果 V

在

是 不 equal 至

零, 和 不平衡 情况 exists 对照的 至 这 自动

零 阶段, 和 这 积分器 将 发生 一个 ramp 谁的

斜度 是 均衡的 至 V

在

. 在 这 终止 的 这个 阶段, 这

sign 的 这 ramp 是 latched 在 这 极性 f/f.

Deintegrate 阶段 II

(计算数量 2C 和 2d)

在 这 Deintegrate 阶段, 这 转变 驱动 逻辑 使用 这

输出 的 这 极性 f/f 在 determining whether 至 关闭

转变 6 或者 5. 如果 这 输入 信号 是 积极的, 转变 6 是 关闭

andavoltagewhichisV

REF

更多 负的 比 在

自动-零 是 impressed 在 这 缓存区 输入. 负的

输入 将 导致 +2(v

REF

) 至 是 应用 至 这 缓存区

输入 通过 转变 5. 因此, 这 涉及 电容 发生

这 相等的 的 一个 (+) 或者 (-) 涉及 从 这 单独的

涉及 电压 和 negligible 错误. 这 涉及 电压

returns 这 输出 的 这 积分器 至 这 零-越过 要点

established 在 阶段 i. 这 时间, 或者 号码 的 counts,

必需的 至 做 这个 是 均衡的 至 这 输入 电压. 自从

这 Deintegrate 阶段 能 是 两次 作 长 作 这 输入

合并 阶段, 这 输入 电压 必需的 至 给 一个 全部

规模 读 是 2V

REF

.

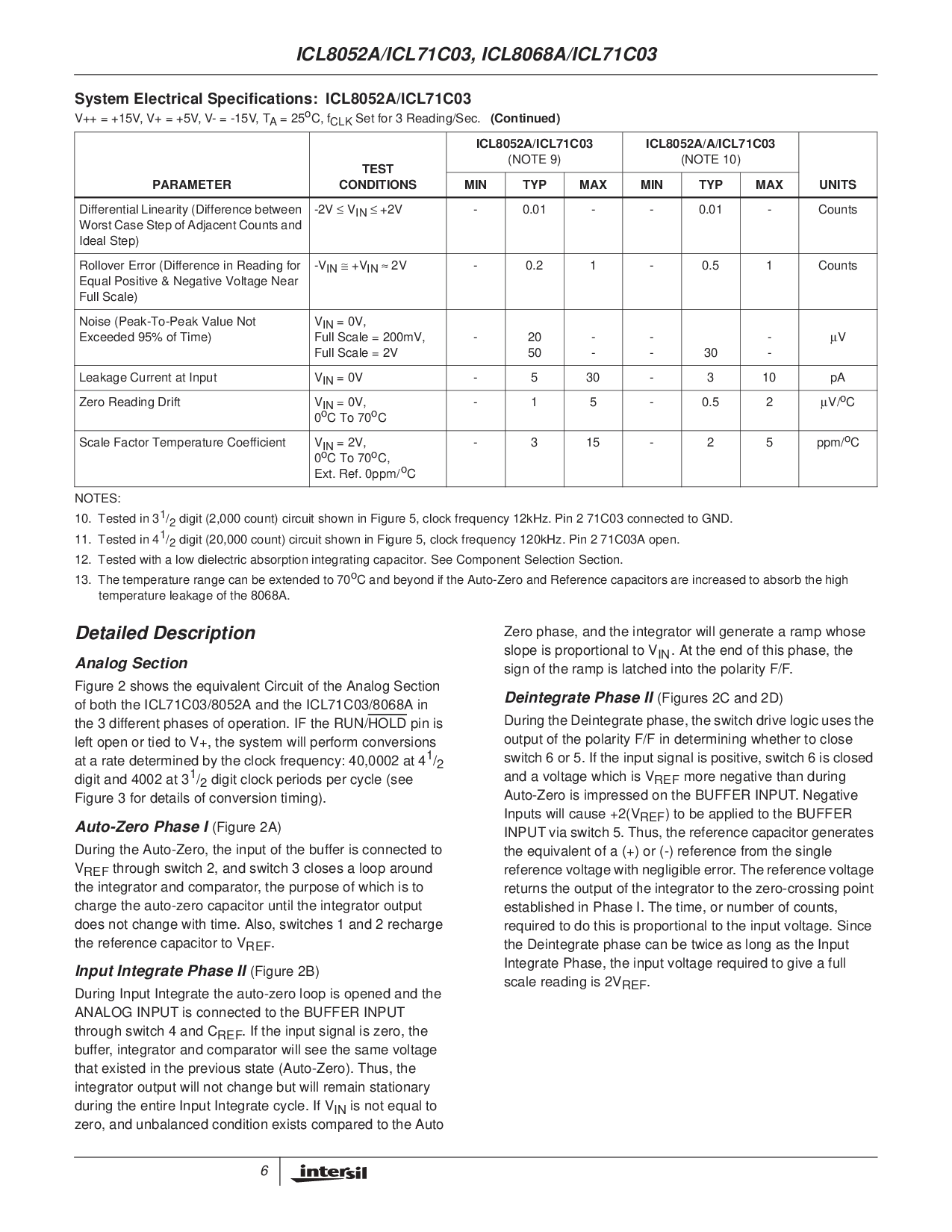

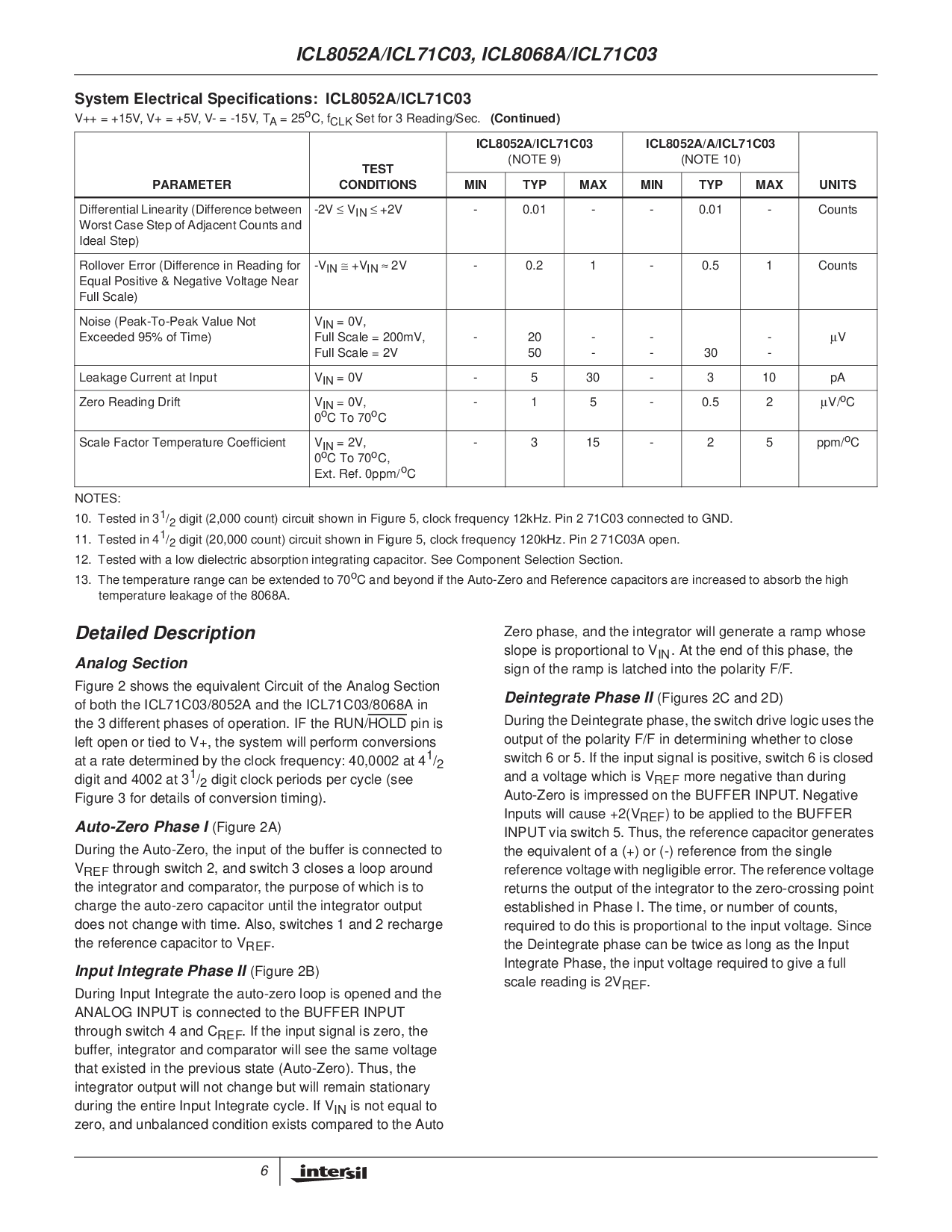

差别的 线性 (区别 在

Worst 情况 步伐 的 调整 Counts 和

完美的 步伐)

-2v

≤

V

在

≤

+2V - 0.01 - - 0.01 - Counts

Rollover 错误 (区别 在 读 为

Equal 积极的 &放大; 负的 电压 Near

全部 规模)

-v

在

≅

+V

在

≈

2V - 0.2 1 - 0.5 1 Counts

噪音 (顶峰-至-顶峰 值 不

超过 95% 的 时间)

V

在

=0v,

全部 规模 = 200mv,

全部 规模 = 2V

-20

50

-

-

-

-30

-

-

µ

V

泄漏 电流 在 输入 V

在

=0V - 530- 310 pA

零 读 逐渐变化 V

在

=0v,

0

o

CTo70

o

C

-15-0.52

µ

v/

o

C

规模 因素 温度 系数 V

在

=2v,

0

o

CTo70

o

c,

ext. ref. 0ppm/

o

C

-315-25ppm/

o

C

注释:

10. Testedin3

1

/

2

数字 (2,000 计数) 电路 显示 在 图示 5, 时钟 频率 12khz. 管脚 2 71C03 连接 至 地.

11. Testedin4

1

/

2

数字 (20,000 计数) 电路 显示 在 图示 5, 时钟 频率 120khz. 管脚 2 71C03A 打开.

12. 测试 和 一个 低 dielectric absorption integrating 电容. 看 组件 选择 部分.

13. Thetemperaturerangecanbeextendedto70

o

C 和 在之外 如果 这 自动-零 和 涉及 电容 是 增加 至 absorb 这 高

温度 泄漏 的 这 8068a.

系统 电的 规格: icl8052a/icl71c03

v++=+15v,v+=+5v,v-=-15v,t

一个

=25

o

c, f

CLK

设置 为 3 读/秒.

(持续)

参数

测试

情况

icl8052a/icl71c03

(便条 9)

icl8052a/一个/icl71c03

(便条 10)

单位最小值 典型值 最大值 最小值 典型值 最大值

icl8052a/icl71c03, icl8068a/icl71c03